在5G基站的核心芯片里,在數據中心的光模塊中,甚至在你手中的智能手機主板內,每秒鐘有超過萬億比特(Tbps)的數據以接近光的速度穿梭。這些信號的“賽道”僅有頭發絲千分之一的寬度,而它們的“賽車”卻需要以皮秒(1皮秒=1萬億分之一秒)為單位精準控制啟停。一旦信號波形出現細微畸變,輕則引發數據有誤碼,重則導致系統宕機——這就是高速信號完整性(Signal Integrity, SI)測試的終極使命:在微觀世界中守護每一次比特的完美躍遷。

高速串行信號傳輸速率越來越高,很多電子工程師在電路設計過程中,經常碰見系統不穩定、間歇性的死機、不同產品兼容性差,經常出現誤碼,這些現象多半是信號完整性惹的禍。

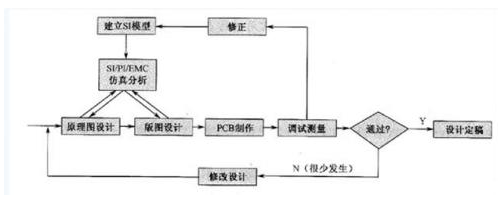

在高速數字系統(如PCIE5.0、USB4.0、DDR5、400G以太網等)中,信號完整性的好壞直接決定了整個系統的可靠性與性能上限。隨著信號速率突破數十Gbps,微小的波形畸變、時序抖動或阻抗失配都可能引發災難性錯誤。為了確保系統內模塊之間及時、準確的數據傳輸,要滿足高速傳輸的性能符合預期,信號完整性越來越重要,本文將從基礎理論出發,深入探討信號完整性的驗證和分析。

在信號完整性驗證和測試過程中,很多工程師會面臨各種各樣的問題:

抖動太大?

眼圖太差?

誤碼太多?

如何得到一個“漂亮”的眼圖結果?

抖動每次測試的結果都不一致?

如何在系統設計中改善抖動指標?

接收端抖動容限和噪聲容限怎么測試?

FFE/CTLE/DFE均衡設置和考量?

如何評估高速信號完整性?

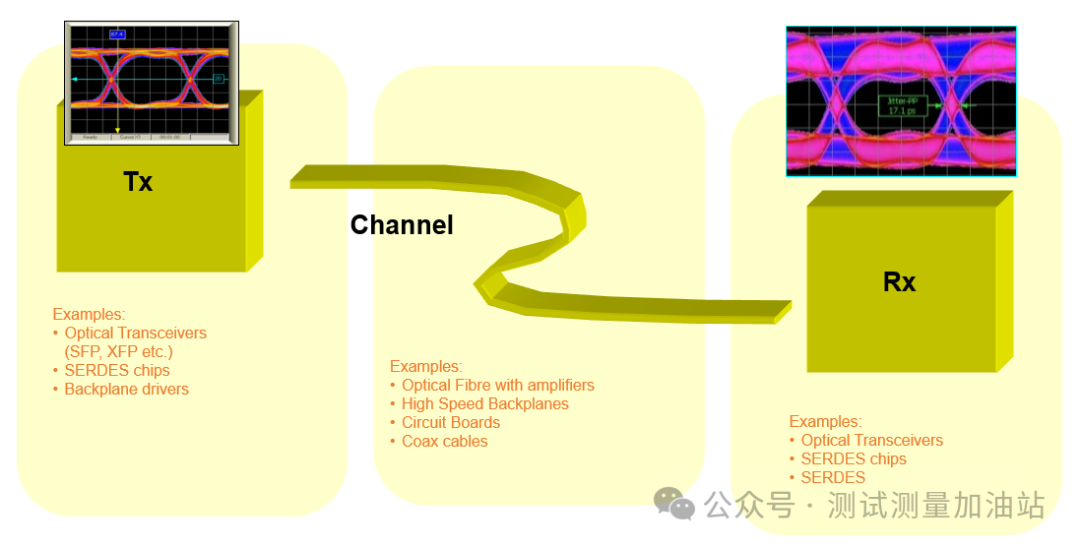

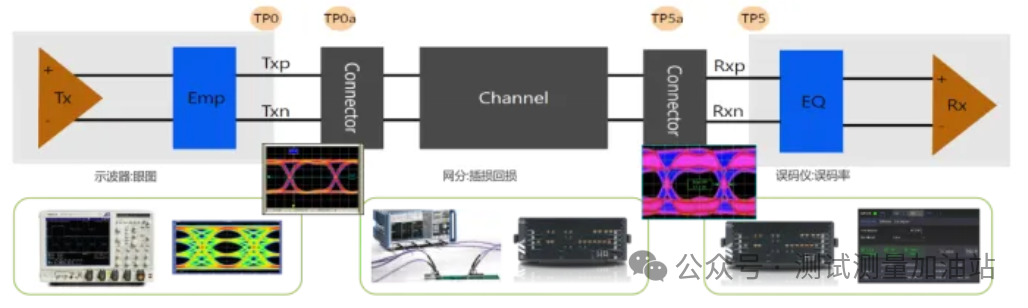

由于高速串行信號傳輸速率不斷攀升,在電路設計過程中,工程師常常遇到諸多棘手問題,諸如:系統不穩定、間歇性的死機、不同產品兼容性差以及經常出現誤碼等,而這些現象多半是信號完整性的問題。依照信號傳輸的完整流程,分別針對 TX 端(發送端)、傳輸鏈路以及 RX 端(接收端)進行測試,便能夠精準地定位問題根源,從而為后續的優化改進工作提供有力依據,確保高速傳輸系統的高效穩定運行。

在高速信號傳輸鏈路中互連鏈路上任何一個環節的故障可能影響整個系統工作的效率以及穩定性,對于測試人員需要花費更多的成本去發現問題、定位問題、分析問題、解決問題。新標準逐漸從單一互連簡單要求的基礎上,額外增加協同整體要求。整個高速鏈路性能的評估,包括Tx發送端,傳輸鏈路,以及Rx接收端三大部分組成,發送、接收、電纜或者背板需要放在一個互連鏈路中評估。評估時按照時域、頻域和其他進行不同儀表的選取。

信號完整性測試核心儀器

實時示波器(RT Scope):利用高性能實時示波器和軟件完成Tx發送端信號的抖動(Jitter)和眼圖(Eye Diagram)以及一致性測試測試。

誤碼率測試儀(BERT):利用誤碼儀的PPG創建壓力眼(Stressed Eye)信號模擬極端環境,驗證其接收端RX容限能力。

矢量網絡分析儀(VNA):

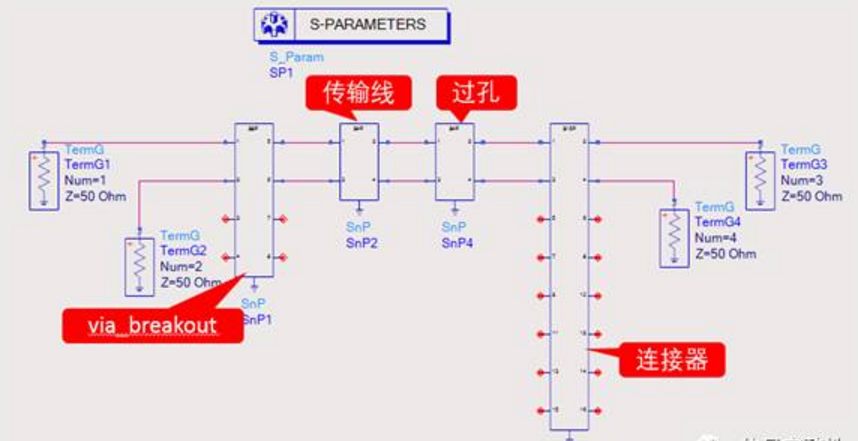

信號在傳輸過程中,對不同速率其損耗不同,反射和串擾都可以導致信號的波形發生失真,導致眼圖閉合。使用矢量網絡分析儀(VNA)測量夾具和傳輸鏈路的 S 參數;利用TDR或VNA進行阻抗測試以及通過時域反射計(TDR)驗證差分對的對稱性,控制 Intra-pair Skew。

Tx發送端信號質量的評估

在高速數字系統中,信號完整性(Signal Integrity, SI)是確保信號從發送端(Tx)到接收端(Rx)全程保持準確時序、幅度和形狀的核心指標。隨著數據速率從 1.25Gbps 躍升至 800Gbps 甚至更高,TX 發送端的信號質量直接影響整個系統的誤碼率、功耗以及穩定性。

TX 發送端的核心挑戰(信號完整性的“三大殺手”):

高頻衰減:信號的高頻分量在傳輸鏈路中易受趨膚效應和介質損耗影響,導致眼圖閉合。

反射與串擾:阻抗不連續和相鄰信號線的電磁耦合會引發波形畸變。

抖動控制:總體抖動TJ,可能超出接收端容限。

TX 發送端信號質量的評估指標

1.波形完整性

波形完整性是衡量信號在傳輸過程中是否畸變的關鍵指標,主要包括以下參數:

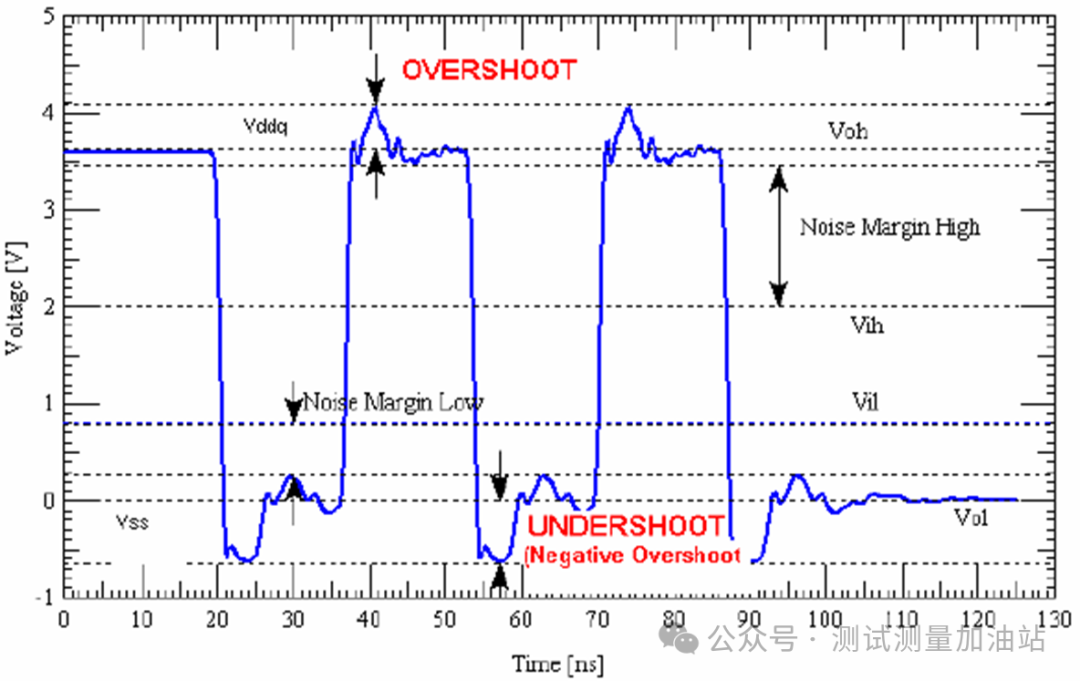

過沖(Overshoot)與下沖(Undershoot):由阻抗不匹配或反射、或者電源噪聲引起,可能損壞器件或導致邏輯誤判。例如,過沖超過器件耐壓閾值時,可能觸發保護電路動作。

振鈴(Ringing): 傳輸線中的電感、電容諧振效應導致信號在跳變后振蕩,需通過優化終端匹配電阻或調整信號上升時間抑制。

單調性(Monotonicity):信號上升沿/下降沿需保持單一方向變化,避免影響時序判斷。

衰減(Attenuation):高頻信號因趨膚效應和介質損耗導致的幅度下降,可通過預加重(Pre-emphasis)或去加重(De-emphasis)技術補償。

2.時序完整性

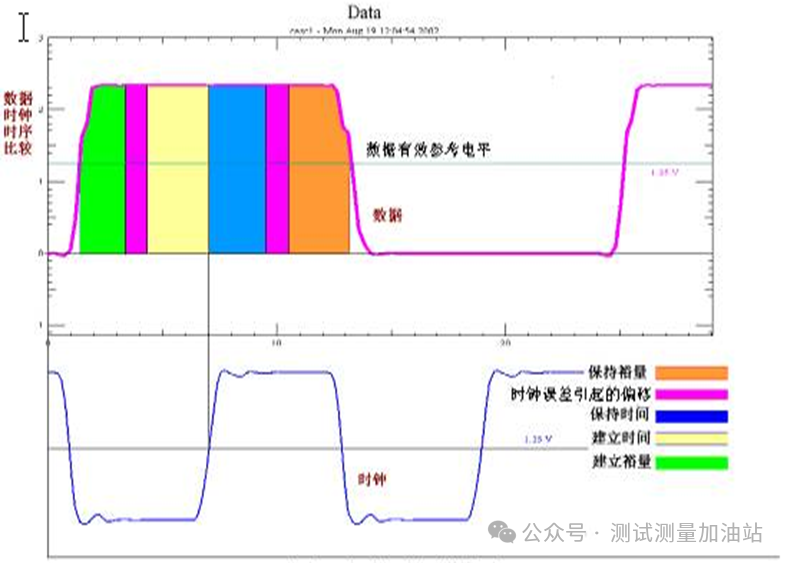

建立時間(Setup Time)與保持時間(Hold Time):信號在時鐘邊沿前后需穩定保持的最小時間窗口,違反會導致數據采樣錯誤。

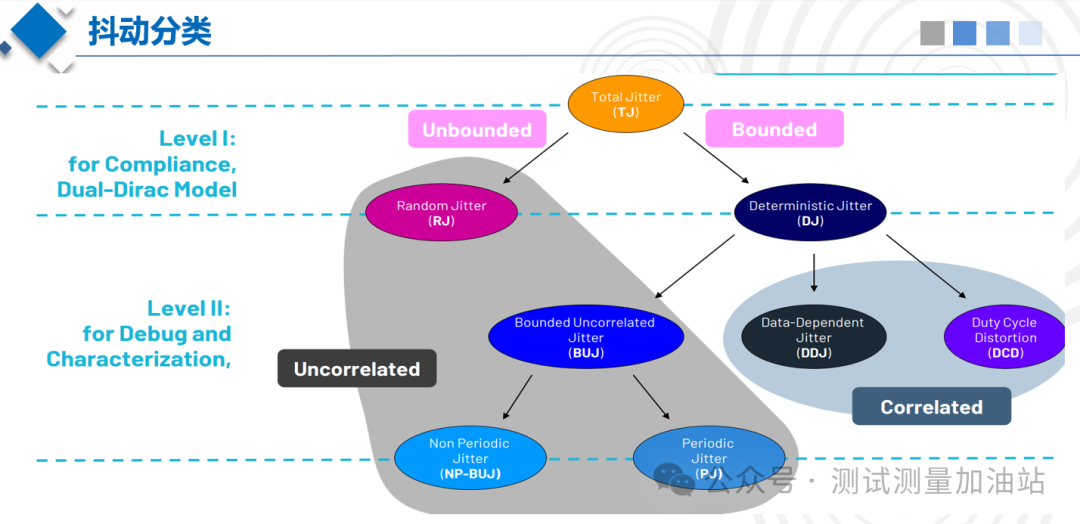

時序抖動(Timing Jitter):總體抖動(TJ)為隨機抖動(RJ)和確定性抖動(DJ)。

確定性抖動(DJ):DJ 包括周期性抖動(PJ)、碼間干擾(ISI),占空比失真(DCD)。

隨機抖動(RJ):RJ 服從高斯分布且無界,需通過低噪聲電源設計和屏蔽措施抑制。

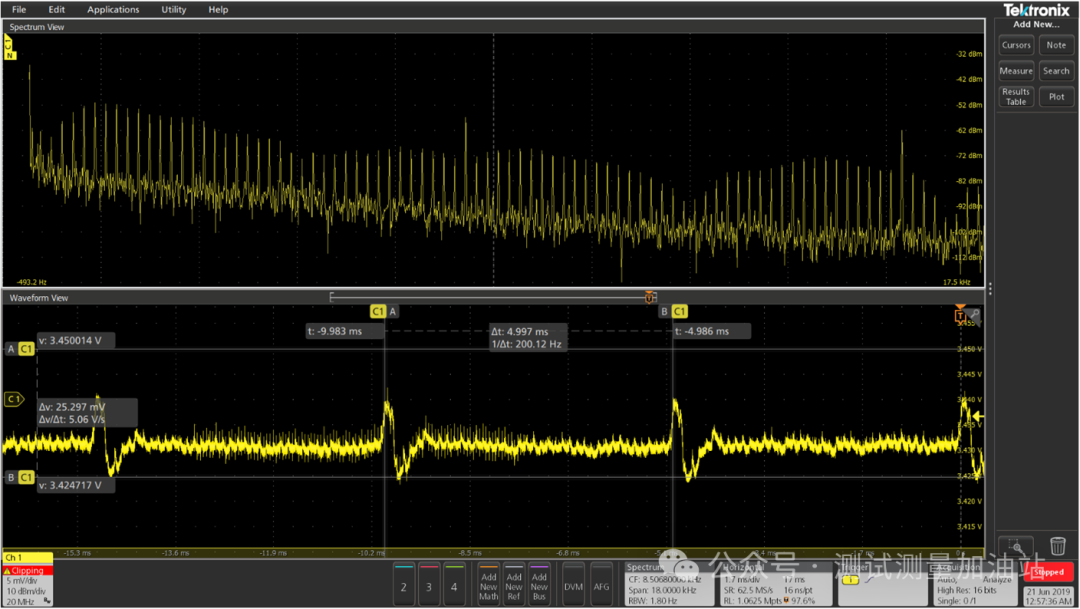

3.電源完整性(PI)

PI 與 SI 緊密相連,電源噪聲會直接耦合到信號路徑。電源噪聲是導致信號質量惡化的主要因素之一。電源完整性測試包括:

紋波與噪聲:紋波一般控制在 5% 以內,過高的噪聲會導致信號幅度波動和抖動增加,使用高帶寬示波器測量電源軌的峰峰值噪聲(通常需小于 50mVpp)。

同步開關噪聲(SSN):多路信號同時切換時,地彈和電源反彈會引入共模干擾,需通過去耦電容和低阻抗電源平面設計緩解。

4.抖動與眼圖分析

抖動是高速信號中最難控制的參數之一。

抖動總抖動(TJ)= 隨機抖動(RJ) + 確定性抖動(DJ):TJ 需要滿足協議規定的容限。

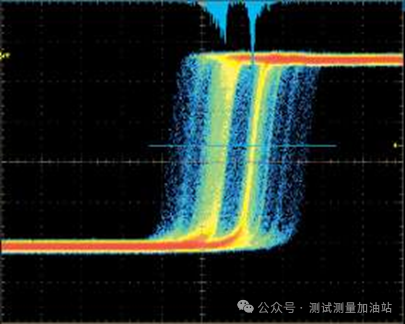

眼圖測試:通過疊加多比特周期形成,直觀反映信號幅度、抖動和噪聲,眼高(Eye Height)和眼寬(Eye Width)是判斷信號質量的黃金標準。

眼圖模板測試:

將實際眼圖與協議標準模板(如 USB4 或 PCIe 的眼高/眼寬要求)對比,快速判斷 Pass/Fail。

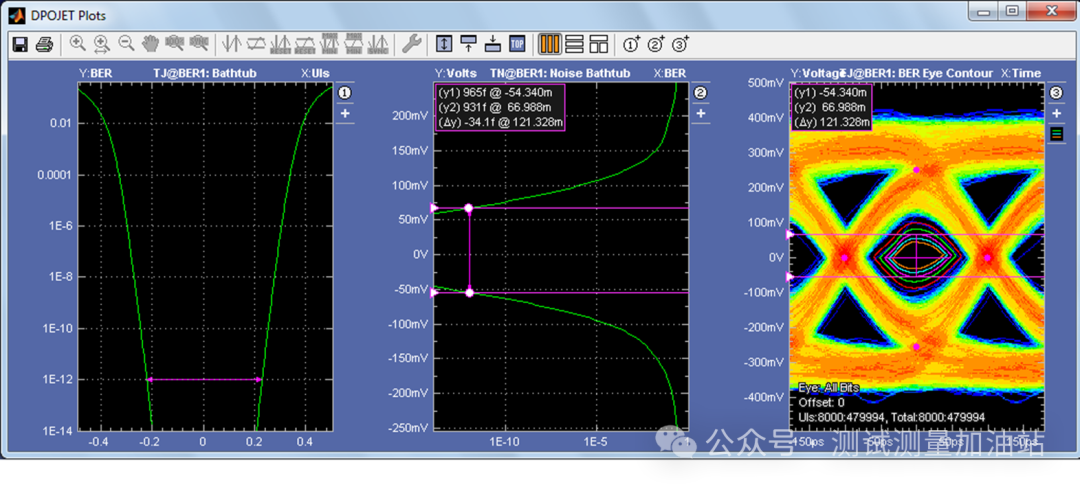

抖動分解:通過 TIE(Time Interval Error)分析,分離 RJ 和 DJ 成分。例如,泰克實時示波器的DPOJET抖動分析軟件可自動生成雙狄拉克模型,預測總抖動(TJ)。

Rx接收端測試

Rx接收端測試

一、為什么要做Rx接收端測試?——高速信號的“最后一公里”挑戰在高速數字系統中,接收端(Rx)是信號傳輸鏈路的最終環節,也是信號完整性問題爆發的“重災區”。隨著以太網速率從10G邁向800G甚至1.6T,USB4.0和PCIE6.0的速率突破64Gbps,高速信號在傳輸過程中面臨損耗、反射、串擾等問題的多重夾擊。即使發送端(Tx)和傳輸鏈路的設計近乎完美,接收端的微小偏差也可能導致系統誤碼率飆升,甚至完全失效。

有趣的是,接收端的測試難點在于其“黑盒性”:芯片內部的均衡電路(如CTLE、DFE)、時鐘恢復模塊(CDR)等復雜結構無法直接觀測,只能通過注入壓力信號模擬極端環境,驗證其容限能力。因此,抖動容限測試(JTOL)成為評估接收端Rx性能的“黃金標準”。

二、抖動容限測試的核心原理:如何“折磨”接收端?

1. 壓力眼圖:模擬真實世界的“最差情況”

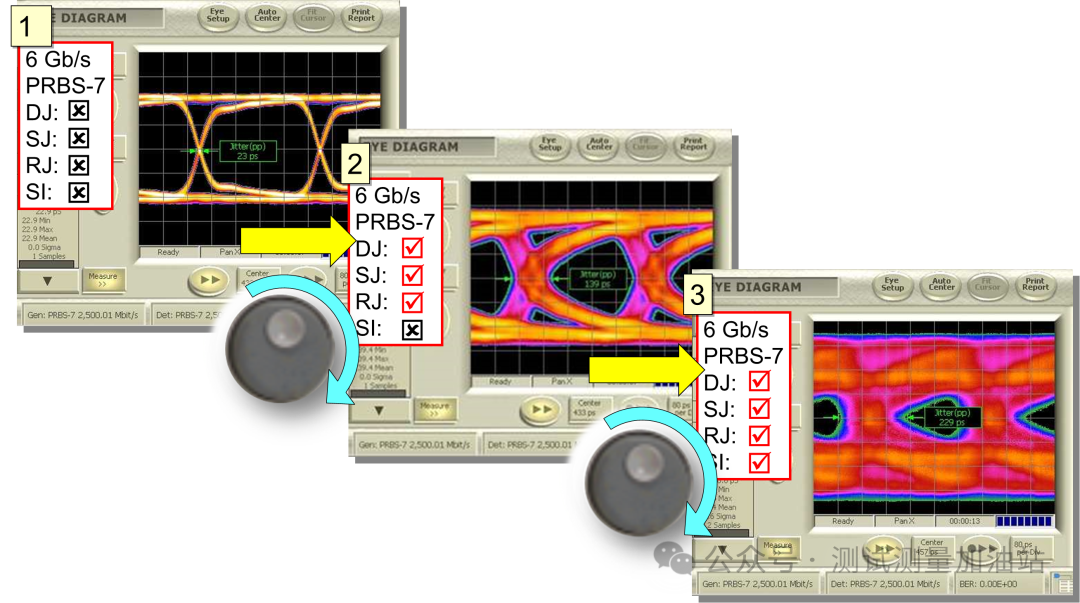

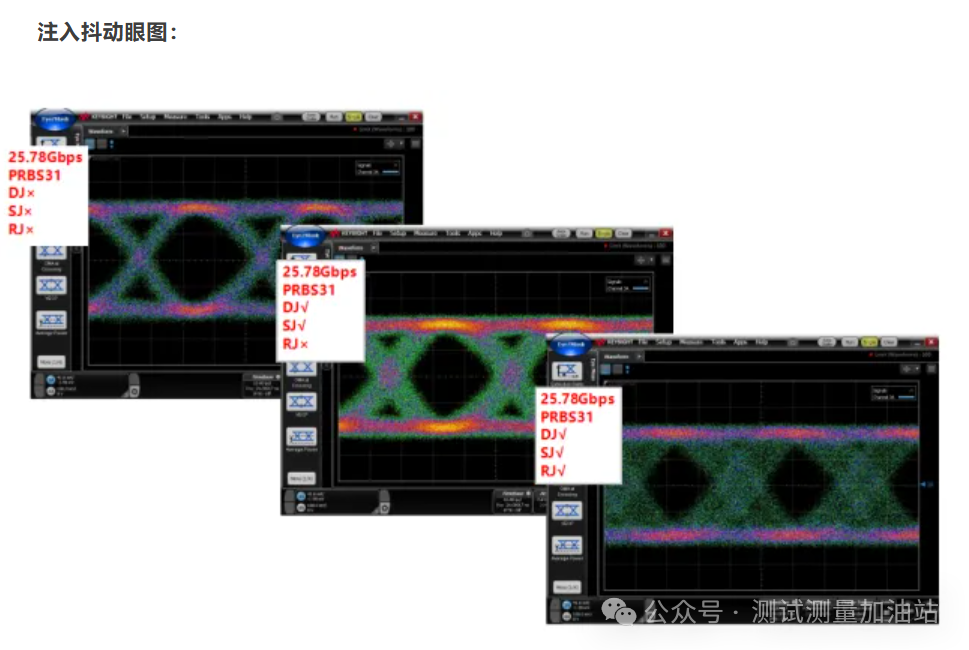

抖動容限測試的核心是生成“壓力眼圖”(Stressed Eye),即在信號中注入特定類型的抖動和噪聲,模擬傳輸鏈路中最惡劣的環境。例如:

隨機抖動(RJ):源于熱噪聲等不可預測因素,呈高斯分布,無界特性使其成為“長期誤碼殺手。

確定性抖動(DJ):包括周期性抖動(PJ)、碼間干擾(ISI)等,與電路設計缺陷直接相關,可通過均衡技術部分補償。

串擾噪聲(BUJ):相鄰通道的干擾,尤其是高頻信號下,近端和遠端串擾可能疊加形成“噪聲風暴”。

2. 測試流程:從校準到判據

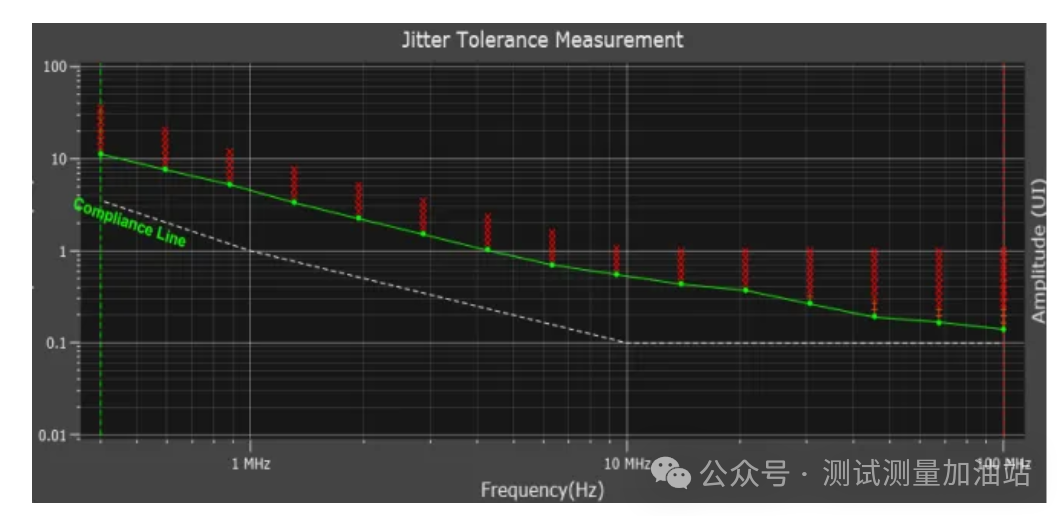

通過高性能誤碼儀注入這些抖動,逐步增加壓力,直到接收端誤碼率閾值,即可確定其抖動容限邊界。

使用高性能誤碼儀產生一個劣化(注入抖動)的眼圖信號,俗稱壓力眼信號。壓力眼信號的參數有明確規定,,在不同的規范中具體指標會有不同。通過校準后的壓力眼會輸入被測接收機進行抖動容限測試。中星聯華SL3000B系列高性能誤碼儀可提供PJ、RJ、BUJ等抖動注入,可以為RX JTOL測試提供強力支持。

測試流程:

產生規范要求的抖動分量,在不同的頻點上分別產生相應的抖動量;

將stressed信號注入DUT Rx;

統計DUT Tx端發出的信號的誤碼率是否達到要求。

目前,中星聯華的高性能誤碼儀是國內首個支持注入抖動和加噪聲創建壓力信號的高性能誤碼儀,也是目前國內首款能夠滿足接收端抖動容限JTOL和噪聲容限ITOL測試的誤碼儀。其中可支持的注入抖動類型有低頻正弦抖動、高頻周期抖動、BUJ串擾抖動、RJ隨機抖動以及SSC擴頻時鐘等;支持的噪聲類型有CMI和DMI和BBN寬帶白噪聲,有效地解決“卡脖子”的難題。

高速信號完整性測試總結高速信號完整性驗證和測試是高速系統設計的“守門人”,TX 發送端信號質量評估是需綜合波形、時序、電源和抖動眼圖等多維度參數。RX接收端抖動容限測試不僅是技術驗證,更是對系統魯棒性的終極考驗。從壓力眼生成到誤碼統計,每一步都需兼顧精度與效率。利用強大的測試工具——高性能誤碼分析儀,工程師得以在實驗室中“預見”真實世界的信號”最差環境“,從而設計出真正可靠的高速系統。正如一位資深工程師所言:“好的接收端RX測試,就像給信號穿上防彈衣——它可能不會讓系統跑得更快,但一定能讓它活得更久。隨著速率提升和協議復雜化,測試技術正向智能化、高集成度方向發展。工程師需緊跟技術演進,結合仿真與實測,確保信號從發送端到接收端的全程完整性。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

電路設計

+關注

關注

6701文章

2531瀏覽量

213738 -

信號完整性

+關注

關注

68文章

1438瀏覽量

96536 -

高速信號

+關注

關注

1文章

243瀏覽量

18011

發布評論請先 登錄

相關推薦

熱點推薦

高速電路信號完整性設計培訓

高速IC(芯片)、PCB(電路印制板)和系統的核心技術就是微波背景下的互連設計與信號完整性分析。全世界高速高密度電路的發展表明:互連正在取代器件,躍升為

發表于 04-21 17:11

信號與電源完整性分析和設計培訓

印制板)和系統的核心技術就是微波背景下的互連設計與信號完整性分析。全世界高速高密度電路的發展表明:互連正在取代器件,躍升為高速電路設計的主角。信號

發表于 05-29 13:29

高速電路信號完整性分析與設計—高速信號完整性的基本理論

2.1 基本電磁理論 本書主要討論高速數字電路中信號完整性分析與高速電路設計的基本方法,而信號完整性

發表于 05-25 16:21

?1838次閱讀

基于信號完整性的高速PCB設計流程解析

(1)因為整個設計流程是基于信號完整性分析的,所以在進行PCB設計之前,必須建立或獲取高速數字信號傳輸系統各個環節的信號

發表于 10-11 14:52

?2330次閱讀

ADS在信號完整性和電源完整性仿真方面的應用

的工藝發展使得集成度越來越高,導致芯片上電流密度急速增加,使信號完整性的問題更加嚴重。因此非常有必要從整個系統設計開始就考慮信號完整性與電源完整性

聽懂什么是信號完整性

2024年12月20日14:00-16:00中星聯華科技將舉辦“高速信號完整性分析與測試”-“碼”上行動系列線上講堂線上講堂。本期會議我們將為大家介紹高速串行總線傳輸基本框架,什么是

皮秒級暗戰:深度解析高速信號完整性的“隱形殺手”!

皮秒級暗戰:深度解析高速信號完整性的“隱形殺手”!

評論