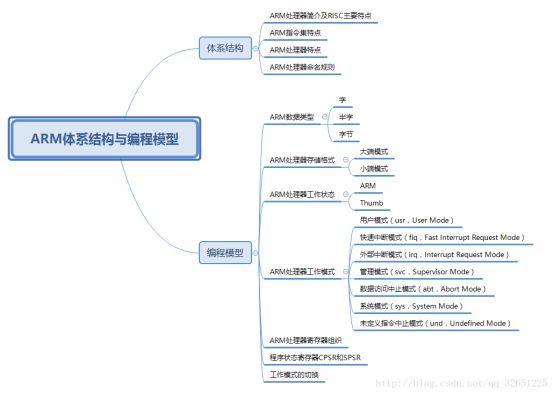

ARM處理器簡介

ARM(Advanced RISC Machines)是一個32位RISC(精簡指令集)處理器架構,ARM處理器則是ARM架構下的微處理器。ARM處理器廣泛的使用在許多嵌入式系統。ARM處理器的特點有指令長度固定,執行效率高,低成本等。

RISC設計主要特點

1、指令集——RISC減少了指令集的種類,通常一個周期一條指令,采用固定長度的指令格式,編譯器或程序員通過幾條指令完成一個復雜的操作。而CISC指令集的指令長度通常不固定。

2、流水線——RISC采用單周期指令,且指令長度固定,便于流水線操作執行。

3、寄存器——RISC的處理器擁有更多的通用寄存器,寄存器操作較多。例如ARM處理器具有37個寄存器。

4、Load/Store結構——使用加載/存儲指令批量從內存中讀寫數據,提高數據的傳輸效率。

5、尋址方式簡化,指令長度固定,指令格式和尋址方式種類減少。

二、ARM指令集特點

ARM處理器是基于RISC的,但不是純粹的RISC體系結構。為了使ARM處理器能夠更好的滿足嵌入式系統的需要,ARM指令集和單純的RISC指令集有以下幾點不同:

1、一些特定的指令周期數可變。例如多寄存器裝載或存儲的Load/Store指令執行周期就是不確定的,這個會根據相關的寄存器個數而定。如果是訪問連續的內存地址,就可以改善性能,因為連續的內存訪問比隨機訪問要快。根據這個特點,由于在函數的起始和結尾通常會有多個寄存器與內存進行數據交換的操作,因此相應操作的指令條數會減少,提高了代碼的密度。

2、內嵌的桶形移位寄存器產生了更復雜的指令。桶形移位寄存器是一個硬件部件,在一個寄存器被一條指令使用之前,桶形移位寄存器可以處理這個寄存器中的數據。桶形移位寄存器擴展了許多指令的功能,以此改善內核的性能,提高代碼密度。

3、Thumb16位指令集。ARM處理器有兩種工作狀態,一種是ARM狀態,一種是Thumb狀態。ARM狀態下指令長度為32位,Thumb狀態下指令長度為16位。這種特點使得ARM既能執行16位指令,又能執行32位指令,從而增強了ARM內核的功能。

4、條件執行。只有當某個特定條件滿足時指令才會被執行。這個特性可以減少分支指令的數目,從而改善性能,提高代碼密度。

5、增強指令。一些功能強大的數字信號處理器(DSP)指令被加入到標準的ARM指令中,以支持快速的16*16乘法操作及飽和運算。ARM的這些增強指令,使得ARM處理器不需要加上DSP即可實現。

三、ARM處理器特點

1、ARM指令都是32位定長的

2、寄存器數量豐富(37個寄存器)

3、普通的Load/Store指令

4、多寄存器的Load/Store指令

5、指令的條件執行

6、單時鐘周期中的單條指令完成數據移位操作和ALU操作

7、通過變種和協處理器來擴展ARM處理器的功能

8、擴展了16位的Thumb指令來提高代碼密度

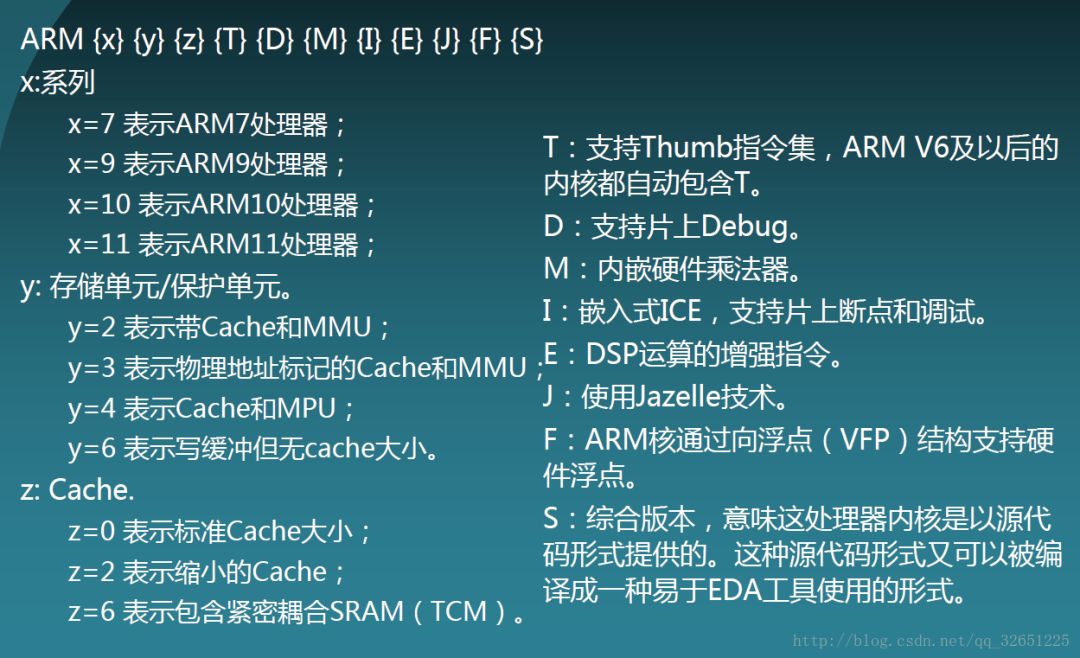

四、ARM處理器命名規則

ARM編程模型

一、ARM數據類型

1、字(Word):在ARM體系結構中,字的長度為32位。

2、半字(Half-Word):在ARM體系結構中,半字的長度為16位。

3、字節(Byte):在ARM體系結構中,字節的長度為8位。

二、ARM處理器存儲格式

ARM體系結構將存儲器看作是從0地址開始的字節的線性組合。作為32位的微處理器,ARM體系結構所支持的最大尋址空間為4GB。

ARM體系結構可以用兩種方法存儲字數據,分別為大端模式和小端模式。

大端模式(高地高低):字的高字節存儲在低地址字節單元中,字的低字節存儲在高地址字節單元中。

小端模式(高高低低):字的高字節存儲在高地址字節單元中,字的低字節存儲在低地址字節單元中。

三、ARM處理器工作狀態

從編程的角度來看,ARM微處理器的工作狀態一般ARM和Thumb有兩種,并可在兩種狀態之間切換。

1、ARM狀態:此時處理器執行32位的字對齊ARM指令,絕大部分工作在此狀態。

2、Thumb狀態:此時處理器執行16位的半字對齊的Thumb指令。

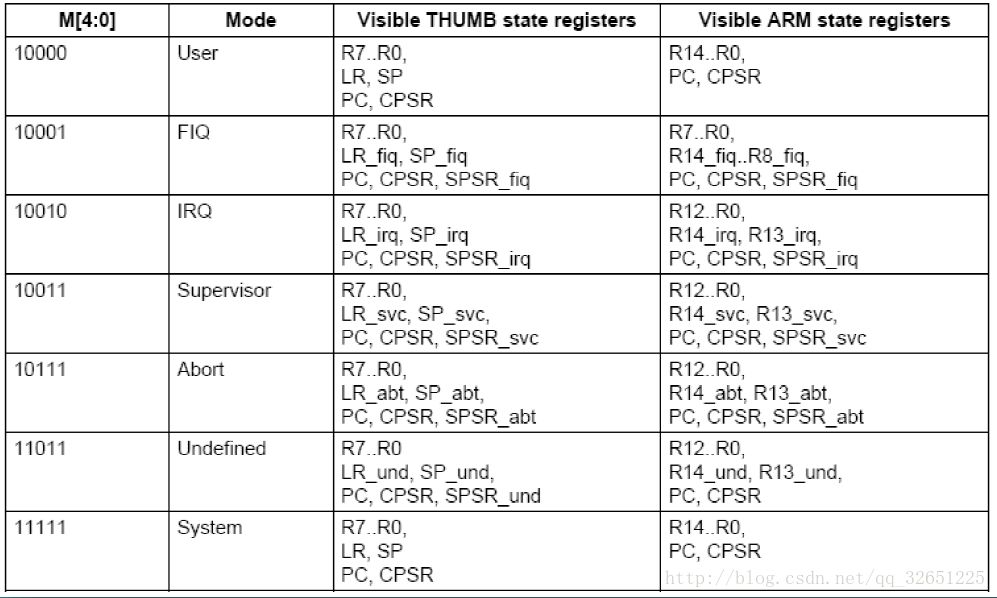

四、ARM處理器工作模式

1、用戶模式(usr,User Mode):ARM處理器正常的程序執行狀態。

2、快速中斷模式(fiq,Fast Interrupt Request Mode):用于高速數據傳輸或通道處理。當觸發快速中斷時進入此模式。

3、外部中斷模式(irq,Interrupt Request Mode):用于通用的中斷處理。當觸發外部中斷時進入此模式。

4、管理模式(svc,Supervisor Mode):操作系統使用的保護模式。在系統復位或執行軟件中斷指令SWI時進入。

5、數據訪問中止模式(abt,Abort Mode):當數據或指令預取中止時進入該模式,可用于虛擬存儲及存儲保護。

6、系統模式(sys,System Mode):運行具有特權的操作系統任務。

7、未定義指令中止模式(und,Undefined Mode):當未定義的指令執行時進入該模式,可用于支持硬件協處理器的軟件仿真。

除了用戶模式之外,其余六種模式都是特權模式。除了用戶模式和系統模式之外,其余五種模式都是異常模式。

在特權模式下程序可以訪問所有的系統資源。非特權模式和特權模式之間的區別在于有些操作只能在特權模式下才被允許,例如直接改變模式和中斷使能等。而且為了保證數據安全,一般MMU會對地址空間進行劃分,只有特權模式才能訪問所有的地址空間。而用戶模式如果需要訪問硬件,必須切換到特權模式下,才允許訪問硬件。

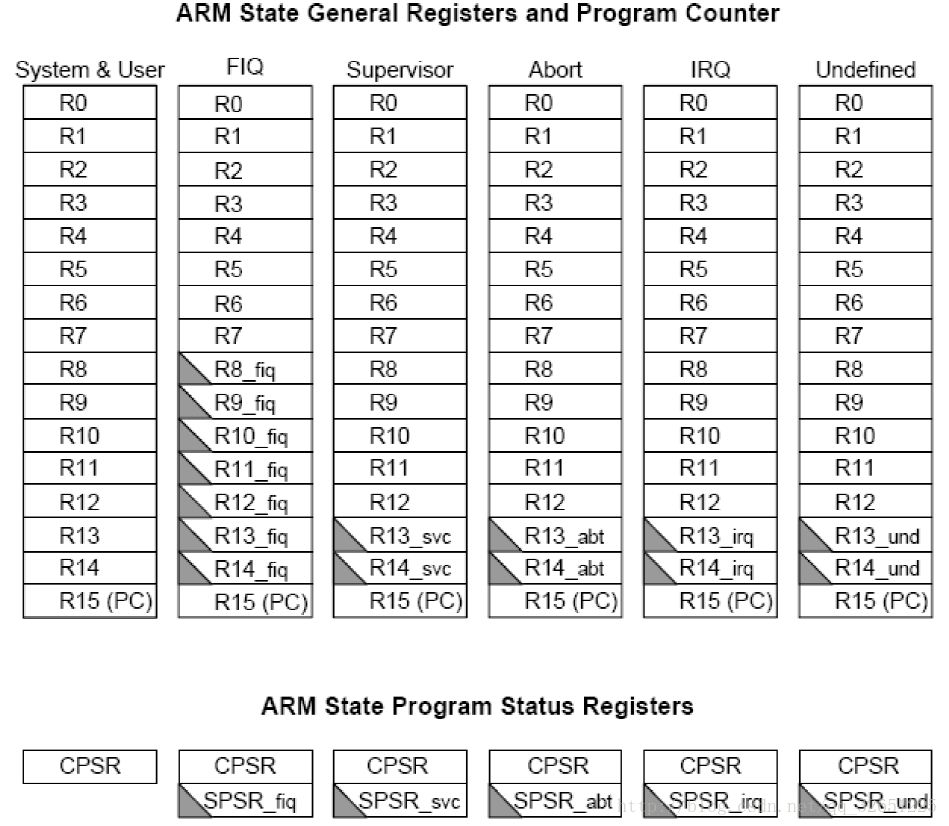

五、ARM處理器寄存器組織

ARM共有37個32位寄存器,其中31個為通用寄存器,6個為狀態寄存器,包括R0-R15,R8_fiq-R14_fiq,R13_svc,R14_svc,R13_abt,R14_abt,R13_irq,R14_irq,R13_und,R14_und,CPSR,SPSR_fiq,SPSR_svc,SPSR_abt,SPSR_irq,SPSR_und。如圖。

通用寄存器包括R0-R15,可以分為3類:

1、未分組寄存器R0-R7

在所有運行模式下,未分組寄存器都指向同一個物理寄存器,他們未被系統用作特殊的用途。因此在中斷或異常處理進行異常模式轉換時,由于不同的處理器運行模式均使用相同的物理寄存器,所以可能造成寄存器中數據的破壞。

2、分組寄存器R8-R14

對于分組寄存器,他們每次所訪問的物理寄存器都與當前的處理器運行模式相關。具體如上圖。

R13常用作存放堆棧指針,用戶也可以使用其他寄存器存放堆棧指針,但在Thumb指令集下,某些指令強制要求使用R13存放堆棧指針。

R14稱為鏈接寄存器(LR,Link Register),當執行子程序時,R14可得到R15(PC)的備份,執行完子程序后,又將R14的值復制回PC,即使用R14保存返回地址。

3、程序計數器PC(R15)

寄存器R15用作程序計數器(PC),在ARM狀態下,位[1:0]為0,位[31:2]用于保存PC;在Thumb狀態下,位[0]為0,位[31:1]用于保存PC。

由于ARM體系結構采用了多級流水線技術,對于ARM指令集而言,PC總是指向當前指令的下兩條指令的地址,即PC的值為當前指令的地址值加8個字節。

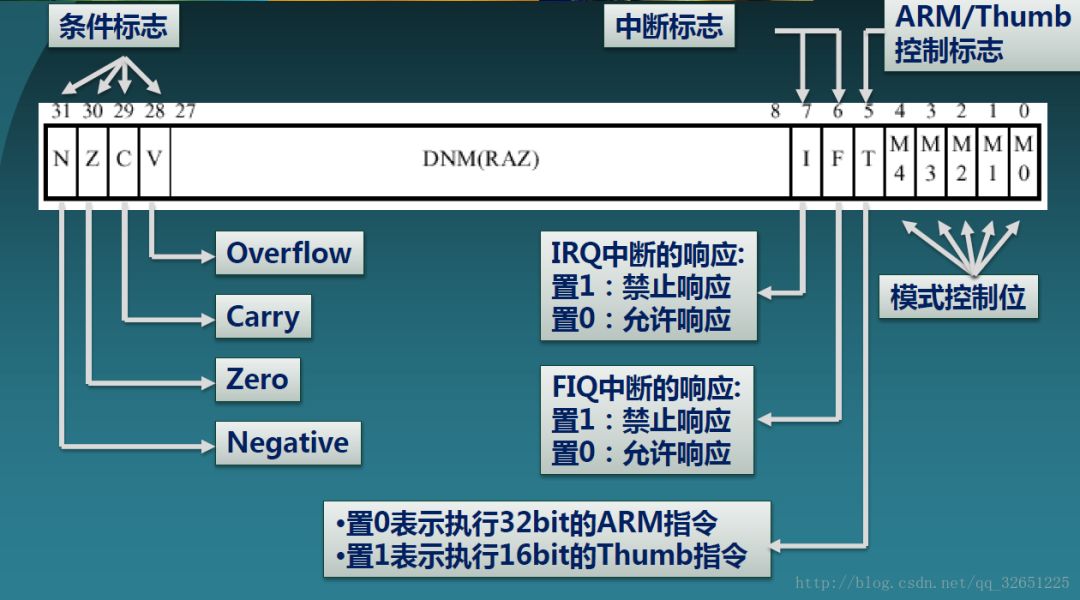

六、程序狀態寄存器CPSR和SPSR

CPSR(Current Program Status Register,當前程序狀態寄存器),CPSR可在任何運行模式下被訪問,它包括條件標志位、中斷禁止位、當前處理器模式標志位以及其他一些相關的控制和狀態位。

每一種運行模式下都有一個專用的物理狀態寄存器,稱為SPSR(Saved Program Status Register,備份的程序狀態寄存器),當異常發生時,SPSR用于保存當前CPSR的值,從異常退出時則可由SPSR來恢復CPSR。

由于用戶模式和系統模式不屬于異常模式,這兩種狀態下沒有SPSR,因此在這兩種狀態下訪問SPSR,結果是未知的。

CPSR保存數據的結構:

1、N(Negative):當用兩個補碼表示的帶符號數進行運算時,N=1表示結果為負,N=0表示結果為正數或零

2、Z(Zero):Z=1表示運算結果為0,Z=0表示運算結果非零

3、C(Carry):有4種方法可以設置C的值:

(1)加法指令(包括比較指令CMP)

(2)當運算產生進位時(無符號數溢出),C=1,否則C=0

(3)減法運算(包括比較指令CMP)

(4)當運算產生了借位(無符號數溢出),C=0,否則C=1

對于包含移位操作的非加/減運算指令,C為移出值的最后一位。對于其他的非加/減運算指令,C的值通常不變。

4、V(Overflow):有2種方法設置V的值:

(1)對于加/減法運算指令,當操作數和運算結果為二進制的補碼表示的帶符號數時,V=1表示符號位溢出。

(2)對于其他的非加減法運算指令,V的值通常不變。

5、I(Interrupt Request):I=1表示禁止響應irq,I=0表示允許響應

6、F(Fast Interrupt Request):F=1表示禁止響應fiq,F=0表示允許響應

7、T(Thumb):T=0表示當前狀態位ARM狀態,T=1表示為Thumb狀態

8、M4-M0:表示當前處理器的工作模式,如圖:

七、工作模式的切換

(1)執行軟中斷(SWI)或復位命令(Reset)指令。如果在用戶模式下執行SWI指令,CPU就進入管理(Supervisor)模式。當然,在其他模式下執行SWI,也會進入該模式,不過一般操作系統不會這么做,因為除了用戶模式屬于非特權模式,其他模式都屬于特權模式。執行SWI指令一般是為了訪問系統資源,而在特權模式下可以訪問所有的系統資源。SWI指令一般用來為操作系統提供API接口。

(2)有外部中斷發生。如果發生了外部中斷,CPU就會進入IRQ或FIQ模式。

(3)CPU執行過程中產生異常。最典型的異常是由于MMU保護所引起的內存訪問異常,此時CPU會切換到Abort模式。如果是無效指令,則會進入Undefined模式。

(4)有一種模式是CPU無法自動進入的,這種模式就是System模式,要進入System模式必須由程序員編寫指令來實現。要進入System模式只需改變CPSR的模式位為System模式對應的模式位即可。進入System模式一般是為了利用System模式和用戶模式下的寄存器相同的特點,因此一般情況下,操作系統在通過SWI進入Supervisor模式后,做一些操作后,就進入System模式。

(5)在任何特權模式下,都可以通過修改CPSR的MODE域來進入其他模式。不過需要注意的是由于修改的CPSR是該模式下的影子CPSR,即SPSR,因此并不是實際的CPSR,所以一般的做法是修改影子CPSR,然后執行一個MOVS指令來恢復執行某個斷點并切換到新模式。

推薦閱讀:

1.從一個不起眼的小公司逐漸成為半導體行業巨頭,Microchip CEO史蒂夫桑吉不一般的“擴張”之路

2.這是一篇非常不錯的介紹U-boot工作機制的好文

3.我們吃蛋糕,手中的盤子小,卻可以吃掉大蛋糕,RAM就是這樣運行比自身更大的程序

4.超實用!一位嵌入式高手摸索出的Linux內核編譯步驟和經驗

-

處理器

+關注

關注

68文章

19825瀏覽量

233756 -

ARM

+關注

關注

134文章

9321瀏覽量

375442 -

編程

+關注

關注

88文章

3685瀏覽量

94923

原文標題:圖文并茂?一圖了解?其實這是一個ARM體系結構與編程模型的總結

文章出處:【微信號:gh_c472c2199c88,微信公眾號:嵌入式微處理器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

ARM體系結構與編程模型的總結

ARM體系結構與編程模型的總結

評論