文章來源:學(xué)習(xí)那些事

原文作者:小陳婆婆

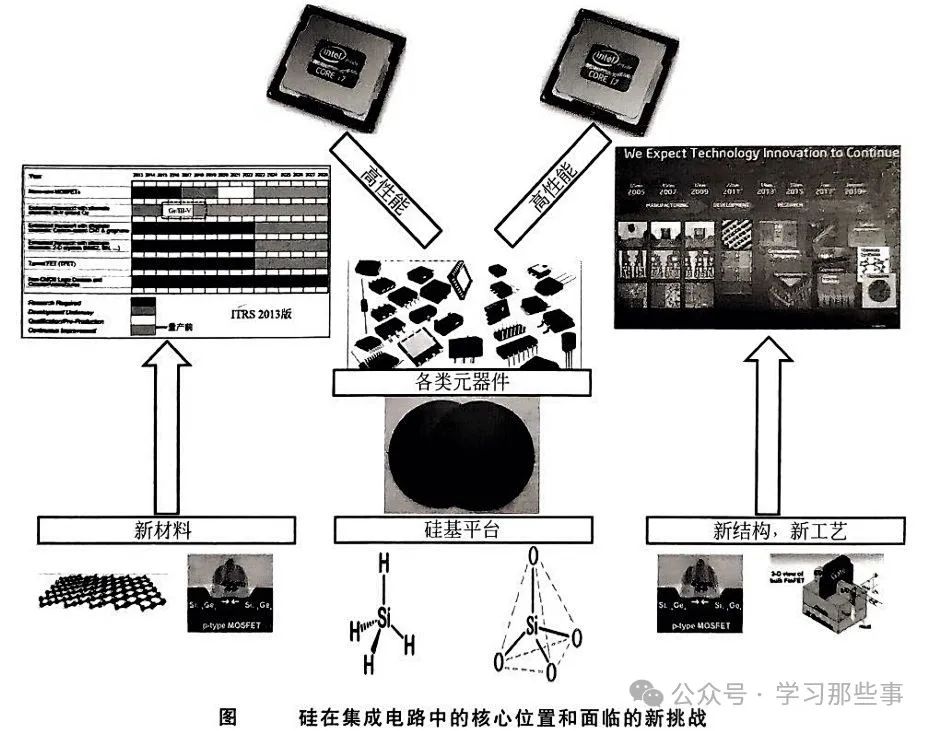

硅作為半導(dǎo)體材料在集成電路應(yīng)用中的核心地位無可爭(zhēng)議,然而,隨著科技的進(jìn)步和器件特征尺寸的不斷縮小,硅集成電路技術(shù)正面臨著一系列挑戰(zhàn),本文分述如下:1.硅集成電路的優(yōu)勢(shì)與地位;2.硅材料對(duì)CPU性能的影響;3.硅材料的技術(shù)革新。

硅集成電路的優(yōu)勢(shì)與地位

硅材料以其豐富的資源、優(yōu)質(zhì)的特性、完善的工藝以及廣泛的用途,在集成電路產(chǎn)業(yè)中占據(jù)了主導(dǎo)地位。其優(yōu)點(diǎn)包括:

1. 地球儲(chǔ)量豐富:硅原料成本低廉,易于獲取。

2. 工藝成熟:經(jīng)過幾十年的發(fā)展,硅的提純工藝已經(jīng)非常完善,能夠制造出所需的各類型晶體結(jié)構(gòu)。

3. 金半界面完美:Si/SiO2界面可以通過氧化獲得,為集成電路中的核心器件提供了基礎(chǔ)。

4. 摻雜和擴(kuò)散工藝成熟:硅的摻雜和擴(kuò)散工藝已經(jīng)積累了豐富的經(jīng)驗(yàn),可以滿足器件要求。

這些優(yōu)勢(shì)使得硅半導(dǎo)體材料在集成電路制造業(yè)中稱霸了半個(gè)世紀(jì)以上。然而,隨著器件特征尺寸的不斷縮小,硅集成電路技術(shù)正面臨著一系列挑戰(zhàn):

圖1 硅在集成電路中的核心位置和面臨的新挑戰(zhàn)

1. 物理極限的限制:當(dāng)器件尺寸進(jìn)入納米尺度后,一些基本物理規(guī)律開始發(fā)揮作用,如量子效應(yīng)、隧穿效應(yīng)等,這些效應(yīng)會(huì)影響器件的性能和穩(wěn)定性。柵極氧化層的厚度已經(jīng)接近或達(dá)到物理極限,進(jìn)一步減小將變得非常困難。

2. 材料、技術(shù)、器件和系統(tǒng)方面的物理限制:隨著尺寸的減小,熱管理問題變得越來越突出。小尺寸器件的散熱能力下降,容易導(dǎo)致溫度升高,影響器件性能和可靠性。制造成本隨著尺寸的減小而增加。雖然單位芯片的成本可能降低,但整體的制造成本由于工藝復(fù)雜度的增加而上升。器件間的互連問題變得更加復(fù)雜。隨著尺寸的減小,互連線的寬度和間距也減小,這增加了互連線的電阻和電容,從而影響了信號(hào)傳輸?shù)乃俣群唾|(zhì)量。

3. 一維發(fā)展模式的局限性:硅集成電路技術(shù)主要依賴于一維(即平面方向)的發(fā)展模式。然而,隨著尺寸的減小,這種模式已經(jīng)接近其物理極限。為了繼續(xù)提高集成電路的性能和密度,需要探索新的三維發(fā)展模式或其他新型技術(shù)。

面對(duì)這些挑戰(zhàn),硅集成電路技術(shù)可能需要與其他新型技術(shù)相結(jié)合或被完全替代。以下是一些可能的解決方案和未來趨勢(shì):

1. 三維集成電路技術(shù):通過堆疊多個(gè)二維芯片層來形成三維結(jié)構(gòu),從而提高集成電路的密度和性能。

2. 新型半導(dǎo)體材料:探索如碳納米管、二維材料(如石墨烯、二硫化鉬等)等新型半導(dǎo)體材料,以替代或補(bǔ)充硅材料。

3. 量子計(jì)算技術(shù):利用量子效應(yīng)來構(gòu)建全新的計(jì)算體系,從而突破傳統(tǒng)硅集成電路的物理極限。

4. 生物芯片技術(shù):利用生物分子來構(gòu)建芯片,實(shí)現(xiàn)生物與電子技術(shù)的融合。

綜上所述,硅作為半導(dǎo)體材料在集成電路應(yīng)用中的挑戰(zhàn)主要來自物理極限、材料和技術(shù)方面的限制。為了應(yīng)對(duì)這些挑戰(zhàn),需要不斷探索新的技術(shù)和材料,以推動(dòng)集成電路產(chǎn)業(yè)的持續(xù)發(fā)展。

硅材料對(duì)CPU性能的影響

在工藝層面,我們期望CPU具備以下特性:

速度更快:通過優(yōu)化設(shè)計(jì)和提高集成度,實(shí)現(xiàn)更高的運(yùn)算速度。

尺寸更小:縮小芯片尺寸以降低功耗和成本,同時(shí)提高集成密度。

閾值電壓更低:降低閾值電壓以減少功耗并提高性能。

飽和電流增大:增加飽和電流以提高輸出能力和響應(yīng)速度。

漏電流降低:減少漏電流以降低功耗和保持穩(wěn)定性。

寄生電容下降:降低寄生電容以減少信號(hào)延遲和功耗。

為了實(shí)現(xiàn)上述目標(biāo),我們需要對(duì)硅材料進(jìn)行改進(jìn),但面臨以下挑戰(zhàn):

遷移率限制:硅材料的遷移率受到材料特性和摻雜水平的限制,達(dá)到理論極限后需采用輔助工藝如應(yīng)力工程來提高。

介電材料限制:隨著尺寸減小,SiO2作為絕緣材料的厚度已達(dá)到極限,短溝道效應(yīng)明顯,需更換高介電常數(shù)材料。

物理極限:硅材料的尺寸存在物理極限,1nm為理論研究極限,1~4nm為物理極限,4nm為制造極限。

面對(duì)硅材料的挑戰(zhàn),研究者們正在探索替代材料,以延續(xù)摩爾定律:

高介電常數(shù)材料:如氧化鉿或氧化鋁,已在28nm工藝中廣泛應(yīng)用。

應(yīng)變硅技術(shù):通過引入應(yīng)變來提高硅材料的遷移率。

鍺或硅鍺材料:作為PMOS的溝道材料,有望在7nm以下工藝中實(shí)現(xiàn)。

三五族元素:作為NMOS的溝道材料,同樣有望在7nm以下工藝中替代硅。

隨著關(guān)鍵尺寸向物理極限的逼近,硅材料在CPU制造中的局限性日益凸顯。研究者們正在積極探索替代材料和技術(shù),以延續(xù)摩爾定律并推動(dòng)半導(dǎo)體產(chǎn)業(yè)的進(jìn)一步發(fā)展。在這個(gè)半導(dǎo)體產(chǎn)業(yè)的岔路口上,睿智的選擇將帶來新一輪的技術(shù)革命。

硅材料的技術(shù)革新

硅技術(shù)與非硅技術(shù)的集成

隨著硅材料在CPU制造中的局限性日益凸顯,許多公司和研究單位開始致力于硅技術(shù)與非硅技術(shù)的集成,以延長(zhǎng)摩爾定律。例如,將II-V族工藝技術(shù)與硅技術(shù)結(jié)合,實(shí)現(xiàn)硅基光電集成,被視為一個(gè)可能的解決方案。IBM公司在這一領(lǐng)域取得了顯著進(jìn)展,展示了將三五族銦鎵砷化合物放到絕緣上覆硅晶圓上的技術(shù),并聲稱采用標(biāo)準(zhǔn)塊狀硅晶圓制造硅上砷化銦鎵具有可行性。此外,國際微電子中心與Riber分子束外延設(shè)備公司合作,準(zhǔn)備建造用于在鍺襯底上生長(zhǎng)III-V族化合物半導(dǎo)體材料的串接式分子束外延設(shè)備。Intel公司也成功研制出混合硅激光器,這種激光器由熔合在硅片上的InP基材料作為光源和光放大介質(zhì),硅材料作為波導(dǎo)構(gòu)成。

后硅材料時(shí)代的研究進(jìn)展

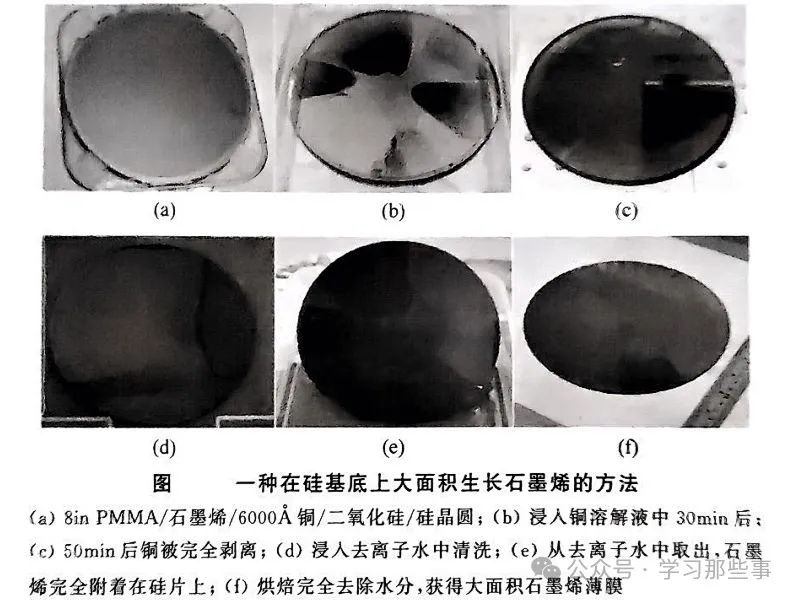

在后硅材料時(shí)代,研究者們正在積極探索各種新材料以替代硅。新加坡國立大學(xué)提出了一種在硅基底上大面積生長(zhǎng)石墨烯的較好方法,該方法利用石墨烯在金屬銅表面生長(zhǎng)的特點(diǎn),通過一系列工藝步驟最終在硅片上得到大面積石墨烯。

圖2 一種在硅基底上大面積生長(zhǎng)石墨烯的方法

(a)8in PMMA/石墨烯/銅/二氧化硅/硅晶圓;(b)浸入銅溶解液中30min后;(c)50min后銅被完全剝離;(d)浸入去離子水中清水;(e)去離子水中取出,石墨烯完全附著在硅片上;(f)烘焙完全去除水分,獲得大面積石墨烯薄膜

這些研究進(jìn)展使人們看到了后硅材料時(shí)代的曙光,預(yù)示著未來芯片制造將采用更多種類的非硅材料。

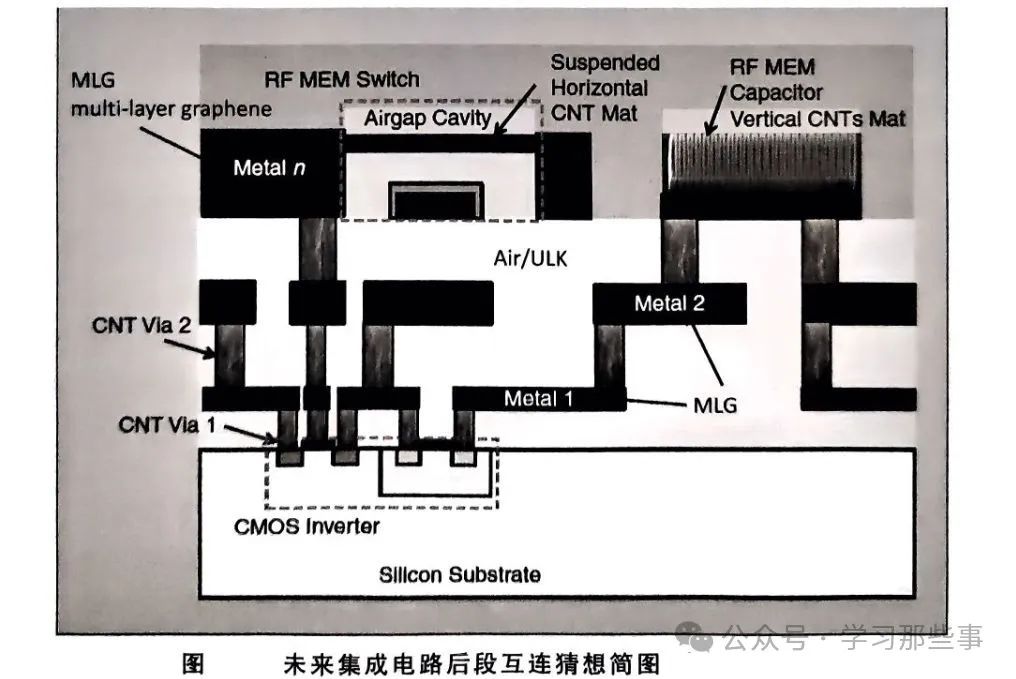

后段互連材料面臨的挑戰(zhàn)

隨著技術(shù)進(jìn)一步發(fā)展,尤其是進(jìn)入14nm以下工藝,后段互連材料面臨新的挑戰(zhàn)。銅已經(jīng)取代了鋁及鋁銅合金作為互連材料,因?yàn)槠渚哂懈偷碾娮杪省⒏叩碾娏髅芏群透蟮臒醾鲗?dǎo)系數(shù)。然而,隨著工藝尺寸的不斷縮小,對(duì)互連材料的要求也越來越高。同時(shí),超低絕緣常數(shù)材料也在不斷被開發(fā)以適應(yīng)不同工藝的需要。利用空氣填充金屬間的空隙也有望被引入實(shí)際工藝中。

新材料帶來的蝕刻技術(shù)挑戰(zhàn)

事實(shí)上,早在芯片制造發(fā)展之初,就已經(jīng)有大量替換硅溝道材料的研究。例如三五族材料、拓?fù)浒雽?dǎo)體、石墨烯、納米管線、黑磷、量子點(diǎn)等。這些新材料在芯片制造中的應(yīng)用給蝕刻技術(shù)帶來了新的挑戰(zhàn)。

圖3 未來集成電路后段互連猜想簡(jiǎn)圖

由于這些材料的物理和化學(xué)性質(zhì)與硅不同,因此需要開發(fā)新的蝕刻工藝和蝕刻劑以適應(yīng)這些材料的需求。這些挑戰(zhàn)需要研究者們不斷探索和創(chuàng)新,以推動(dòng)半導(dǎo)體產(chǎn)業(yè)的進(jìn)一步發(fā)展。

綜上,硅技術(shù)與非硅技術(shù)的集成、后硅材料時(shí)代的研究進(jìn)展以及后段互連材料面臨的挑戰(zhàn)都是當(dāng)前半導(dǎo)體產(chǎn)業(yè)研究的重要方向。研究者們正在積極探索各種新材料和新技術(shù),以應(yīng)對(duì)這些挑戰(zhàn)并推動(dòng)半導(dǎo)體產(chǎn)業(yè)的持續(xù)發(fā)展。

-

集成電路

+關(guān)注

關(guān)注

5420文章

12010瀏覽量

367772 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28766瀏覽量

235061 -

cpu

+關(guān)注

關(guān)注

68文章

11062瀏覽量

216454 -

硅材料

+關(guān)注

關(guān)注

0文章

47瀏覽量

8249

原文標(biāo)題:硅作為半導(dǎo)體材料在集成電路中的應(yīng)用及挑戰(zhàn)

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

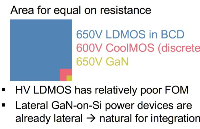

氮化鎵(GaN)功率集成電路(IC)開發(fā)的優(yōu)勢(shì)與挑戰(zhàn)

硅集成電路技術(shù)的優(yōu)勢(shì)與挑戰(zhàn)

硅集成電路技術(shù)的優(yōu)勢(shì)與挑戰(zhàn)

評(píng)論