文章來源:學習那些事???

原文作者:小陳婆婆???

半導體集成電路的可靠性評價是一個綜合性的過程,涉及多個關鍵技術和層面,本文分述如下:可靠性評價技術概述、可靠性評價的技術特點、可靠性評價的測試結構、MOS與雙極工藝可靠性評價測試結構差異。

可靠性評價技術概述

可靠性評價技術的核心組成部分

1.可靠性評價(REM):這是一個與時間密切相關的技術,旨在通過特定的測試結構和試驗方法來評估集成電路的可靠性。REM技術通過模擬實際使用環境中的各種應力條件,來揭示集成電路潛在的失效機理。

2.工藝質量監測(PCM):PCM技術關注于生產過程中的工藝參數,通過提取這些參數來監控工藝的穩定性。PCM為SPC提供了基礎數據,是確保工藝質量穩定的重要手段。

3.統計過程控制(SPC):SPC技術基于PCM提取的數據,運用統計學方法對工藝過程進行監控和控制。通過SPC,可以及時發現工藝中的異常波動,從而采取糾正措施,確保產品質量。

可靠性評價試驗的實施

1.可靠性評價測試結構:這些測試結構與待評估的集成電路經歷相同的工藝過程,因此能夠反映實際產品的可靠性水平。測試結構的設計應充分考慮集成電路的失效機理和應力條件,以確保評價的準確性。

2.加速試驗:加速試驗是可靠性評價中常用的一種方法,通過提高應力水平來加速失效過程,從而在較短的時間內獲得可靠性數據。加速試驗的關鍵在于選擇合適的加速因子和應力條件,以確保試驗結果的準確性和可靠性。

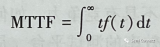

3.試驗數據的統計分析和計算:對試驗數據進行統計分析是可靠性評價的重要環節,通過計算各種可靠性指標(如失效率、平均無故障時間等)來定量評價工藝的可靠性。統計分析方法的選擇應根據試驗數據的特性和可靠性評價的需求來確定。

4.評價層次:可靠性評價試驗可以在不同的層次上進行,包括圓片級、裝配級和封裝級。每個層次的評價都有其特定的目標和要求,通過綜合各個層次的評價結果,可以全面評估集成電路的可靠性水平。

可靠性評價的意義和作用

提高產品質量:通過可靠性評價,可以及時發現和糾正工藝中的缺陷和問題,從而提高產品的質量水平。

降低生產風險:通過對薄弱環節的加固和改進,可以減少生產過程中的風險,提高產品的可靠性和穩定性。

支持產品研發:可靠性評價為產品研發提供了重要的數據支持,有助于優化產品設計,提高產品的市場競爭力。

綜上所述,半導體集成電路的可靠性評價是一個復雜而重要的過程,涉及多個技術和層面。通過綜合運用可靠性評價技術,可以全面評估集成電路的可靠性水平,為產品質量提升和產品研發提供有力支持。

可靠性評價的技術特點

簡化模型

1.多種失效機理并存:在一個電路中,往往存在多種失效機理,這些機理在電路的工作過程中同時起作用。

2.主導失效機理的識別:對于特定的電路,總會有一種失效機理起主導作用,成為電路失效的主要原因。其他失效機理雖然存在,但對電路的失效起次要作用,主要影響電路的失效時間。

3.單一失效機理模型的應用:在可靠性評價中,為了簡化問題并便于工程應用,通常針對單一失效機理來考慮,建立單一失效機理的可靠性評價模型。這種方法有助于更清晰地識別和解決主要的失效問題,提高評價的準確性和效率。

快速評價

1.加速試驗條件:可靠性評價試驗通常在高溫、大電流密度或高電壓條件下進行,這些條件能夠加速電路的失效過程。

2.加速系數的作用:通過提高應力條件,可以獲得較大的加速系數,從而在較短的時間內獲得一批可靠性數據。

3.快速評價的優勢:相對于使用失效來評價可靠性,加速試驗能夠在更短的時間內提供大量的可靠性數據。通過對這些數據的統計分析,可以對金屬化電遷移、熱載流子注入效應、與時間有關的柵介質擊穿、接觸退化、鍵合退化和表面態等可靠性問題進行評價。快速評價有助于及時發現和糾正工藝中的缺陷和問題,提高產品的質量和可靠性水平。

綜上所述,半導體集成電路可靠性評價的技術特點主要體現在簡化模型和快速評價兩個方面。簡化模型有助于更清晰地識別和解決主要的失效問題,而快速評價則能夠在較短的時間內提供大量的可靠性數據,為產品質量提升和工藝優化提供有力支持。

可靠性評價的測試結構

在半導體器件的可靠性評價中,測試結構扮演著至關重要的角色。

基本的可靠性測試結構

1.金屬電遷移/應力遷移測試結構:設計上采用各種結構的金屬條結構,用于評價金屬的抗電遷移和應力遷移能力。

2.連接孔的電遷移測試結構:專注于評價金屬間連接通孔的電遷移可靠性。

3.接觸退化測試結構:采用接觸孔及孔鏈結構,用于評價接觸電阻的退化情況。

4.熱載流子注入效應測試結構:主要采用不同寬長比的單管(MOS工藝)和各種NPN單管(雙極工藝),用于評價熱載流子注入對器件性能的影響。

5.與時間有關的柵介質擊穿測試結構:采用不同面積的柵氧化層電容,用于評價柵介質的擊穿特性。

6.鍵合退化測試結構:用于檢測鍵合性能的好壞,確保鍵合的可靠性。

7.濺射損傷測試結構:用于評價濺射工藝對可靠性的影響,特別是濺射時圓片表面充電對柵氧化層的影響。

8.界面態結構:用于表征工藝參數,如氧化層厚度、平帶電壓、閾值電壓等,以及測量陷阱電荷和界面態密度的變化量。

MOS與雙極工藝可靠性評價測試結構差異

MOS工藝

電遷移測試結構:采用各種結構的金屬條結構。

熱載流子注入效應測試結構:主要采用不同寬長比的單管。

與時間有關的柵介質擊穿測試結構:采用不同面積的柵氧化層電容。

接觸退化測試結構:采用接觸孔及孔鏈結構。

雙極工藝

電遷移測試結構:同樣采用各種結構的金屬條結構。

熱載流子注入效應測試結構:主要采用各種NPN單管。

接觸退化測試結構:與MOS電路相似,采用接觸孔及孔鏈結構。

參數漂移測試結構:主要采用柵控管、單管、氧化層電容結構,用于測量器件參數的變化情況。

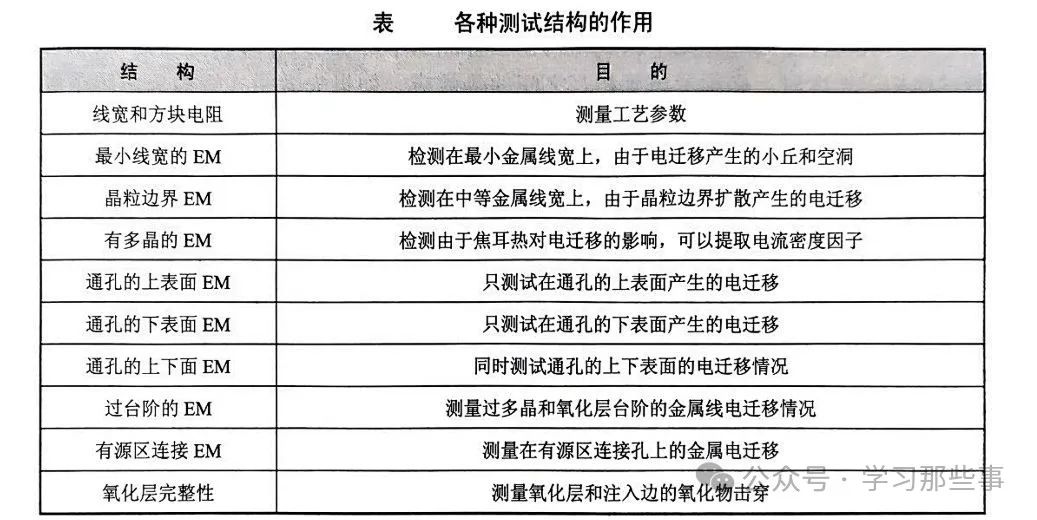

測試結構的作用與分類

作用:確認工藝線的可靠性水平,減少生產風險。

通過加速試驗或電測獲取基本的可靠性參數和可靠性信息。

分類:工藝用測試結構:用于對工藝參數進行檢測,包括薄層電阻結構、互連線結構、氧化層電容結構等。

可靠性評價用測試結構:用于對失效機理進行評價,包括金屬化電遷移、熱載流子注入效應、與時間有關的柵氧化層擊穿等測試結構。

其他實用的可靠性測試結構

電容電壓(CV)結構:用于表征工藝參數,如氧化層厚度、平帶電壓、閾值電壓等,以及測量陷阱電荷和界面態密度的變化量。

閂鎖測試結構:用于評價各種結構的抗閂鎖能力。

ESD測試結構:用于評價所設計的結構抗靜電放電性能。

通過綜合運用各種可靠性測試結構,可以全面評估半導體器件的可靠性水平,為產品質量提升和工藝優化提供有力支持。

影響測試結構的因素

在微電子工藝的可靠性評價中,測試結構的設計和實施受到多種因素的影響,這些因素直接關系到測試結果的準確性和可靠性。以下是對影響測試結構的主要因素進行重整和分述:

設計因素

1.范德堡圖形設計:

結構對稱性:范德堡圖形應高度對稱,以確保測試結果的準確性。

有效區域:正十字的中心部分是測試薄層電阻的有效區域,設計時應確保該區域符合要求。

引出臂長度:引出臂長度的選擇應合理,長寬比建議在1~2之間,以優化測試性能。

2.互連線測試結構設計:

長度要求:互連線測試結構應足夠長,以全面考察互連線的完整性。

3.金屬化電遷移測試結構:

直線設計:測試圖形通常為一條直的金屬線,設計在氧化層上。

橫截面積均勻性:金屬線的橫截面積應均勻,以保證測試線在形成明顯空洞前有近似均勻的溫度。

材料與工藝因素

1.金屬條性能穩定性:在應力作用下,被測金屬條的性能應穩定,能對金屬化質量問題做出敏感響應。

2.中位壽命:測試結構的中位壽命應足夠長,以便在電阻發生明顯變化前進行測量。

3.溫度選取:溫度的選取會影響失效時間的精度,應與金屬條在應力作用下的溫度平均值一致。

4.設計寬度一致性:當用中位失效時間對相同厚度的金屬化進行比較時,測試線應有相同的設計寬度。

測試條件與誤差控制

1.電壓降限制:在測試結構上,電壓降應受到限制,以減少失效瞬間可能因大電阻產生的熱能。

2.應力偏差控制:結構之間所受應力與應力平均值的偏差會影響失效時間,應保持在較小范圍內。

3.熱效應考慮:當芯片上有多個測試結構同時產生焦耳熱時,需考慮相互之間的熱效應,必要時對測量值進行校正。

4.熱載流子注入效應測試:測試結構應使用最小溝道長度,避免窄溝熱載流子注入效應,并確保所有引線端連接。

5.電容測試結構:包括大面積電容、條形電容和天線結構,用于考察氧化層的可靠性、缺陷率和電荷收集情況。

6.多晶柵電極考慮:當使用多晶作柵電極時,需考慮接觸電勢差和耗盡層的影響,以及高摻雜對耗盡效應的抑制作用。

7.表面漏電流控制:在設計和測試氧化層測試結構時,應考慮表面漏電流產生的誤差,并采取相應措施進行限制和校正。

8.電流源相關問題:避免高場穿透電流、位移電流、峰值電流和相鄰結構漏電流對測試結果的影響,采用寬條金屬和多晶連接線、多個并行連接孔和通孔等措施。

綜上所述,影響測試結構的因素涉及設計、材料與工藝、測試條件與誤差控制等多個方面。為確保測試結果的準確性和可靠性,在設計測試結構時應充分考慮這些因素,并采取相應的措施進行優化和控制。

-

集成電路

+關注

關注

5420文章

11971瀏覽量

367379 -

半導體

+關注

關注

335文章

28669瀏覽量

233395 -

可靠性

+關注

關注

4文章

269瀏覽量

27069

原文標題:一文了解半導體集成電路的可靠性評價

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

提供半導體工藝可靠性測試-WLR晶圓可靠性測試

基于集成電路的高可靠性電源設計

芯片,集成電路,半導體含義

如何實現高可靠性電源的半導體解決方案

集成電路與半導體

半導體集成電路的可靠性設計

半導體集成電路可靠性測試及數據處理

集成電路可靠性檢查的最佳實踐方案

半導體集成電路的可靠性評價

半導體集成電路的可靠性評價

評論