“細探 PCB 電路板設計中的流行趨勢。”

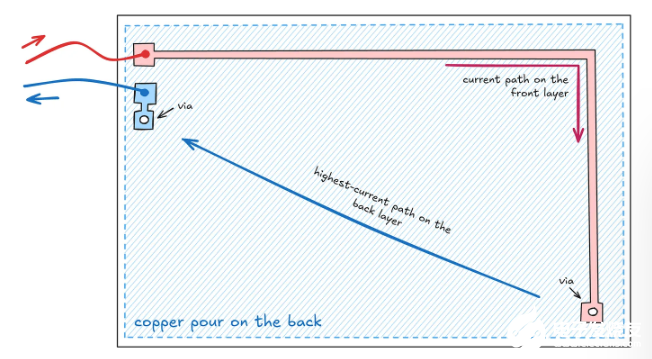

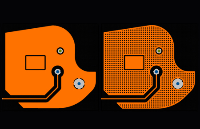

二十世紀八十年代初,一臺8位家用計算機中的典型 PCB 電路板大致長這樣:  Amstrad CPC 464主板細節圖

Amstrad CPC 464主板細節圖

到二十一世紀前十年,同類技術已演變成這樣的形態:

Arduino Uno R3產品宣傳圖特寫

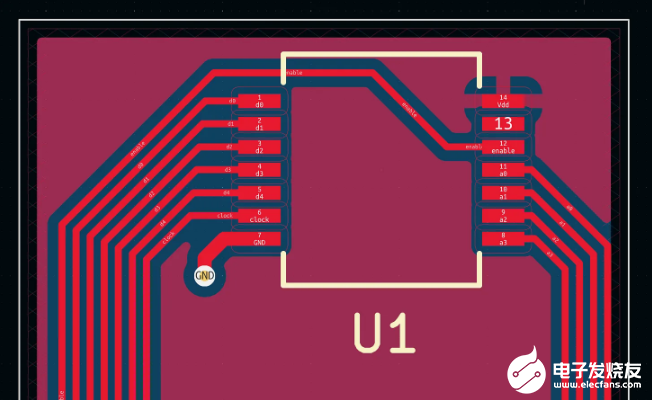

除了變得更小之外,最顯著的變化是鋪銅的應用——即通過計算機生成的區域填充PCB上走線之間的空白區域。

這種設計為何興起?一個籠統的答案是:在高速電子領域,該做法有助于改善信號完整性。這使得該方法在智能手機或臺式機等尖端應用中不可或缺。但顯然,我們討論的并非這類高端場景。

另一變化是 1980 年代美國聯邦通信委員會(FCC)開始將 47 CFR Part 15 規則(射頻干擾標準)應用于各類計算機設備。于是出現了所謂的"認證產業":需將原型送至認證實驗室,支付高昂的射頻測試費用,若未通過還需承擔額外成本與延誤。鋪銅能有效降低射頻輻射,因此常被預先采用以防萬一。

最后但同樣重要的是行業審美變遷:業余愛好者相互影響追隨產業潮流。任何非常規或過時的PCB美學設計常遭非議,即便批評者未必能明確指出設計缺陷。

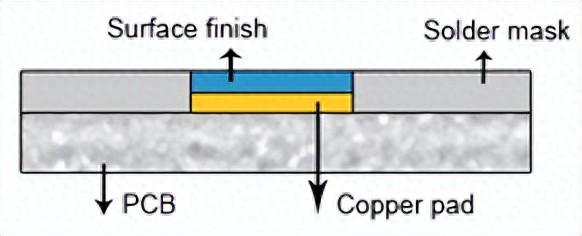

先別急,讓我們先直面最核心的問題:鋪銅究竟如何發揮作用?

先插個概念:共模扼流圈

電子電路中,電子流動雖受導體約束,但能量傳遞并非通過粒子碰撞實現,而是通過電磁場完成。電磁場源自于載流子,卻自由延伸至周圍空間。

鐵氧體等材料會通過價電子重排響應外部磁場,從而吸收周圍場能量。如果這個磁場是由附近的導體產生的,那么在鐵氧體重新排列電子的過程中,導體中的電流流動會暫時受到阻礙。這是因為鐵氧體在吸收磁場能量時,會對導體中的電流產生反作用力。隨著鐵氧體吸收越來越多的能量,它最終會達到飽和狀態,即它不能再吸收更多的磁場能量了。但即使在這種情況下,如果導體中的電流發生變化,鐵氧體仍然會阻礙這些變化,直到達到一個新的平衡狀態。

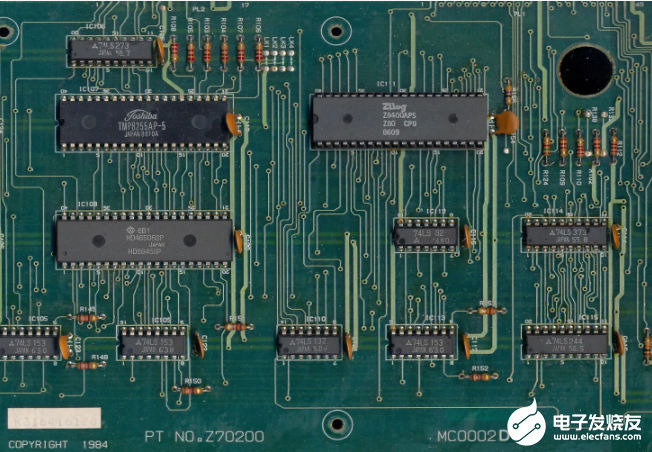

這是標準的電感原理,它有一個巧妙的變體:共模扼流圈。其基礎形態可見于某些計算機電纜:管狀鐵氧體元件包裹兩條同向導線。更緊湊的版本采用環形磁芯,每根導體繞制數匝:

共模扼流圈示意圖

共模電流情況:當兩個導線中有共模電流以相同方向流動時,會產生一個一致的磁場作用于鐵氧體(ferrite)。這使得該裝置表現得像一個普通的電感器,直流電(DC)可以順利通過,但對于高頻交流電(AC)成分,其會根據頻率變化的速率(即與交流頻率成正比)來減弱它們。這是因為電感對交流電會產生感抗,頻率越高,感抗越大,從而阻礙交流電的通過。 差模電流情況:相反地,如果存在互補的電流以相反方向流動,比如差分信號對或者連接到電源的“+”和“-”導線,那么產生的磁場會相互抵消,總和為零。這就沒有磁化現象發生,鐵氧體沒有吸收能量,所以裝置的感抗(衡量其對交流信號衰減程度的一個類似電阻的指標)保持在較低水平。 共模扼流圈可以抑制長電纜上的射頻干擾:射頻干擾通常會在所有捆綁的導體中產生相同的感應電動勢,導致產生的電流是共模的。而共模扼流圈可以將這些共模電流與我們關心的差分信號區分開來,從而起到抑制長電纜上射頻干擾的作用。

回到鋪銅

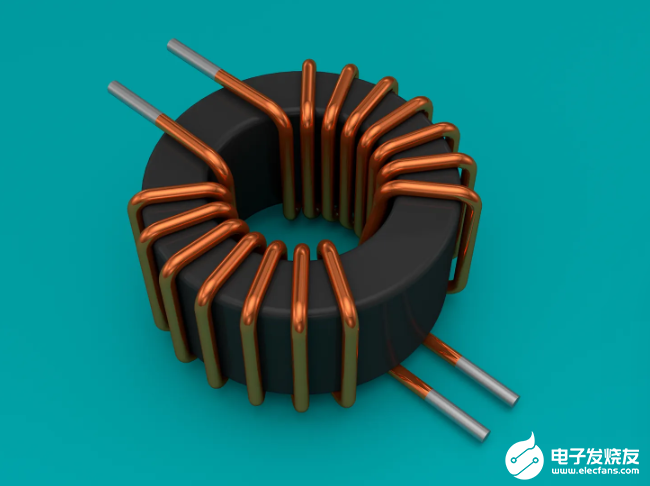

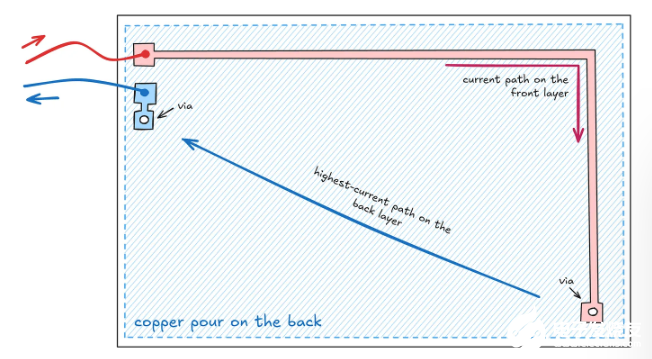

電感現象不僅限于鐵氧體磁芯,PCB走線同樣存在(雖程度輕微)。為了更直觀地讓大家理解PCB走線電感為什么重要,舉一個具體的電路板例子。這個電路板的結構是:在頂層有一個單獨的紅色走線,在底層有一個藍色的鋪銅平面,還有兩個過孔(vias)來完成整個電路的連接。

簡易PCB結構示意圖

當在 PCB 的引腳上施加直流(DC)信號時,頂層的“正向”電流被限制在走線內。而底層的返回電流理論上可以自由地擴散,但實際上它會選擇電阻最小的路徑,也就是兩個過孔(vias)之間的最短直線路徑。這是因為電流總是傾向于沿著阻抗最小的路徑流動,以最小化能量損耗。

隨著正弦波頻率 f 的升高,原始電流路徑中的磁化相關準電阻效應也會增加。這是因為PCB走線具有電感特性,電感值 L 通常在幾十到幾百納亨利之間,具體取決于走線的長度和其他因素。對于給定的頻率f和電感L,感抗的公式為:

即 20MHz 正弦頻率下,感抗可達約50Ω。

所幸存在補償機制:若底層回流路徑緊貼頂層走線投影路徑,則形成類似共模扼流圈狀態——磁場相互抵消,阻抗保持較低水平。

這就會引出兩個實際問題:

其一,如果正向路徑和最佳可用的返回路徑相距較遠,那么就會產生較高的阻抗。在這種情況下,高速數據線上會有更多的能量以電磁波的形式輻射到周圍空間。這不僅會導致信號傳輸的損耗,還可能對周圍的電子設備產生電磁干擾。

其二,如果附近存在一些不相關的“受害”走線,并且這些走線提供了一條返回地的路徑(即使是通過集成電路的本體),那么電流可能會選擇這條路徑,而不是我們精心設計的電流路徑。這可能會導致信號傳輸的錯誤和不穩定,因為電流的路徑不再是我們預期的那樣。

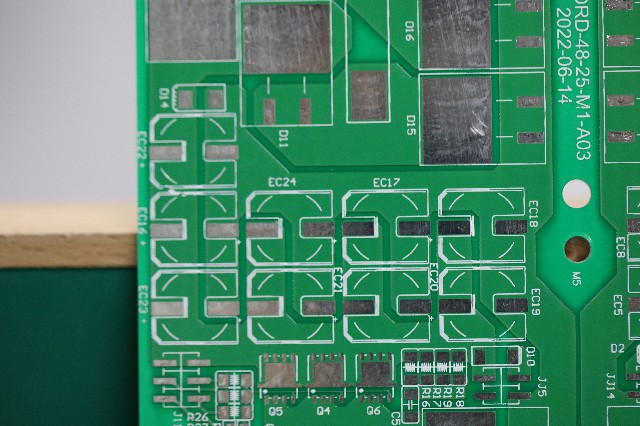

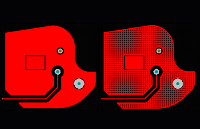

是否需要整板鋪銅?

未必。鋪銅并非唯一解決方案,但相比手動為每個數據總線布設電流回流通道,這種方法能節省時間。

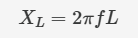

無論采用何種方法,都需審慎設計。比如鋪銅不連續導致的問題:

不連續鋪銅導致劣質回流路徑

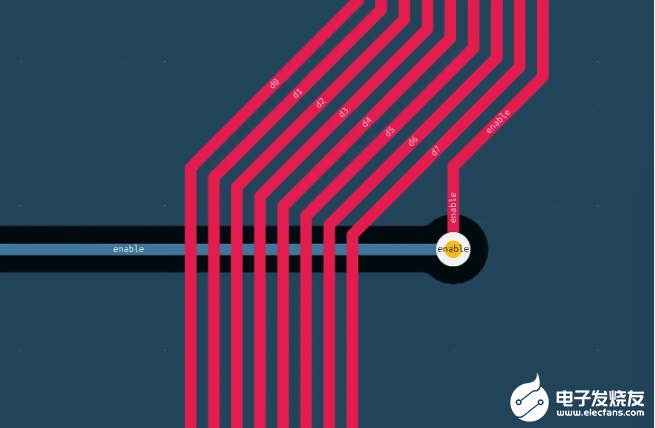

銅鋪也容易讓人忽視電源布線的問題。例如,下圖芯片右上角的 Vdd 供電設計就不太好。  正極供電路徑很長 為了簡化設計,一些愛好者會選擇使用四層板,將中間兩層專用于GND與Vdd。此方案有效但成本倍增。 另一個問題在于:電源平面(或者鋪銅)可以降低 PCB 的電感,但會增加整個 PCB 的旁路電容。對數字信號而言,增加的旁路電容通常是可以接受的,因為它有助于穩定信號和減少噪聲。然而,在模擬電子電路中,特別是在運算放大器(op-amp)的反饋回路中,每增加一點旁路電容(如幾皮法拉)都可能帶來不良影響。 實際應用中,對多數使用ESP32、樹莓派或8位AVR單片機的項目而言,無需過度糾結:鋪銅應以便利設計為準則,而非盲目追隨網絡建議。真正挑戰始于處理MIPI-DSI、USB3.0等高速接口時。

正極供電路徑很長 為了簡化設計,一些愛好者會選擇使用四層板,將中間兩層專用于GND與Vdd。此方案有效但成本倍增。 另一個問題在于:電源平面(或者鋪銅)可以降低 PCB 的電感,但會增加整個 PCB 的旁路電容。對數字信號而言,增加的旁路電容通常是可以接受的,因為它有助于穩定信號和減少噪聲。然而,在模擬電子電路中,特別是在運算放大器(op-amp)的反饋回路中,每增加一點旁路電容(如幾皮法拉)都可能帶來不良影響。 實際應用中,對多數使用ESP32、樹莓派或8位AVR單片機的項目而言,無需過度糾結:鋪銅應以便利設計為準則,而非盲目追隨網絡建議。真正挑戰始于處理MIPI-DSI、USB3.0等高速接口時。

原文轉載自: https://lcamtuf.substack.com/p/pcbs-ground-planes-and-you 已做翻譯及修訂

注意:如果想第一時間收到 KiCad 內容推送,請點擊下方的名片,按關注,再設為星標。

常用合集匯總:

和 Dr Peter 一起學 KiCad

KiCad 8 探秘合集

KiCad 使用經驗分享

KiCad 設計項目(Made with KiCad)

常見問題與解決方法

KiCad 開發筆記

插件應用

發布記錄

審核編輯 黃宇

-

pcb

+關注

關注

4368文章

23489瀏覽量

409675 -

電路板

+關注

關注

140文章

5133瀏覽量

102623

發布評論請先 登錄

一文告訴你為什么不要隨便在高速線旁邊鋪銅!

PCB盜銅工藝:技術與藝術的完美融合

PCB設計中填充銅和網格銅有什么區別?(更新版)

深度解析:PCB死銅問題的根源與處理方法

詳解PCB噴錫/熱風整平工藝

PCB 需要整板鋪銅嗎?

PCB 需要整板鋪銅嗎?

評論