智多晶204B IP的應用領域

隨著高速AD/DA接口在數字接口中越來越廣泛的運用,204B協議作為重要的通訊協議,目前已經發揮出越來越重要的作用。204B協議目前主要運用于數據通信、工業自動化、物聯網、汽車電子、醫療設備等領域。相對于傳統的AD/DA傳輸接口,204B協議主要具有以下優勢:支持高帶寬和低延遲,適合實時應用;提供統一標準,簡化集成和開發;支持大數據傳輸,能滿足高流量需求。

智多晶204B IP配置界面

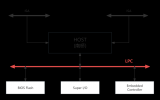

智多晶 204B IP提供了針對204B 協議層的處理能力,能夠與高速AD/DA芯片進行收發的對接工作。智多晶 204B IP支持協議所規定的CGS(Code group synchronization)、ILA(Initial Lane Alignment) 以及數據載荷的正常傳輸過程,并通過SYSREF和SYNC信號實現204B規定的通訊功能。智多晶204B IP位于SerDes之上,需要配合智多晶的SerDes IP同時使用才能夠完成和外圍芯片的通訊。用戶可根據外圍AD或者DA芯片的特性,對智多晶204B IP進行配置,以滿足設計需求。

-

接口

+關注

關注

33文章

8967瀏覽量

153347 -

物聯網

+關注

關注

2928文章

46015瀏覽量

389336 -

IP

+關注

關注

5文章

1791瀏覽量

151692

原文標題:“芯”技術分享 | 智多晶204B IP

文章出處:【微信號:智多晶,微信公眾號:智多晶】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

智多晶FIFO_Generator IP介紹

智多晶LPC_Controller IP介紹

智多晶Serdes IP的應用領域及工作原理

使用jesd204b IP核時,無法完成綜合,找不到jesd204_0.v

請問一下204B接口的各個層次?

JESD204B使用說明

用一顆5G的204B接口DA芯片,DA芯片的輸入時鐘大小和輸入數據的速率是怎么樣的關系?

Altera JESD204B IP核和TI DAC37J84硬件檢查報告

智多晶204B IP的應用領域

智多晶204B IP的應用領域

評論