EMI(電磁干擾)噪聲源的分析與優(yōu)化方法是電力電子系統(tǒng)設(shè)計中的重要環(huán)節(jié)。以下是對EMI噪聲源的分析以及優(yōu)化方法的詳細探討:

一、EMI噪聲源分析

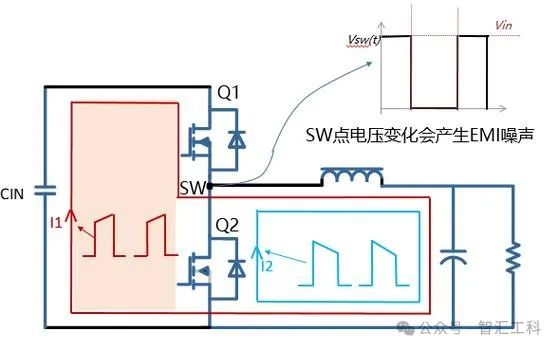

EMI噪聲主要來源于電力電子系統(tǒng)中的半導體器件在開關(guān)過程中產(chǎn)生的高dv/dt節(jié)點與高di/dt環(huán)路。這些快速的電壓和電流變化會激發(fā)電磁場,進而產(chǎn)生電磁干擾。EMI噪聲可以分為共模噪聲和差模噪聲兩種類型:

1. 共模噪聲:共模噪聲是待測零部件的LN線和參考地之間的電位差。它通常通過寄生電容和高dV/dt進行傳導,沿著任意信號(正或負)到地(GND)的路徑傳輸。

2. 差模噪聲:差模噪聲是LN線之間的電位差。它通過寄生電感(磁耦合)和高di/dt進行傳導。

在開關(guān)電源中,如Buck變換器,其EMI噪聲源主要為開關(guān)節(jié)點的電壓。該電壓波形可以等效為一個梯形波,其幅值、上升時間、下降時間以及開關(guān)頻率等因素都會影響EMI噪聲的頻譜特性。

二、EMI優(yōu)化方法

針對EMI噪聲源,可以采取以下優(yōu)化方法:

1. 對開關(guān)波形振蕩的優(yōu)化:

●在實際電路中,芯片、無源元件以及PCB走線都會帶來一些寄生參數(shù),這些寄生參數(shù)在開關(guān)過程中會造成振蕩。為了減小振蕩,可以從芯片設(shè)計、封裝技術(shù)以及板級電路設(shè)計等方面進行優(yōu)化。

●從芯片設(shè)計上,可以采用更先進的工藝和封裝技術(shù)來減小寄生參數(shù)。例如,使用倒裝封裝技術(shù)可以大幅減小封裝帶來的寄生電感。

●在板級電路設(shè)計上,可以通過優(yōu)化布局、使用緩沖器電路(如RC濾波器)來抑制開關(guān)節(jié)點的振鈴現(xiàn)象。

2. 抖頻設(shè)計:

●抖頻技術(shù)通過在一定范圍內(nèi)調(diào)制開關(guān)頻率,將峰值噪聲分布到更寬的頻率范圍內(nèi),從而降低EMI。這種方法在許多開關(guān)穩(wěn)壓器中都得到了應(yīng)用。

3. 濾波與屏蔽:

●濾波是提取有用信號、抑制無用噪聲的技術(shù)。在電路中加入適當?shù)臑V波器可以有效地降低EMI噪聲。

●屏蔽則是用導電或電磁體的封閉面將其內(nèi)外兩側(cè)空間進行電磁性隔離,以抑制過空間的輻射干擾。屏蔽的設(shè)計既可以針對干擾源,也可以針對受擾體。

4. 布局優(yōu)化:

●電源布局與組件選擇同樣重要。布局優(yōu)化通常是一個迭代過程,經(jīng)驗豐富的設(shè)計人員可以減少迭代次數(shù),從而避免延誤和額外的設(shè)計成本。

5. 使用低噪聲組件:

●選擇具有低噪聲特性的組件也是降低EMI的有效方法。例如,使用低噪聲的穩(wěn)壓器、濾波器等。

6. 減小電流回路面積:

●高di/dt回路(熱回路)中的高di/dt和寄生電感是導致電磁噪聲和開關(guān)振鈴的主要原因。為了減小EMI,應(yīng)盡量減小電流回路的面積。這可以通過優(yōu)化PCB布局、使用零阻抗的理想電容等方法來實現(xiàn)。

綜上所述,EMI噪聲源的分析與優(yōu)化方法涉及多個方面,包括開關(guān)波形振蕩的優(yōu)化、抖頻設(shè)計、濾波與屏蔽、布局優(yōu)化以及使用低噪聲組件等。在實際設(shè)計中,應(yīng)根據(jù)具體的應(yīng)用場景和需求選擇合適的優(yōu)化方法以降低EMI噪聲。

審核編輯 黃宇

-

emi

+關(guān)注

關(guān)注

53文章

3738瀏覽量

130747 -

噪聲源

+關(guān)注

關(guān)注

0文章

42瀏覽量

11650

發(fā)布評論請先 登錄

提高SEA模型PBNR計算精度的方法及策略

輪轂電機電磁噪聲測試方法及特性分析

精選好文!噪聲系數(shù)測量的三種方法

如何抑制電子電路中的噪聲

是德示波器噪聲水平的優(yōu)化方法

頻域示波器在電源噪聲分析中的應(yīng)用

設(shè)計EMI/EMC安全的電池包

Buck變換器中EMI噪聲源的優(yōu)化方法

16603系列噪聲源介紹

AN-1120: 低壓差(LDO)調(diào)節(jié)器的噪聲源

EMI 噪聲源的分析與優(yōu)化方法

EMI 噪聲源的分析與優(yōu)化方法

評論