設(shè)計(jì)人員需要一套能夠無(wú)縫地運(yùn)行前端到后端設(shè)計(jì)的集成式工具。西門子 EDA 的全流程產(chǎn)品組合提供了執(zhí)行模擬/混合信號(hào)集成電路 (IC) 設(shè)計(jì)所需的所有不可或缺的工具。本文將簡(jiǎn)要概述使用 S-Edit 原理圖輸入環(huán)境的前端流程,然后更詳細(xì)地描述 Analog FastSPICE (AFS) 平臺(tái)仿真器以及使用該仿真器進(jìn)行基本放大器設(shè)計(jì)驗(yàn)證的步驟。

S-Edit

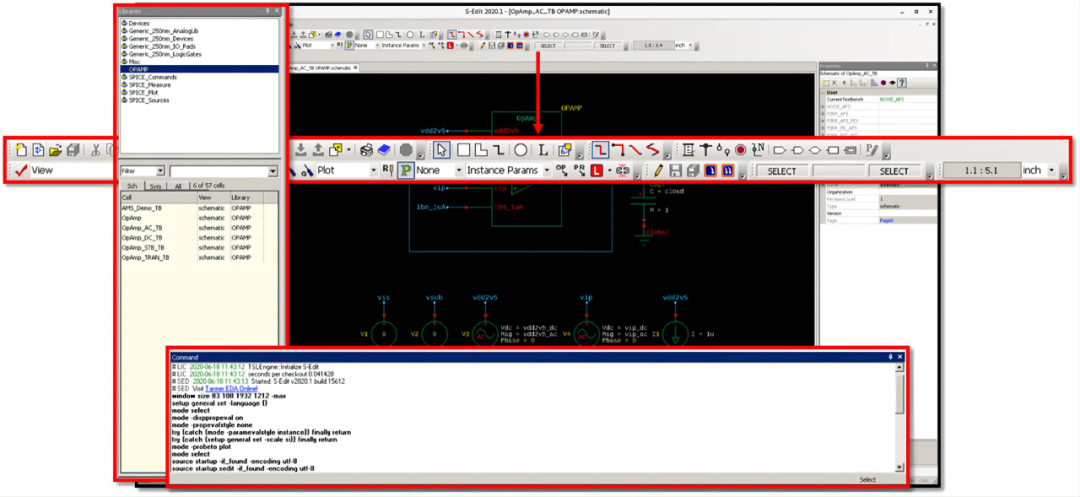

S-Edit 通過(guò)一個(gè)直觀且高度可定制的圖形界面與所有西門子仿真器產(chǎn)品無(wú)縫集成。S-Edit 開(kāi)箱即用,非常容易上手,消除了切換工具時(shí)常常需要的大量學(xué)習(xí)時(shí)間。S-Edit 頂部提供了全面且可自定義的工具欄,可以輕松訪問(wèn)許多設(shè)計(jì)功能的快捷方式并提高生產(chǎn)效率,因?yàn)闊o(wú)需在復(fù)雜的子菜單和下拉選項(xiàng)中查找功能。與設(shè)計(jì)相關(guān)聯(lián)的庫(kù)和單元、命令窗口以及與實(shí)例或測(cè)試電路相關(guān)聯(lián)的屬性,在 S-Edit 中的位置都很靈活,可以分離并且易于重新配置,以適合任何工作方式或顯示風(fēng)格。

S-Edit 原理圖輸入環(huán)境

運(yùn)算放大器設(shè)計(jì)

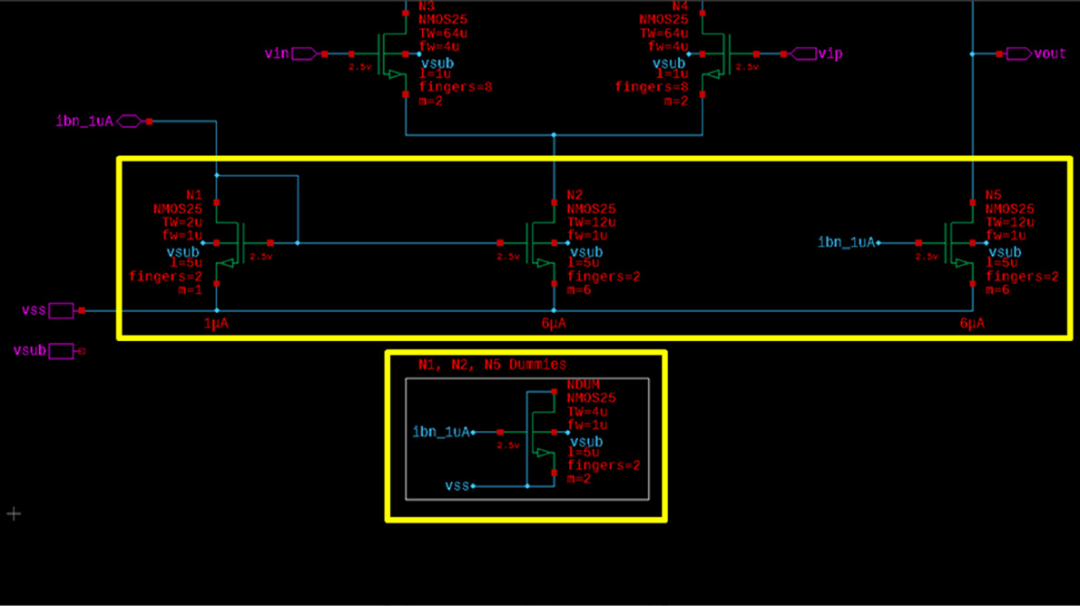

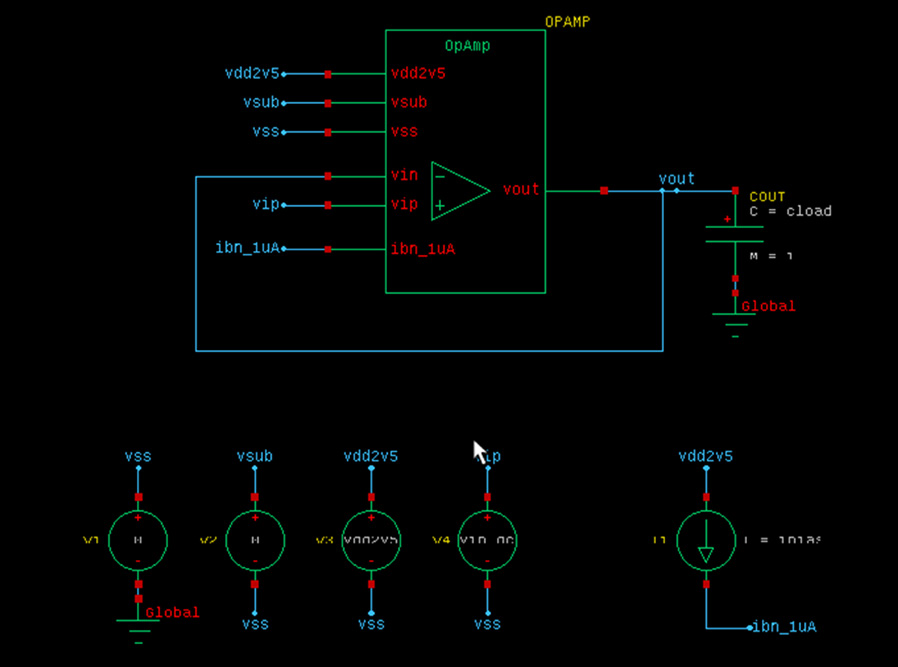

S-Edit 中繪制了一個(gè)八晶體管、兩級(jí)運(yùn)算放大器 (op amp) 設(shè)計(jì)實(shí)現(xiàn)的簡(jiǎn)易原理圖。底部繪制了虛設(shè)器件,以便為 NMOS 下拉電流構(gòu)建完整的矩形中心對(duì)稱版圖結(jié)構(gòu)。下圖所示為運(yùn)算放大器設(shè)計(jì)單位增益反饋配置的輸出補(bǔ)償放大器的簡(jiǎn)易直流測(cè)試電路。

一個(gè)兩級(jí)運(yùn)算放大器的原理圖

直流測(cè)試電路

仿真設(shè)置

仿真設(shè)置可以使用下圖所示的相關(guān)工具欄按鈕啟動(dòng),允許用戶對(duì)各種仿真分析及測(cè)試電路進(jìn)行設(shè)置。

用于啟動(dòng)仿真設(shè)置窗口的菜單圖標(biāo)

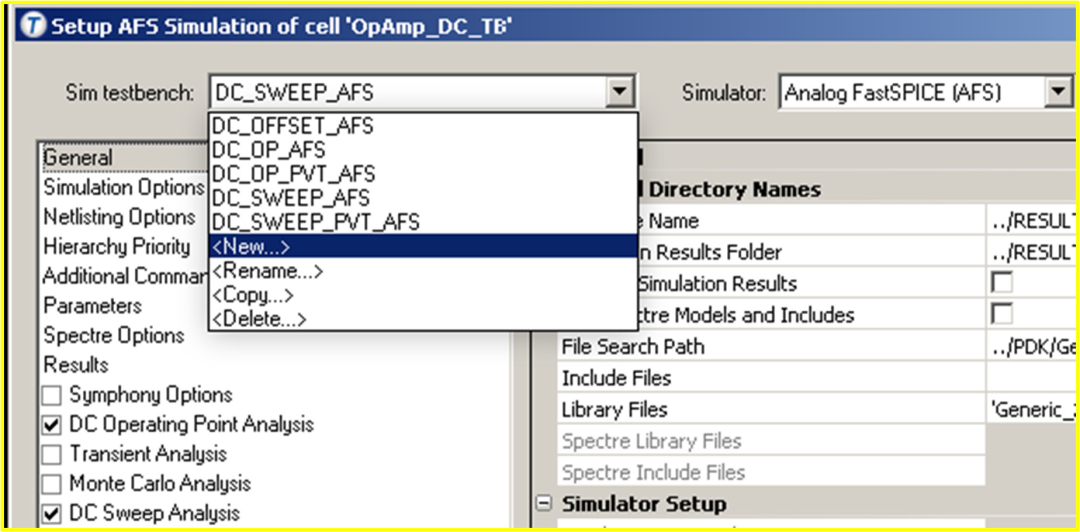

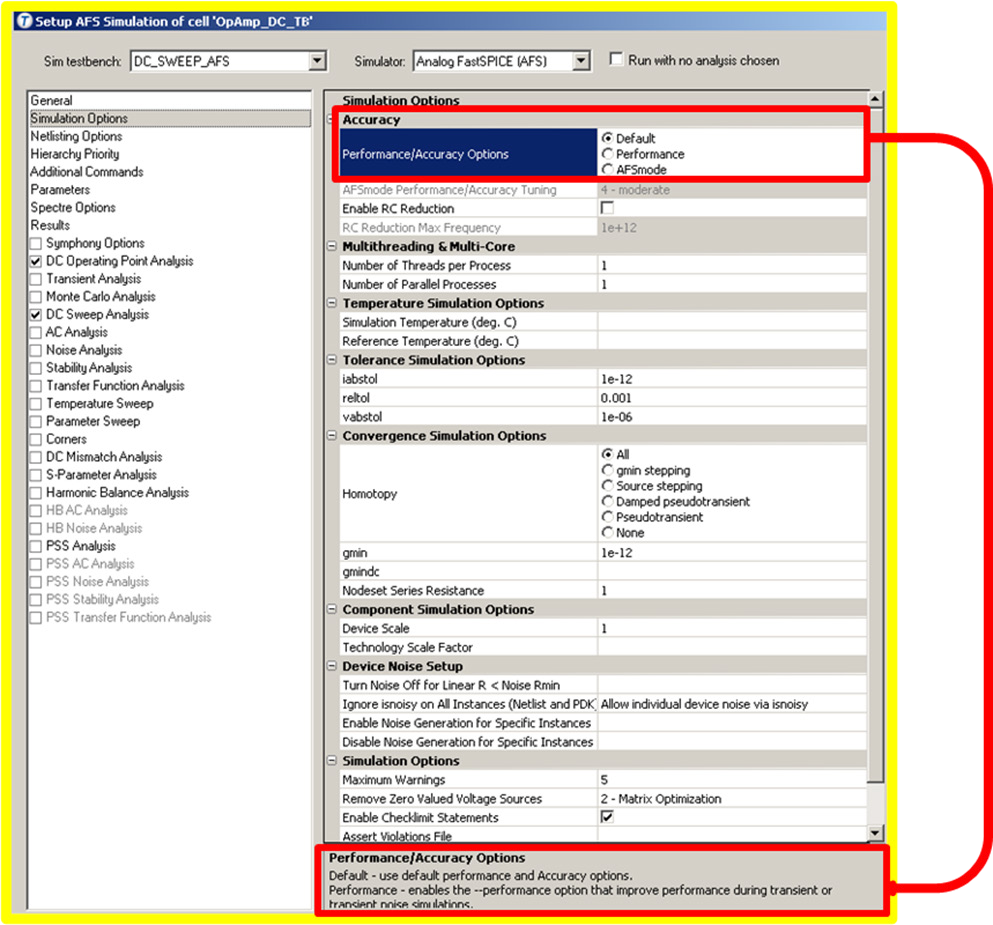

在仿真設(shè)置窗口中,可以使用 Sim testbench(仿真測(cè)試電路)下拉菜單創(chuàng)建測(cè)試電路。選擇仿真器后,圖形界面上的所有相關(guān)仿真選項(xiàng)和分析都會(huì)相應(yīng)地調(diào)整。S-Edit 支持三個(gè)仿真器:T-Spice、Eldo 和 AFS。針對(duì)此設(shè)計(jì),已創(chuàng)建若干直流仿真測(cè)試電路。原理圖測(cè)試電路可能與幾個(gè)全部在此菜單下創(chuàng)建、重命名、復(fù)制和保存的不同仿真測(cè)試電路相關(guān)聯(lián)。

用于直流掃描分析的仿真測(cè)試電路設(shè)置

值得注意的是,其中沒(méi)有隱藏選項(xiàng)或彈出式菜單,所有內(nèi)容全部顯示在仿真設(shè)置中各個(gè)相應(yīng)的子窗口中。例如,AFS 的 Simulation Options(仿真選項(xiàng))子菜單如下圖所示。選擇一個(gè)選項(xiàng)會(huì)在底部顯示用戶手冊(cè)中的簡(jiǎn)要說(shuō)明。

仿真設(shè)置窗口及幫助

-

IC設(shè)計(jì)

+關(guān)注

關(guān)注

38文章

1352瀏覽量

105400 -

西門子

+關(guān)注

關(guān)注

98文章

3142瀏覽量

117903 -

仿真器

+關(guān)注

關(guān)注

14文章

1034瀏覽量

85116 -

eda

+關(guān)注

關(guān)注

71文章

2904瀏覽量

176797

原文標(biāo)題:西門子 EDA 的全流程產(chǎn)品組合助力工程師實(shí)現(xiàn)出色的 IC 設(shè)計(jì)驗(yàn)證效率

文章出處:【微信號(hào):Mentor明導(dǎo),微信公眾號(hào):西門子EDA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

西門子收購(gòu)Mentor會(huì)對(duì)EDA工具用戶帶來(lái)哪些改變?

加速創(chuàng)“芯” 西門子EDA技術(shù)峰會(huì)在滬舉辦

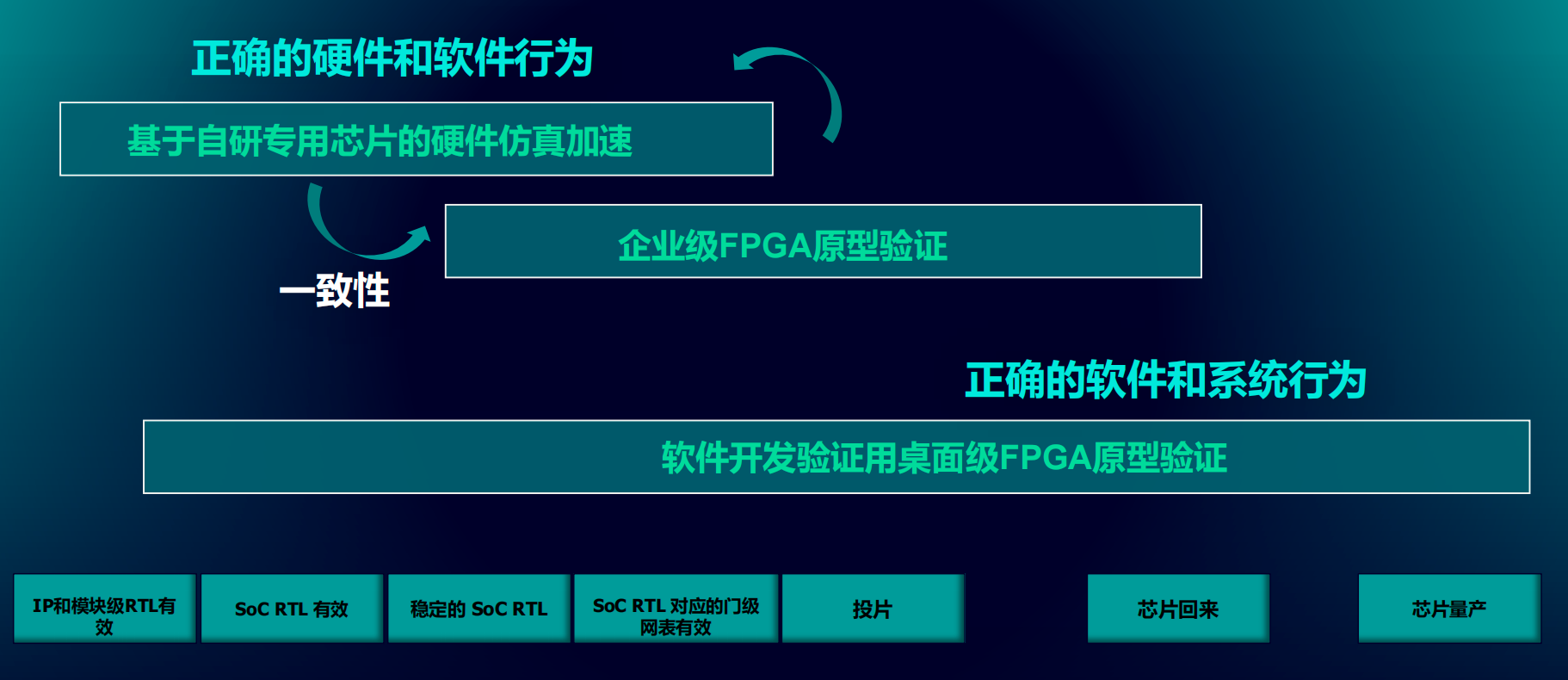

基于自研芯片+頂級(jí)AMD FPGA,西門子EDA發(fā)布“快而全”的Veloce CS

西門子收購(gòu)Solido強(qiáng)勢(shì)進(jìn)軍EDA領(lǐng)域

西門子EDA產(chǎn)品OneSpin助力實(shí)現(xiàn)精確的驗(yàn)證覆蓋率指標(biāo)

西門子Calibre平臺(tái)擴(kuò)展EDA早期設(shè)計(jì)驗(yàn)證解決方案

Chipletz采用西門子EDA解決方案,攻克Smart Substrate IC封裝技術(shù)

加速創(chuàng)“芯” 西門子EDA技術(shù)峰會(huì)在滬舉辦

西門子完成對(duì)EDA軟件公司Insight EDA的收購(gòu)

EDA助力良率提升:紫光展銳與西門子的成功合作

西門子EDA新一代平臺(tái)版本升級(jí)

西門子EDA亮相2025玄鐵RISC-V生態(tài)大會(huì)

西門子EDA工具如何助力行業(yè)克服技術(shù)挑戰(zhàn)

西門子推出Questa One智能驗(yàn)證解決方案

西門子再收購(gòu)EDA公司 西門子宣布收購(gòu)Excellicon公司 時(shí)序約束工具開(kāi)發(fā)商

西門子EDA助力提升IC設(shè)計(jì)驗(yàn)證效率

西門子EDA助力提升IC設(shè)計(jì)驗(yàn)證效率

評(píng)論