在現代電子測量、雷達、通信系統、電子對抗等技術領域中,具有頻率范圍寬,分辨率高,轉換快速的多種模式的信號源是重要和必不可少的。20世紀70~80年代大都采用鎖相頻率合成技術,實現頻率范圍為DC(MHz)~幾十GHz,分辨率達到MHz的信號源。雖然轉換速度不高(幾十μs到ms量級),但已廣泛應用到現代電子系統中;與此同時,各種規格的鎖相頻率合成技術的信號源產品也投入到國際市場。

隨著電子技術和集成電路的飛速發展,進入20世紀90年代后,出現了頻率分辨率高(MHz量級),頻率轉換快(μs到ns量級)的DDS大規模芯片,輸出信號的頻率上限基本止在HF或VHF頻段內,比PLL合成技術以及直接模擬合成技術所得到的信號頻率低。當要求得到既有高的頻率分辨率,又有較快的轉換速度和較低噪聲的超高頻(UHF),甚至微波信號時,DDS+PLL技術就顯示出了強大的生命力。

一、Q2230的基本結構及實現的頻率合成器

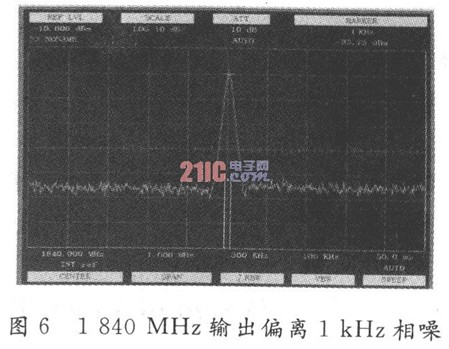

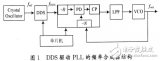

Q2230是QUALCOMM公司生產的一種單片單通道85 MHz的DDS器件。它有串并行控制接口,采用85 MHz的時鐘,可以合成出DC~34 MHz,具有20 MHz分辨率的信號頻率范圍。它的基本組成框圖如圖1所示。

它由頻率控制緩沖器、頻率控制寄存器、相位累加器、相位累加寄存器、正弦檢索表5個部分組成,設有串并行輸入控制的頻率控制寄存器、32位的高速相位寄存器及輸出12位的正弦量。

頻率控制緩沖器 將輸入代表頻率的數碼暫存起來。

頻率控制寄存器 在寫入脈沖的作用下,將緩沖器中的代表頻率的二進制碼寫入該寄存器。

相位累加器 根據寄存器的代表頻率的字,對系統時鐘的相位進行抽樣。

圖2示出了相位步長△ψ與輸出頻率的關系。

正弦檢索表將相應累加器輸出的離散數字變換為相應的正弦波形離散幅度數字,再經外接的D/A轉換器和低通濾波器就可獲得正弦信號。

圖3示出了用Q2230組成的頻率合成器及工作波形。

1.頻率控制值的計算

根據DDS調諧方程

當fs為40 MHz,輸出頻率為12.5 MHz時,可以按上式計算出頻率控制值的相位步長字,以便控制頻率變化。

因此通過改變寫入到頻率控制寄存器的頻率字△ψ的大小,可達到精確改變輸出頻率的目的。

2.頻率分辨率的計算設頻率分辨率fr為

當fs=40 MHz時

3.最低頻率和最高頻率的計算

芯片中相位累加器的步長M-32,當相位累加器的相位取樣步長M-1時,參考時鐘相位的取樣點數達到最大值為△ψ=1,此時DDS輸出的頻率fo為最低,即fomin=fs/232。40 MHz時,fomin=0. 01 Hz。當相位字長Aψ=232時,輸出頻率fomax=AφXfs/232。根據取樣定理,輸出信號基波最高頻率應低于所用參考時鐘頻率的一半,fomax=20 MHz,實際中只能用到fs的40%,即16 MHz。

-

DDS

+關注

關注

22文章

671瀏覽量

154112 -

Q2230

+關注

關注

0文章

2瀏覽量

2329

發布評論請先 登錄

關于DDS+PLL雷達發射源芯片選型問題請教

DDS PLL短波頻率合成器設計

采用DDS+PLL技術實現的L波段頻率合成器

DDS+PLL高性能頻率合成器的設計方案

基于DDS+PLL在電臺設計中的應用

基于DDS驅動PLL結構的寬帶頻率合成器的設計與實現

DDS+PLL頻率合成技術與應用

DDS+PLL頻率合成技術與應用

評論