?

在現代科技領域,嵌入式系統接口作為信息交互的核心樞紐,扮演著不可或缺的角色。各類接口通過標準化的通信協議與規范,實現了設備間的高效數據傳輸與智能協同。作為嵌入式開發的核心技術之一,接口的深入理解與熟練運用直接決定了嵌入式系統的功能實現與性能優化。本文將以SPI(Serial Peripheral Interface)接口為切入點,詳細剖析其工作原理與技術特點,旨在為屏幕前渴望掌握嵌入式開發的小伙伴構建一個全面的接口知識體系。

一、基本概念

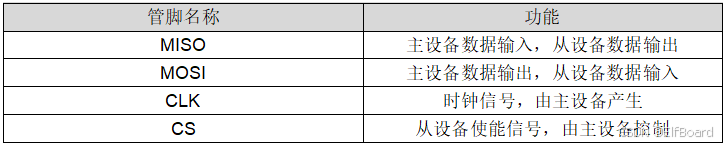

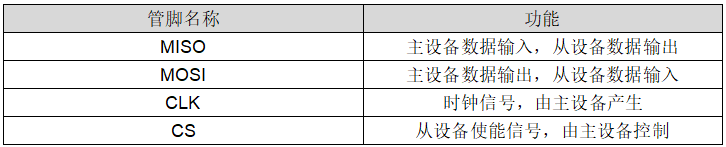

SPI的全稱是Serial Peripheral Interface,譯為串行外設接口。它是一種高速的,全雙工,同步的通信總線,廣泛應用于嵌入式系統,用于控制器和各種外圍設備之間的數據傳輸。SPI接口具有全雙工通信、傳輸速度快、協議簡單等特點,因此在許多需要高效率、短距離的通信場景中使用。SPI接口經常被稱為4線串行總線,以主/從方式工作,數據傳輸過程由主機初始化。4條線號線如下:

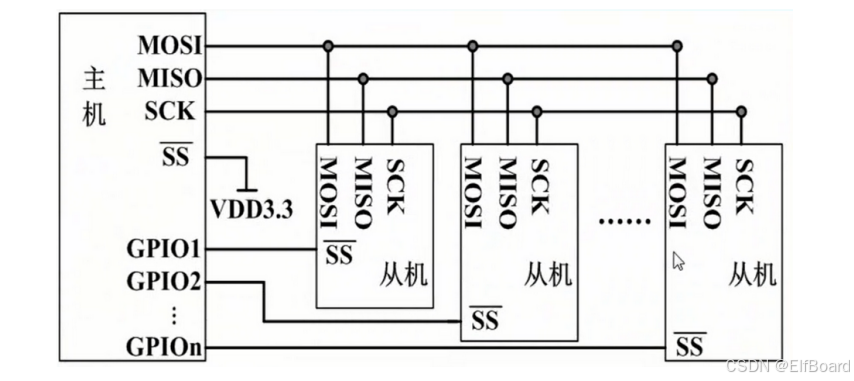

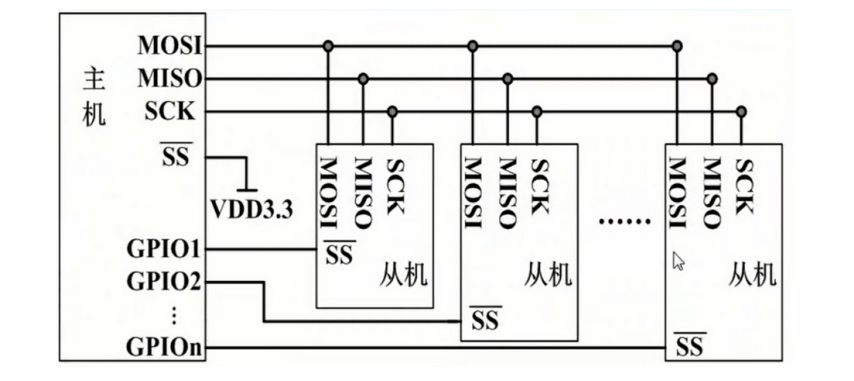

SPI采用主從模式,通常由一個主設備(Microcontroller等控制器)和一個或多個從設備組成。

在通信過程中,由主設備來控制從設備,主設備負責生成時鐘信號,通過SCK引腳提供給從設備,用于同步數據傳輸。主設備通過MOSI向從設備發送數據,同時通過MISO從從設備接收數據,數據傳輸是雙向的。

在SPI總線上,當一個主機和多個從機進行通訊時,主設備使用SS信號選擇一個從設備進行通信,只有被選擇的從設備會響應主設備的指令,其余從設備則保持不響應狀態。

二、工作模式

SPI通常有四種工作模式(0、1、2、3),主要區別在于時鐘極性(CPOL)和時鐘相位(CPHA)的不同設置,決定了時鐘信號在何時進行電平翻轉和數據采樣。

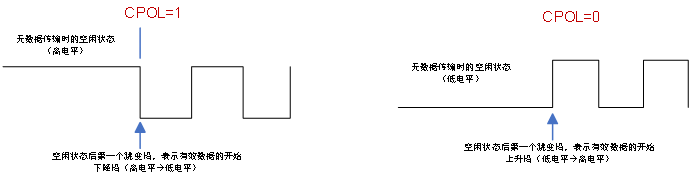

CPOL:時鐘的極性;表示SPI在空閑時,時鐘信號是高電平還是低電平。

CPHA:時鐘的相位;表示SPI設備是在SCK管腳上面的時鐘信號變為上升沿時觸發數據采樣,還是在時鐘信號變為下降沿時出發數據采樣。至于跳變沿是上升沿還是下降沿,取決于CPOL。

主設備會根據將要交換的數據來產生相應的時鐘脈沖,時鐘脈沖組成了時鐘信號,時鐘信號通過時鐘極性和時鐘相位控制著兩個SPI設備之間核實數據交換以及何時對接收到的數據進行采樣,來保證數據在兩個設備之間是同步傳輸的。SPI主設備與通信的從設備時鐘相位和極性應該一致。主設備SPI時鐘和極性的配置應該由外設決定。

CPOL跟CPHA的不同組合構成了SPI總線的四種不同模式:

模式 | CPOL | CPHA |

MODE0 | 0 | 0 |

MODE1 | 0 | 1 |

MODE2 | 1 | 0 |

MODE3 | 1 | 1 |

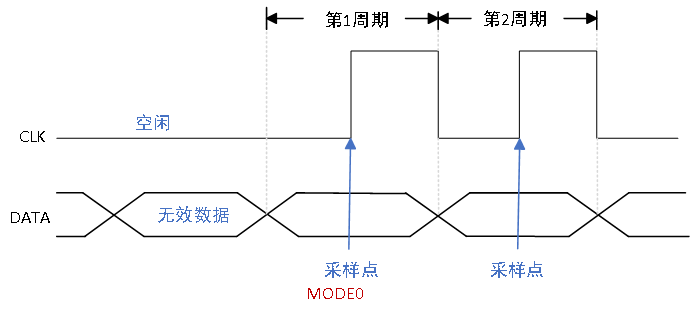

模式0(CPOL=0,CPHA=0):

CPOL=0:空閑時候為低電平,第一個跳變沿是上升沿,第二個跳變沿是下降沿。

CPHA=0:數據在第一個跳變沿(上升沿)采樣。

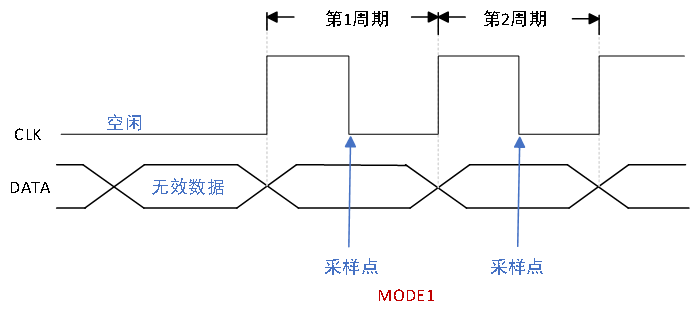

模式1(CPOL=0,CPHA=1):

CPOL=0:空閑時候為低電平,第一個跳變沿是上升沿,第二個跳變沿是下降沿。

CPHA=1:數據在第二個跳變沿(下降沿)采樣。

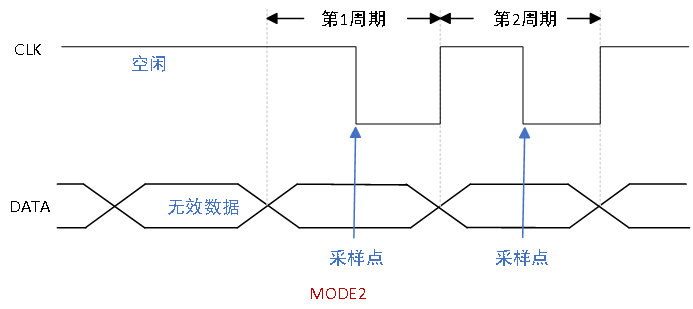

模式2(CPOL=1;CPHA=0):

CPOL=1:空閑時候為高電平,第一個跳變沿是下降沿,第二個跳變沿是上升沿。

CPHA=0:數據在第一個跳變沿(下降沿)采樣。

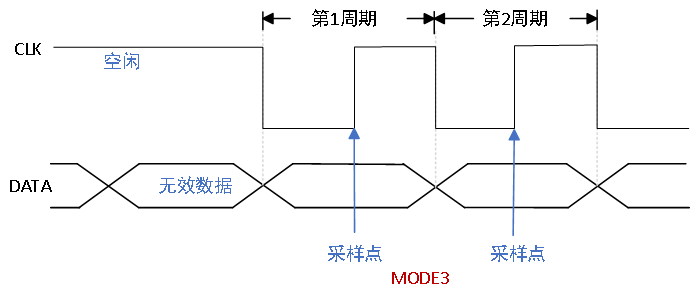

模式3(CPOL=1;CPHA=1):

CPOL=1:空閑時候為高電平,第一個跳變沿是下降沿,第二個跳變沿是上升沿。

CPHA=1:數據在第二個跳變沿(上升沿)采樣。

關于SPI接口就介紹到這里,衷心希望這些內容能為屏幕前努力學習嵌入式開發的小伙伴帶來實質性的幫助與啟發。

?

-

單片機

+關注

關注

6067文章

44969瀏覽量

649752 -

嵌入式

+關注

關注

5148文章

19640瀏覽量

316911 -

嵌入式芯片

+關注

關注

4文章

236瀏覽量

28018 -

開發板

+關注

關注

25文章

5654瀏覽量

104174

發布評論請先 登錄

嵌入式教育科普|I2C接口全面解析

ElfBoard嵌入式教育科普|CAN接口全面解析

嵌入式硬件通信接口協議中的串行通信接口-SPI

嵌入式系統的全面解析

嵌入式硬件通信接口協議-SPI(一)協議基礎

嵌入式主板是什么意思?嵌入式主板全面解析

ElfBoard嵌入式教育科普|UART接口全面解析

嵌入式教育科普|SPI接口全面解析

嵌入式教育科普|SPI接口全面解析

評論