來源:漫談大千世界

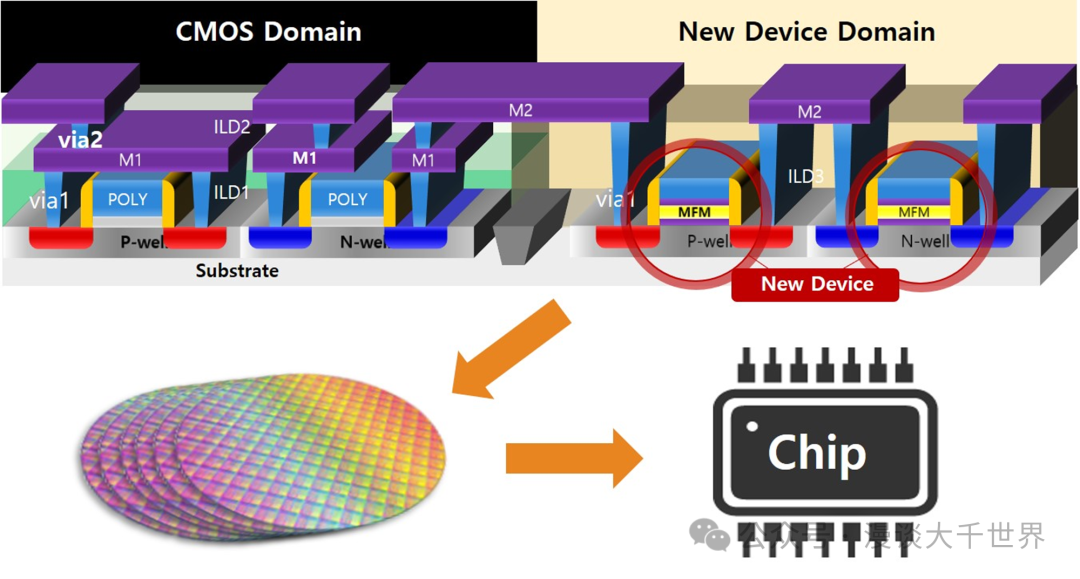

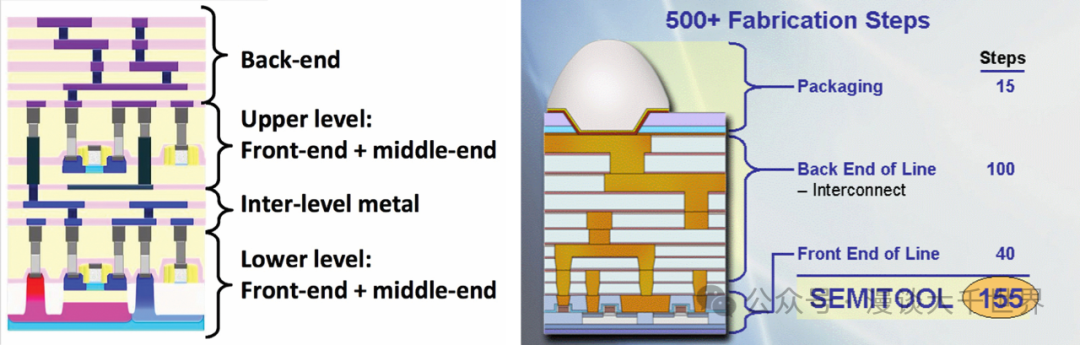

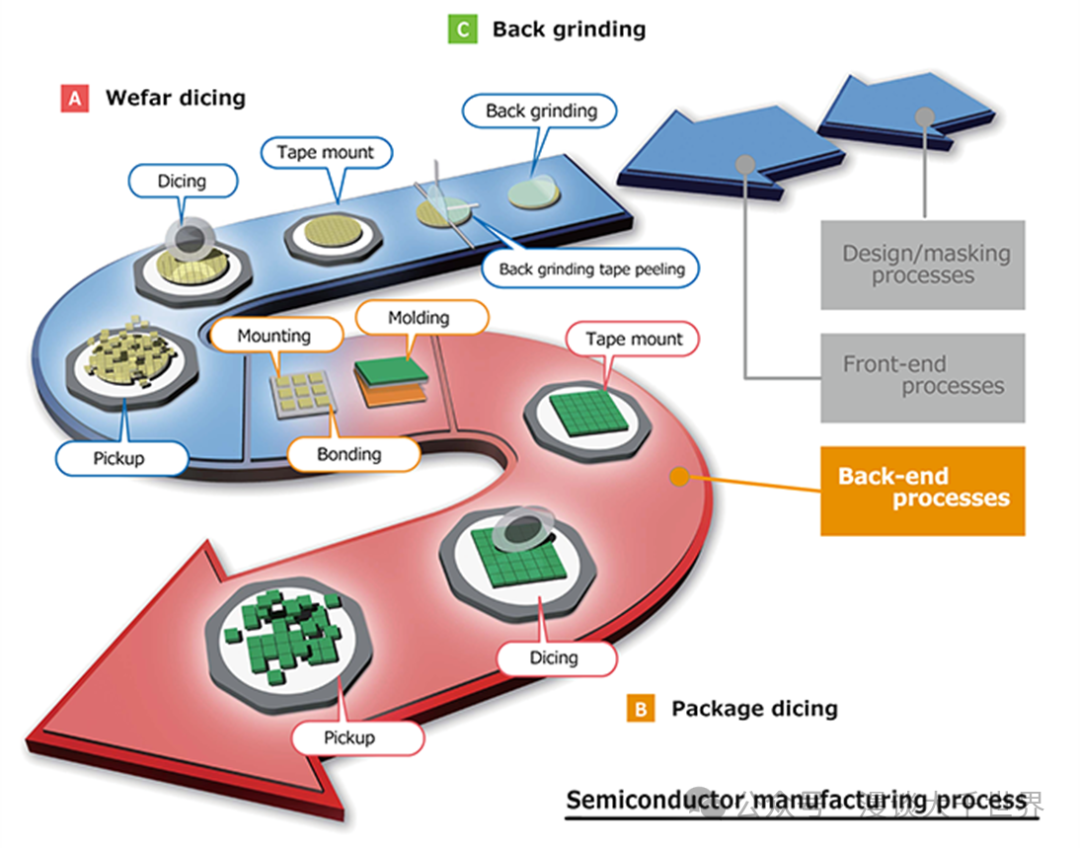

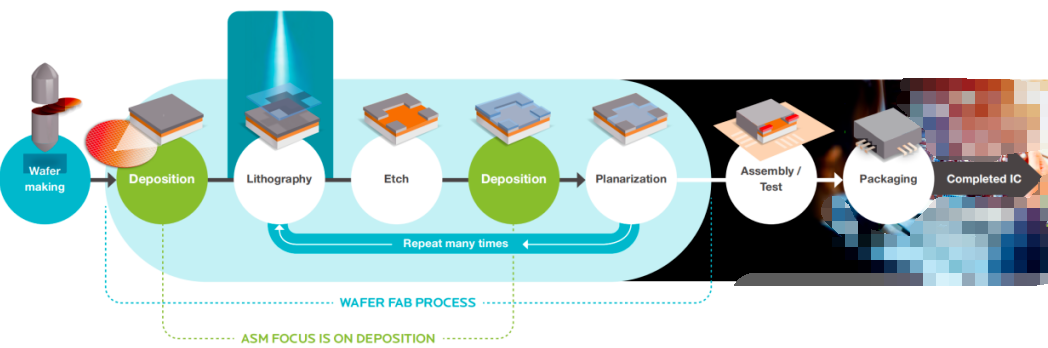

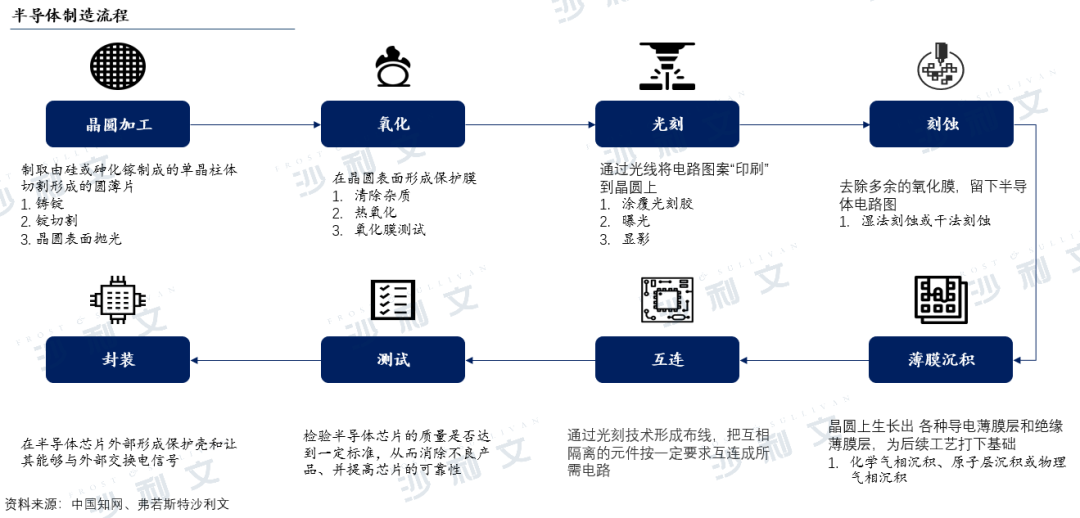

前段工藝(Front-End)、中段工藝(Middle-End)和后段工藝(Back-End)是半導體制造過程中的三個主要階段,它們在制造過程中扮演著不同的角色。

前段工藝(Front-End)主要關注晶體管的制造;中段工藝(Middle-End)則側重于連接晶體管與金屬互連,起到承上啟下的關鍵作用;后段工藝(Back-End)主要負責構建金屬互連層,實現芯片內部各晶體管之間的電氣連接。

芯片制造的三個階段形成了精密的技術鏈條,前段的器件性能、中段的界面質量和后段的互連效率共同決定了芯片的PPA(功耗、性能、面積)特性。

1. 前段工藝(FEOL: Front-End-of-Line)

1.1 核心任務

在硅晶圓上構建晶體管等基礎器件,為后續的互連和封裝奠定基礎。這一階段的精度和質量直接影響到芯片的性能和功耗。

1.2 關鍵技術

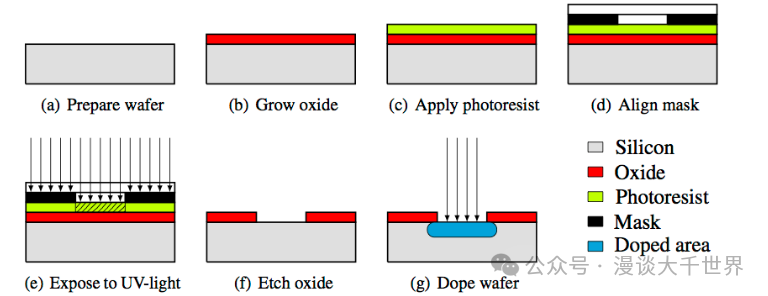

襯底制備

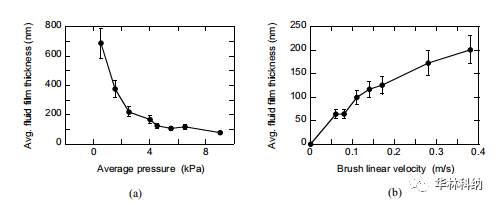

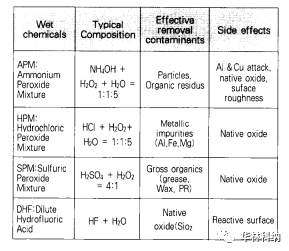

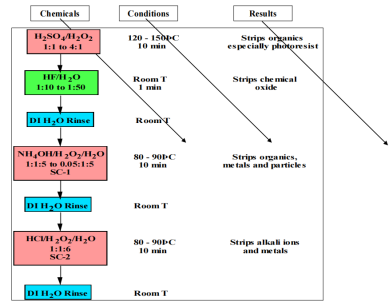

硅片拋光和清洗:通過化學機械拋光(CMP)和多級清洗工藝,消除硅片表面的劃痕、顆粒污染物和有機殘留,確保表面粗糙度小于0.1nm,為后續外延生長提供完美界面。

外延生長(Epitaxy):采用化學氣相沉積(CVD)技術,在硅片表面原子級平整的基礎上,生長出高質量的半導體層,如Si/SiGe,厚度可精確控制在10nm~10μm范圍內,用于構建FinFET的鰭式結構或GAA晶體管的溝道層。

器件成型

光刻與刻蝕:利用極紫外光刻(EUV)技術,其波長為13.5nm,能夠定義納米級甚至亞納米級的圖形。例如,在FinFET工藝中,通過EUV光刻將設計好的鰭式結構圖案轉移到光刻膠層,隨后采用反應離子刻蝕(RIE)技術,將圖案精確轉移到硅襯底,形成高度約50nm、寬度約7nm的鰭式結構,線寬粗糙度(LWR)控制在<1nm。

離子注入:使用高能離子注入機,將摻雜離子(如硼、磷、砷等)以精確的能量和劑量注入硅片特定區域,形成源極(Source)、漏極(Drain)和閾值電壓調整區。例如,在先進節點中,為了實現原子級摻雜均勻性,采用多重離子注入工藝,結合低溫注入和快速熱退火(RTP),確保摻雜原子的精確分布,形成陡峭的摻雜剖面,源漏延伸區的摻雜濃度梯度可達到1×102? atoms/cm3/nm。

柵極堆疊:采用高k介質(如HfO?,k值約為20~25)結合金屬柵(RMG)工藝,降低漏電流。例如,在3nm節點的FinFET器件中,高k介質層厚度約為1nm,金屬柵材料采用TiN/TaC/TiAl等多層結構,通過原子層沉積(ALD)技術實現高k介質的均勻生長和金屬柵的精確填充,有效降低柵極漏電流至1×10?1?A以下。

高溫工藝

快速熱退火(RTP):在氮氣或氬氣氛圍下,利用鹵素燈或激光作為熱源,將硅片迅速加熱至1000℃~1300℃,并在幾秒到幾十秒內完成摻雜原子的激活和損傷修復,確保源漏區的摻雜激活率大于95%。

氧化/氮化硅沉積:采用熱氧化或等離子體增強化學氣相沉積(PECVD)技術,在硅片表面形成氧化硅或氮化硅薄膜,厚度約為5nm~50nm,用于形成側墻(Spacer),保護柵極結構,減少短溝道效應。

1.3 技術挑戰

3nm以下節點的短溝道效應控制:隨著器件尺寸縮小至3nm以下,短溝道效應愈發嚴重,導致漏電流增大和閾值電壓難以控制。例如,在3nm節點的FinFET器件中,由于鰭寬和鰭高尺寸的縮小,縱向和橫向的電場耦合增強,使得漏電流增加至1×10??A以上。為解決這一問題,需要采用新型器件結構如GAA(環繞柵極)晶體管和CFET(互補FET),通過全包圍柵極控制溝道電勢,有效抑制短溝道效應,將漏電流降低至1×10?12A以下。

原子級摻雜均勻性:在先進節點中,源漏區的摻雜濃度需要達到1×102? atoms/cm3以上,且摻雜剖面的均勻性要求在±5%以內。例如,在FinFET器件的源漏延伸區,需要實現精準的SD摻雜剖面,即從源漏主區到溝道區的摻雜濃度逐漸降低,形成陡峭的摻雜梯度,以減少結深和漏電流。目前,通過多重離子注入和低溫注入技術,結合精確的熱處理工藝,能夠實現原子級摻雜均勻性,但仍然面臨摻雜濃度波動和雜質聚集等問題。

EUV多重曝光套刻精度:為了實現更高分辨率的圖形轉移,EUV多重曝光技術應運而生。例如,在5nm節點及以下工藝中,通常需要進行24次EUV曝光,每次曝光的套刻精度要求在<1nm范圍內。然而,由于EUV光刻機的光學系統復雜性和機械精度限制,以及光刻膠的敏感性和顯影工藝的影響,實際套刻精度往往在1.5nm2nm之間,導致圖形轉移誤差和器件性能波動。為提高套刻精度,需要優化光刻機的對準系統和曝光參數,同時開發新型光刻膠材料和顯影工藝,以實現Overlay < 1nm的目標。

2. 中段工藝(MEOL:Middle-End-of-Line)

2.1 核心任務

建立晶體管與金屬互連的橋梁,確保信號能夠高效、準確地在器件和互連網絡之間傳輸,對芯片的速度和功耗具有重要影響。

2.2 關鍵技術

接觸孔(Contact)制造

自對準硅化物(Salicide):在源/漏/柵極表面形成NiPtSi等低電阻接觸。例如,在FinFET工藝中,通過沉積鎳鉑合金薄膜,隨后進行快速熱退火,使鎳鉑與硅發生反應,形成低電阻的硅化物相,電阻率可降低至5μΩ·cm以下,減少接觸電阻,提高器件的開關速度。

鎢栓塞(W-Plug):采用化學氣相沉積(CVD)技術,將鎢填充到高深寬比接觸孔中,孔深與孔徑之比大于10:1。例如,在3nm節點的FinFET器件中,接觸孔直徑約為20nm,深度約為200nm,通過CVD-W工藝實現無空洞填充,確保接觸孔的導電性和可靠性。

局部互連(Local Interconnect)

沉積TiN/TaN等擴散阻擋層:在銅互連工藝中,為了防止銅原子擴散到低k介質中,采用物理氣相沉積(PVD)技術,在銅線和低k介質之間沉積TiN/TaN等擴散阻擋層,厚度約為2nm~5nm,確保阻擋層的完整性和致密性,銅原子擴散系數可降低至1×10?2?cm2/s以下。

銅雙大馬士革工藝(Dual Damascene):形成M0/M1金屬層。例如,在3nm節點的BEOL工藝中,采用銅雙大馬士革工藝,通過光刻和刻蝕技術,在低k介質中形成通孔和溝槽的雙重圖案,隨后采用電化學沉積(ECD)技術填充銅,實現M0/M1金屬層的互連,銅線寬和間距可達到15nm~20nm,電阻率約為1.7μΩ·cm。

平坦化工藝

化學機械拋光(CMP):在多層互連工藝中,為了消除表面起伏,確保光刻焦深,采用化學機械拋光技術對銅層和低k介質層進行平坦化處理。例如,在BEOL工藝中,每完成一層互連的沉積和圖案化后,都需要進行CMP工藝,將表面粗糙度控制在<0.5nm,確保后續光刻工藝的精度和質量。

2.3 技術挑戰

接觸孔電阻控制:在先進節點中,接觸孔的電阻對器件性能和功耗的影響愈發顯著。例如,在3nm節點的FinFET器件中,接觸孔電阻要求小于10Ω·μm,否則會導致源漏電流降低和器件速度減慢。為降低接觸孔電阻,需要優化自對準硅化物工藝和鎢栓塞工藝,提高硅化物的形成質量和鎢的填充密度,同時減小接觸孔的尺寸和深度比。

高深寬比結構的無空洞填充:隨著互連結構尺寸的縮小,高深寬比結構如TSV(硅通孔)的填充難度增加。例如,在3D封裝中,TSV的深寬比可達到15:1以上,直徑約為5μm10μm,深度可達50μm100μm。采用CVD-W或電鍍銅工藝進行填充時,容易出現空洞和縫隙,導致互連可靠性降低。為實現無空洞填充,需要優化工藝參數和材料選擇,例如采用新型的填充材料如鈷或釕,以及改進的填充工藝如種子層增強電鍍技術。

界面態密度優化:在互連結構中,界面態密度對電遷移和可靠性具有重要影響。例如,在銅/低k介質界面,界面態密度要求低于1×1011 cm?2eV?1,否則會加速銅原子的擴散,導致互連斷路。通過優化擴散阻擋層的沉積工藝和表面處理技術,能夠降低界面態密度,提高互連的可靠性和壽命。

3. 后段工藝(BEOL:Back-End-of-Line)

3.1 核心任務

構建多層金屬互連網絡,實現芯片內部數百萬甚至數千萬個晶體管之間的電氣連接,對芯片的性能、功耗和面積(PPA)具有決定性影響。

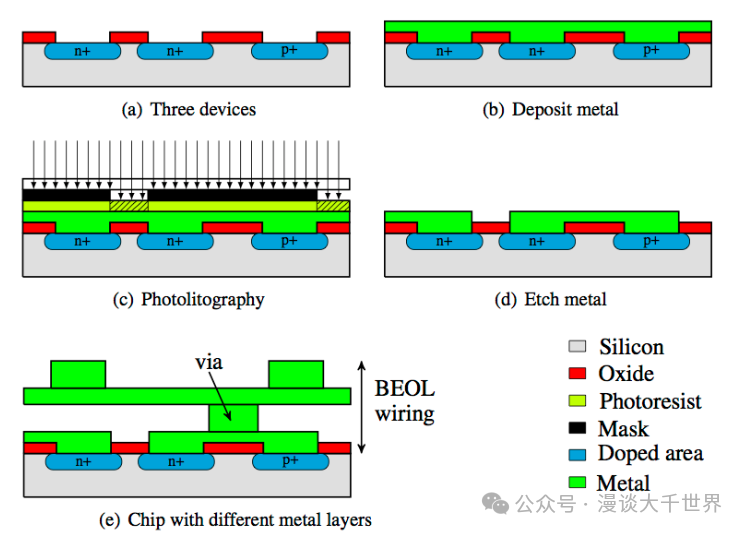

3.2 關鍵技術

互連層堆疊

低k介質(如SiCOH,k=2.4~3.0)沉積:采用化學氣相沉積(CVD)技術,在互連層之間沉積低k介質,減少寄生電容。例如,在10nm節點及以下工藝中,低k介質的厚度約為100nm~200nm,其k值的降低能夠顯著減少互連之間的電容,提高信號傳輸速度和降低功耗。

銅互連(Cu Damascene)替代傳統鋁線:銅的電阻率約為1.7μΩ·cm,比傳統鋁線(電阻率約為2.8μΩ·cm)更低,能夠降低互連電阻,提高芯片的性能和能效。例如,在14nm節點及以下工藝中,銅互連已經成為主流技術,通過銅雙大馬士革工藝實現銅線的精確填充和圖案化,銅線寬和間距可達到30nm~50nm。

多層布線

通孔(Via)與金屬線(Metal Line)的逐層構建:在BEOL工藝中,通常需要構建10層以上的金屬互連網絡。例如,在7nm節點的芯片中,金屬層數量可達12層,每層金屬線和通孔的尺寸和間距逐漸縮小,最上層金屬線寬和間距可達到1μm2μm,而最下層(M1層)金屬線寬和間距可達到20nm30nm。通過逐層的光刻、刻蝕和填充工藝,實現信號在不同層之間的傳輸和分配。

空氣隙(Air Gap)技術進一步降低k值:為了進一步降低互連之間的寄生電容,采用空氣隙技術,在互連結構之間形成真空或氣體間隙,其k值接近1。例如,在5nm節點及以下工藝中,空氣隙技術應用于局部互連和部分金屬層之間,通過優化工藝流程和材料選擇,確保空氣隙的穩定性和可靠性,減少電容達30%~50%。

封裝集成

硅通孔(TSV)實現3D堆疊:在3D封裝技術中,通過在硅片上制造TSV,實現芯片之間的垂直互連。例如,在3DNAND閃存和高端處理器的3D封裝中,TSV直徑約為5μm10μm,深度可達50μm100μm,能夠顯著減少芯片之間的互連長度,提高集成度和性能。

微凸點(Microbump)鍵合用于Chiplet集成:在Chiplet集成技術中,通過微凸點鍵合實現小芯片之間的水平互連。例如,在AMD的Ryzen系列處理器中,微凸點直徑約為10μm20μm,間距約為20μm50μm,能夠實現高密度的電氣連接,提高芯片的模塊化設計和制造靈活性。

3.3 技術挑戰

電遷移(EM)和應力遷移(SM)導致的互連可靠性問題:在高電流密度和溫度應力下,銅互連容易發生電遷移和應力遷移現象,導致互連斷路或短路。例如,在10nm節點及以下工藝中,銅互連的電流密度可達到1×10? A/cm2以上,電遷移失效時間可縮短至1×10?小時以下。為提高互連可靠性,需要優化銅互連的結構設計和材料選擇,例如采用新型的阻擋層材料如鈷或釕,以及改進的互連工藝如空氣隙技術和應力緩沖層沉積。

超低k介質機械強度不足:隨著k值的降低,低k介質的機械強度也相應降低,容易在后續的CMP和封裝工藝中出現劃傷和破裂。例如,超低k介質(k<2.0)的楊氏模量通常低于5GPa,而在CMP工藝中,拋光墊的壓力可達到10kPa~50kPa,容易導致低k介質層的損傷。為提高低k介質的機械強度,需要開發新型的低k介質材料和加固工藝,例如采用多孔結構優化和表面涂層技術。

多層布線中的RC延遲優化:在多層互連網絡中,互連的電阻(R)和電容(C)會導致信號傳輸延遲,影響芯片的性能。例如,在14nm節點的芯片中,互連的RC延遲占總信號延遲的50%以上。為優化RC延遲,需要采用低電阻的互連材料如銅和低k介質,同時優化互連的布線拓撲結構和層次設計,例如采用RDL(重分布層)技術重新分配互連網絡,減少互連長度和交叉電容。

4. 工藝演進

4.1 先進技術

前段:GAA(環繞柵極)晶體管、CFET(互補FET)

GAA晶體管:通過全包圍柵極結構,有效控制溝道電勢,抑制短溝道效應,適用于3nm及以下節點。例如,在三星的3nm GAA工藝中,采用納米線或納米片作為溝道材料,溝道長度可縮小至1nm~3nm,漏電流可降低至1×10?12A以下,同時提高器件的驅動電流和性能。

CFET(互補FET):將NMOS和PMOS器件垂直堆疊,進一步縮小芯片面積,提高集成度。例如,在IMEC的CFET研究中,通過3D集成技術將PMOS器件堆疊在NMOS器件之上,芯片面積可縮小30%~50%,同時減少互連長度和功耗。

中段:自對準通孔(Self-Aligned Via)

自對準通孔技術:通過光刻和刻蝕工藝的優化,使通孔與下方的金屬線自動對準,減少工藝偏差和接觸電阻。例如,在臺積電的N7工藝中,采用自對準通孔技術,通孔與金屬線的對準精度可達到±5nm,接觸電阻可降低至5×10?1?Ω·μm以下,提高互連的可靠性和性能。

后段:混合鍵合(Hybrid Bonding)、光互連

混合鍵合技術:結合微凸點鍵合和TSV技術,實現高密度、低延遲的3D封裝互連。例如,在蘋果的M1 Ultra芯片中,采用混合鍵合技術將兩顆M1 Max芯片無縫連接,互連帶寬可達2.5TB/s,延遲極低,相當于單顆芯片的性能。

光互連技術:利用光信號代替電信號進行長距離、高速率的數據傳輸,減少互連功耗和延遲。例如,在Intel的研究中,通過在芯片表面集成光波導和光收發器,實現芯片內部和芯片之間的光互連,傳輸速率可達100Gbps以上,功耗降低至1pJ/bit以下。

4.2 材料革新

二維材料(MoS?):具有原子級厚度和優異的電學性能,可用于構建超薄溝道器件,適用于后摩爾時代的小尺寸器件。例如,在MoS?基的晶體管中,溝道厚度可達到1nm以下,載流子遷移率可達到200cm2/V·s以上,具有低功耗和高性能的特點。

鈷互連:鈷的電阻率約為6μΩ·cm,雖然高于銅,但在小尺寸互連中具有更好的電遷移特性和與低k介質的兼容性。例如,在7nm節點及以下工藝中,鈷互連應用于最下層金屬線和接觸孔,提高互連的可靠性和工藝良率。

鉍基接觸金屬:鉍具有低電阻和良好的與硅的接觸特性,可用于替代傳統的鎳硅化物接觸,降低接觸電阻。例如,在FinFET器件中,采用鉍基接觸金屬,接觸電阻可降低至1×10?1?Ω·μm以下,提高器件的性能和能效。

-

半導體

+關注

關注

335文章

28780瀏覽量

235368 -

工藝

+關注

關注

4文章

679瀏覽量

29359 -

晶體管

+關注

關注

77文章

10005瀏覽量

141201 -

芯片制造

+關注

關注

10文章

682瀏覽量

29631

原文標題:芯片制造:FEOL、MEOL與BEOL

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

半導體制造的難點匯總

半導體制造車間的環境與生產要求以及設施規劃

盤點半導體制造工藝中的主要設備及材料

半導體制造工藝教程的詳細資料免費下載

半導體制造過程中刷洗力的研究

半導體制造過程中的新一代清洗技術

ALD是什么?半導體制造的基本流程

半導體制造三要素:晶圓、晶粒、芯片的傳奇故事

半導體制造過程中的三個主要階段

半導體制造過程中的三個主要階段

評論