NXP S32G2 硬件設計篇(上)

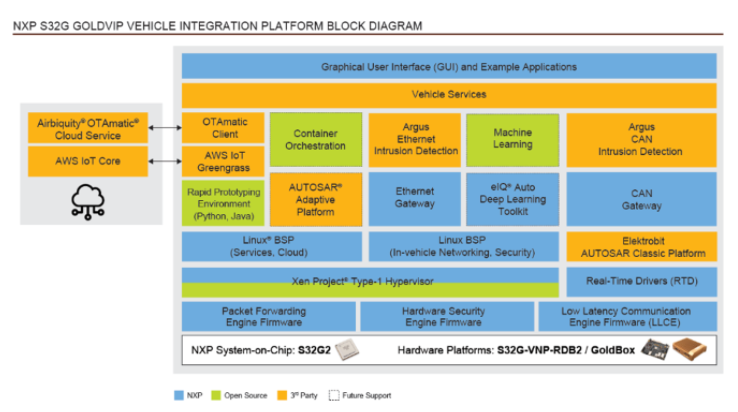

近些年,汽車電子發展日新月異,功能越來越多,對處理器性能需求也越來越高,恩智浦新推出的高性能車輛網絡處理器S32G2非常適合汽車中央網關。本文介紹了一些在S32G2硬件設計中需要注意的一些問題,包括電源設計、高速接口以及PCB Layout建議等。

為了能使客戶更快的熟悉并應用S32G2,艾睿電子和恩智浦合作對該芯片進行了深度的前期開發,即將推出方便用戶測試的開發套件SEED-S32G。

圖 開發套件SEED-S32G

電源設計

S32G2芯片需要多種電源供給,包括核電源、IO電源、Fuses電源、模擬電源等,所有電源需要保證正確的供給,包括電壓、最大電流、紋波,即使電源引腳相應功能沒有使用,也需要保證正常供給。不過如果電源引腳對應功能沒有使用的話,相關的去耦電容可以省去。

對于S32G2的電源,建議按照官方設計選用VR5510進行設計,這樣可以加快件設計,同時也可以使得軟件開發更方便,因為NXP官方SDK包提供了完整的VR5510支持。

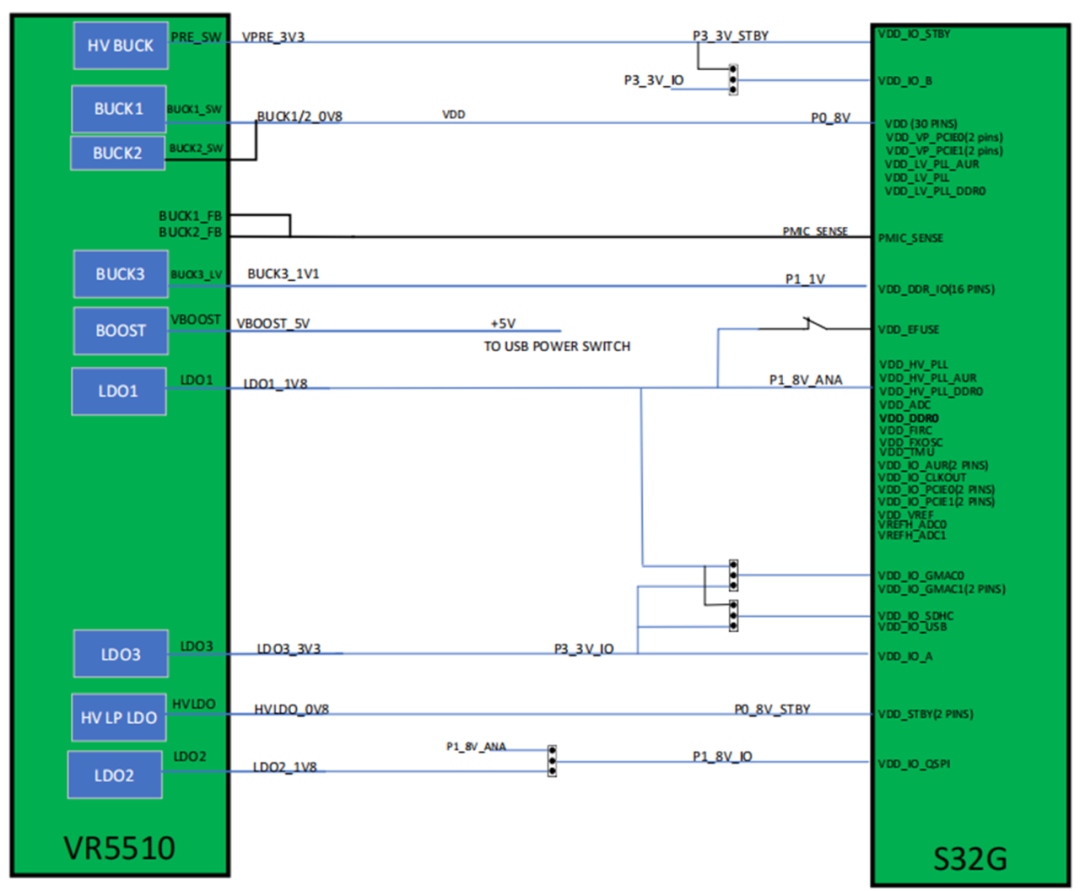

電源連接

電源連接方式建議按照下圖方式進行連接,其中部分電源有跳線選擇,客戶實際使用時可根據實際情況進行優化,確定選擇其中一種電源,省去跳線電路。

圖二

旁路模式

對于PMIC來說,有下面兩種旁路模式:

常規旁路模式:需要VPRE和HVLDO正常工作

帶LPDDR4 自刷新旁路模式:需要VPRE、HVLDO、BUCK3以及LDO2正常工作

根據不同的需求,用戶可以選擇不同連接方式。S32G的VDD_IO_B可以選擇是來自VPRE_3V3還是LDO3_3V3,其中的區別在于,在旁路模式下,VDD_IO_B是否需要供電,需要供電的話,就要連接到VPRE_3V3,如果不需要供電就要連接到LDO3_3V3。這里主要影響的是旁路模式下的功耗。由于CAN_Rx需要用于喚醒,所以處于VDD_IO_STBY電源域,但相應的CAN_Tx引腳處于VDD_IO_B電源域。

兩種不同的設計分下面兩種情況:

VDD_IO_B選擇是來自LDO3_3V3,這樣在旁路模式,CAN_Tx引腳處于不工作狀態。

VDD_IO_B選擇是來自VPRE_3V3,這種情況下,CAN_Tx引腳處于工作狀態。這種情況下,S32G2在旁路模式多了40個工作的引腳。

旁路模式下工作的引腳如果有上拉,則會有0.3uA的漏電流產生。

旁路模式下不工作的引腳如果外部不是下拉或者不驅動,將會產生額外的漏電流。可以根據實際情況選擇旁路模式是否給VDD_IO_B供電。

核電壓配置

系統上電之后需要讀一下S32G2芯片的DIE_PROCESS[1:0]寄存器,確定一下芯片的SVS模式是否有使能,如果有使能,即DIE_PROCESS[1:0] = 01b,需要把VR5510的SVS OFFSET[5:0]寄存器的值配置為 ‘0b00101’,從而將BUCK1/2_0V8的電壓值配置為0.76875V,通過這種方式來優化功耗。

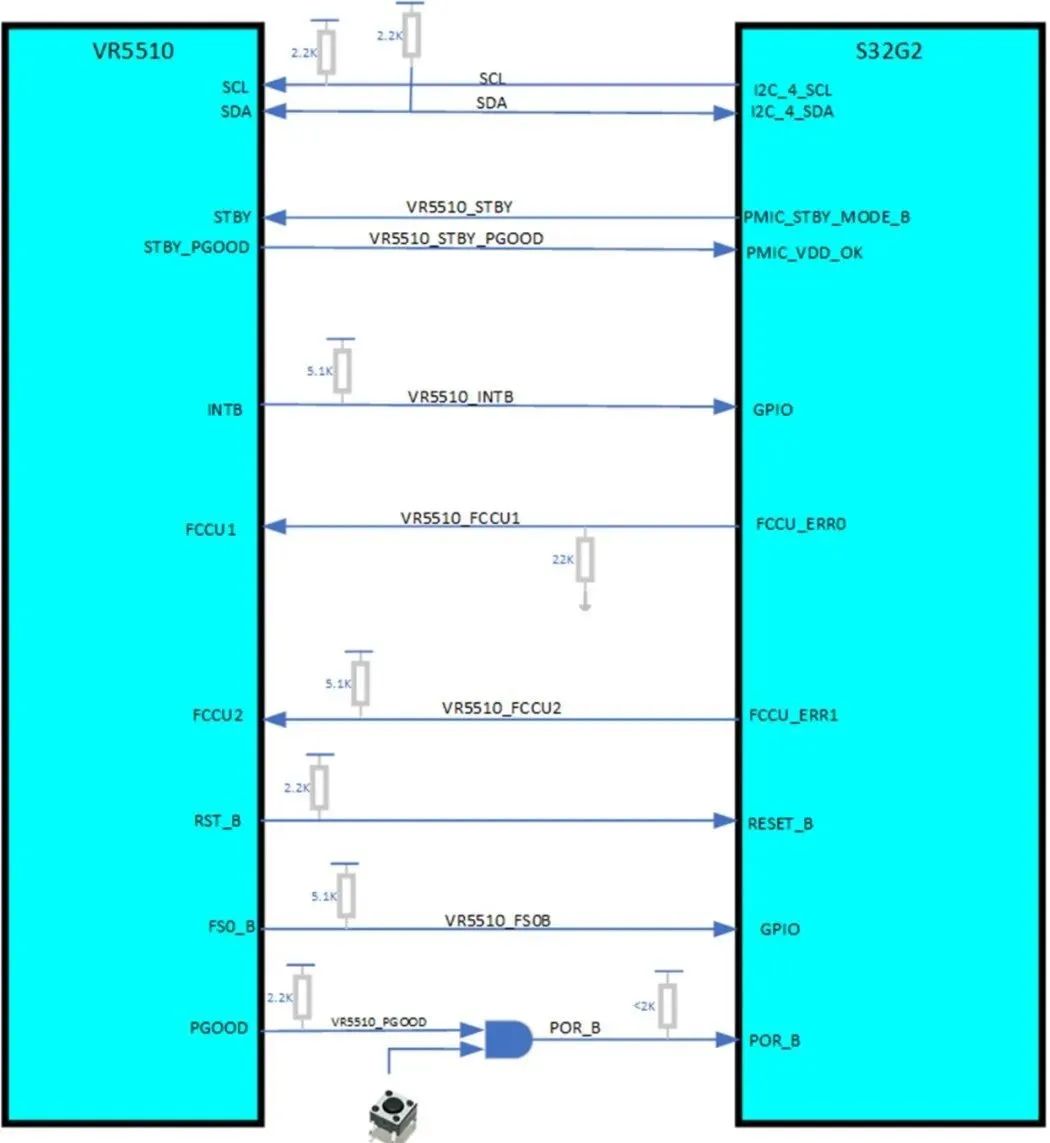

PMIC控制引腳連接

PMIC控制引腳與S32G2之間連接方式如下圖所示:

其中I2C4可以替換為其他I2C引腳,只需修改軟件配置即可。

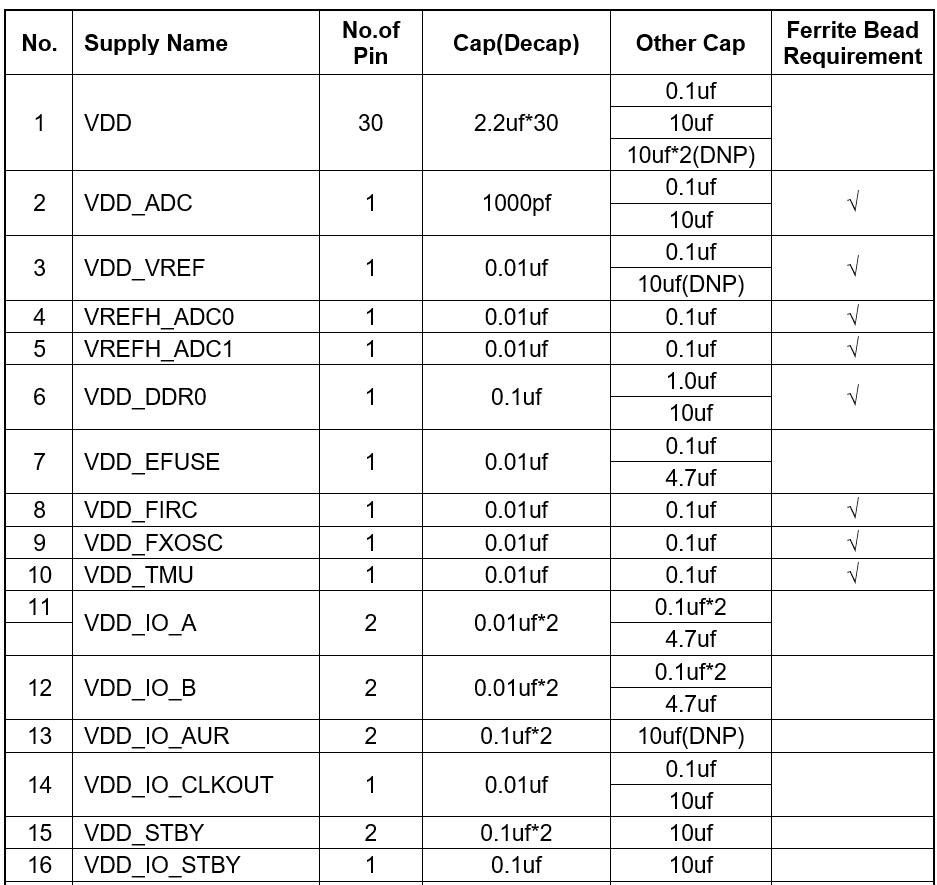

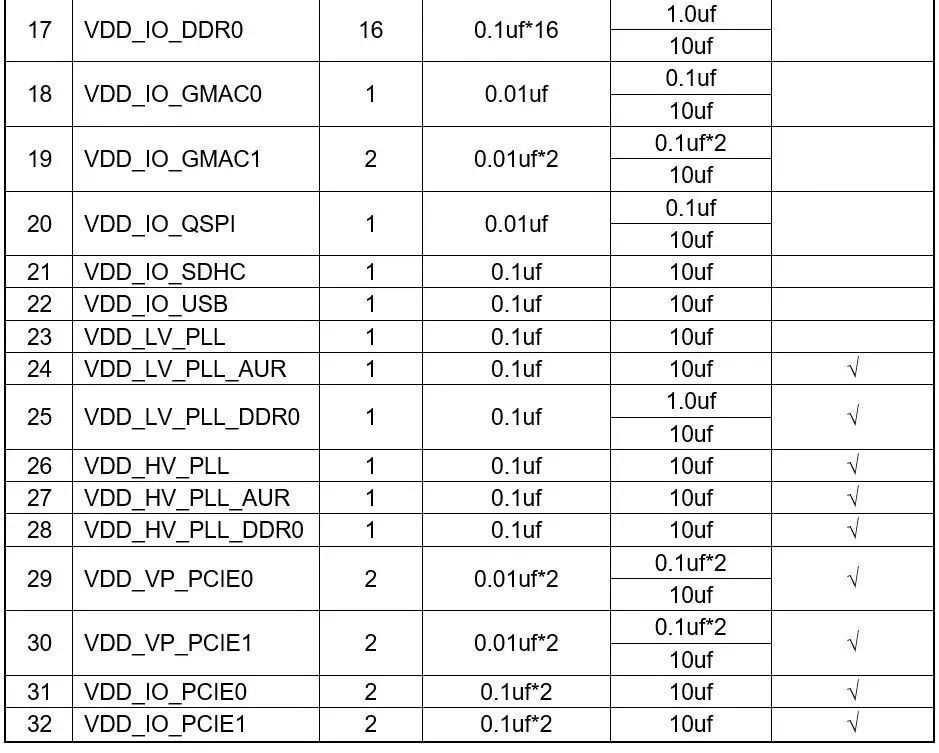

去耦及濾波電容設計

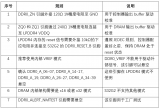

推薦按照下表進行電容選擇:

S32G2的每一個電源引腳旁邊都需要有一個去耦電容,其他電容可放置在磁珠旁。

去耦電容或者bulk電容需要距離電源過孔盡可能的近,最好不要超過50mils。其他的bulk電容可以放在BGA旁邊。去耦電容距離芯片的電源引腳距離應足夠近,這樣有助于減少等效電感,從而保證芯片所需的高速瞬態電流。

VDD_EFUSE 設計

S32G包含一個Fusebox用于存儲一次性燒寫數據。在開發或者生產階段燒寫Fuse時需要給VDD_EFUSE引腳供電,其他時間段需要連接到地。這樣可以保護Fuse被意外改寫。如果硬件不需要修改fuse,可以將VDD_EFUSE引腳直接連接到地。

RESET 設計

芯片包含兩個reset引腳,POR_B和RESET_B。

POR_B低電平有效,引腳內部包含一個弱下拉電阻。建議將改引腳連接至電源管理芯片的PGOOD引腳,并且搭配小于等于2kΩ的上拉電阻,這樣芯片上電瞬間,電源管理芯片(VR5510)會將POR_B拉低,等所有電源電壓穩定之后,電源管理芯片會釋放POR_B。工作過程中,電源管理芯片監控的電源如果有異常,就會拉低POR_B,使芯片進入reset狀態。POR_B引腳需要防止噪聲干擾,引腳旁邊可以加一個低通濾波電路。

RESET_B是一個開漏類型的雙向引腳,內部包含一個弱上拉電阻。主要用于向外輸出信號,用來指示芯片進入reset狀態。其次,在調試芯片時,該引腳也可以用于reset信號輸入。建議將RESET_B連接至電源管理芯片(VR5510)的RSTB引腳,并且外部加不大于10kΩ的上拉電阻。和POR_B引腳一樣,RESET_B也需要防止噪聲干擾,引腳旁邊可以加一個低通濾波電路。

時鐘設計

時鐘源可選下面任一種:

EXTAL和XTAL引腳之間連接一個20/24/40 MHz的晶體

連接一個40MHz的單端時鐘信號至EXTAL引腳

時鐘的PCB設計需要參照以下規則:

由于內部已經集成,外部不再需要添加反饋電阻。

時鐘電路越短越好。

VSS _FXOSC引腳直連到地平面。

PCB上的高頻信號以及噪聲敏感信號遠離時鐘電路。

S32G2 XTAL引腳旁的VSS引腳需要直連到地平面,并且和最近的VDD引腳之間需要通過電容連接。晶振兩端需要放置電容,然后將電容直連地平面。

晶振周圍可以在頂面放一圈地信號線來隔離噪聲。

晶振下面放一塊完整的地平面。

Boot 配置

Boot 相關引腳:

RESET_B釋放時,BOOTMOD[0] (PA_02) 和 BOOTMOD[1] (PA_03)的電平狀態會決定S32G2 的boot模式,RESET_B為低時,這兩個引腳電平需要保持穩定。

BOOTMOD[0/1]引腳建議用1kΩ電阻上拉。

啟動時,BOOTROM通過BOOTMOD和RCON引腳電平來決定不同的boot配置,這些引腳都是功能復用的引腳,啟動之后都要用作其他功能。但是有些引腳,比如I2C功能的引腳使用時必須有上拉電阻,但是如果啟動需要配置成低電平,這樣就會有沖突,因此在開發板中增加了一個MAX4886ETO+芯片用于功能選擇。等到產品量產階段,可以通過燒寫fuse來設置boot配置,MAX4886ETO+芯片就可以省去。

在開發階段,啟動配置BOOT_CFG有兩個方法進行配置:從EEPROM讀或者從32個GPIO RCON引腳讀。

從EEPROM讀取boot啟動配置:

如果RCON8/PB_01引腳在RESET_B上升沿是高電平,boot配置會從EEPROM讀取,這時,RCON7/PB_00會用作SDA,RCON8/PB_01會用作SCL。

EEPROM的I2C 地址需要設置為0xA0。

S32G2 會從EEPROM的0x0地址讀前4byte的數據來配置RCON。數據格式為小端。需要按照RCON7-0 、RCON15-8、RCON23-16、RCON31-24的順序存放數據。

當使用EEPROM作為RCON數據存放地址時,還需要燒寫EEPROM用于S32G2的啟動。

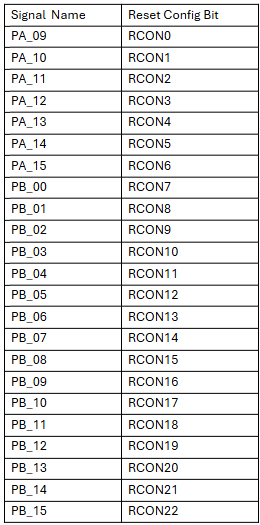

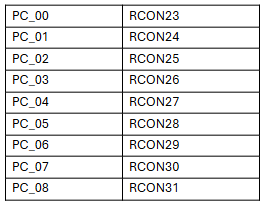

從GPIO讀取boot啟動配置:

Boot配置也可以在RESET_B上升沿從GPIO讀取,需要通過外部的上下拉電阻來進行配置。GPIO RCON引腳如下表所示:

Debug 接口

S32G2包括一個標準JTAG接口和高速Aurora調試接口。

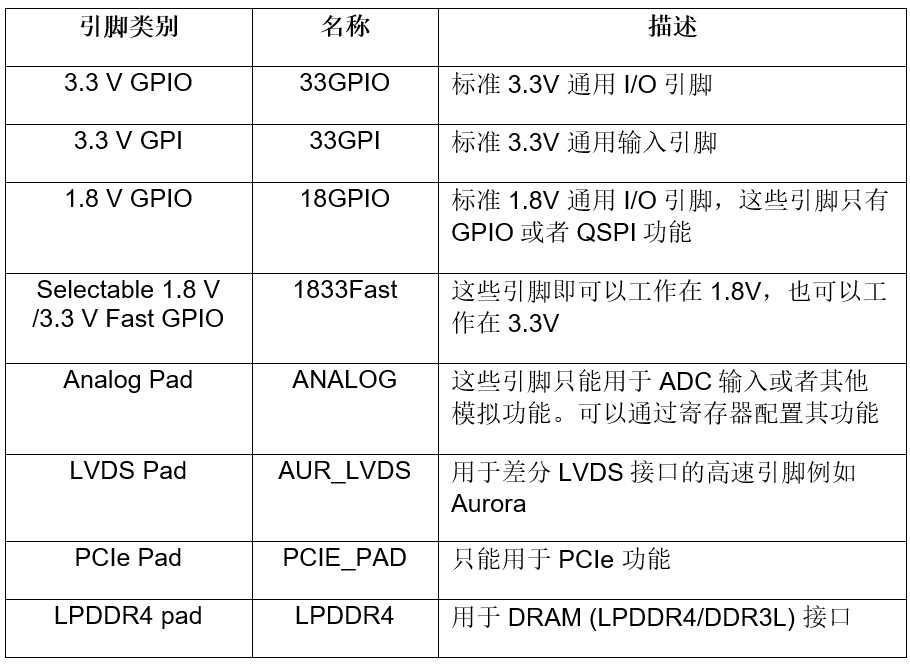

Input/Output 引腳

下表總結了S32G2的引腳類型

引腳復用

S32G2的多數引腳都可以用作多種功能。可以通過軟件選擇配置為哪種功能,詳細功能可參考S32G2用戶手冊附件的IOMUX文件。

注入電流

所有的引腳都內置了保護二極管。一些應用中,數字和模擬引腳都有可能連接到高于工作電平的電壓,比如由于不同器件或者不同板卡上電順序的原因。這種情況下,只要是器件是斷電的,就可以支持電流注入。不過等到上電之后,用戶還是需要保證引腳工作電平不要超過最高限值。

引腳外部可以增加額外的高速ESD保護器件。

未使用引腳

未使用的可以懸空,軟件配置成輸入以及禁用輸出buffer,(SIUL2 MSCR bits OBE and IBE =0) 、內部上拉使能 (PUE = 1)

CLKOUT_P、CLKOUT_N、 POST_AN是NXP內部測試引腳,需要懸空

TMU_ANODE以及TMU_CATHODE,接地。如果實際情況不方便實現,可以懸空。

所有未使用的ADC輸入需要下拉到地

S32G2 仿真模型

下面幾種模型可直接從NXP官網下載并用于仿真:

IBIS Model

BSDL Model

DDR S-parameters Model

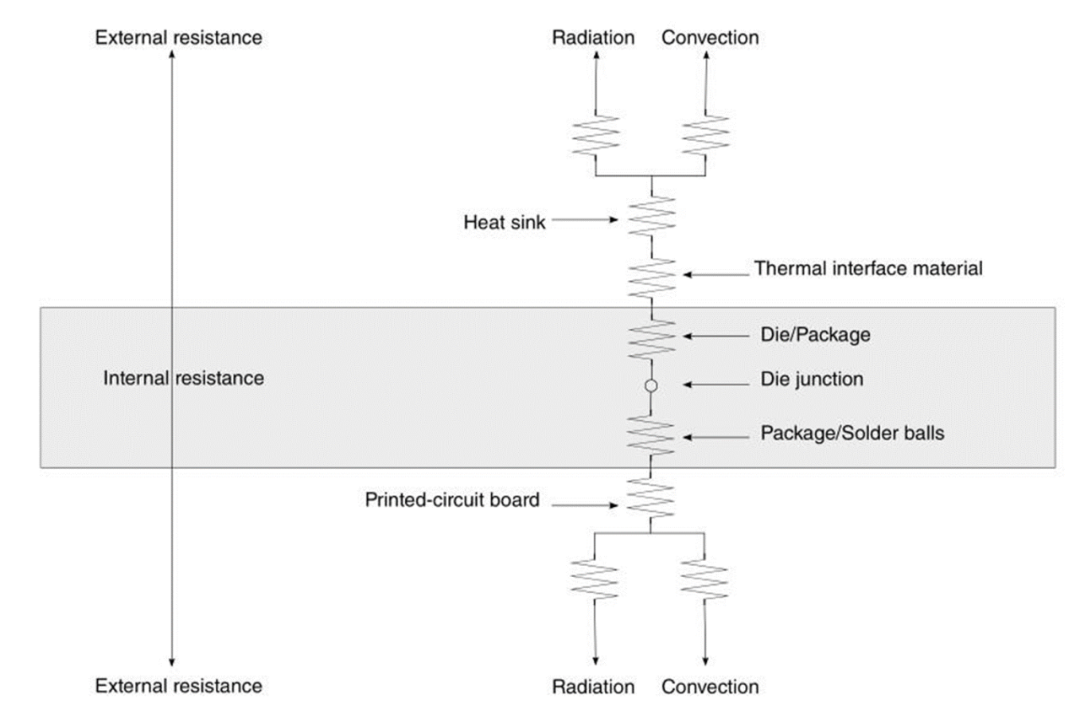

S32G2 散熱

散熱管理需要綜合考慮各種因素。可以通過熱仿真來分析系統的散熱性能。最常用的散熱方式是散熱片,直接貼裝于S32G2上即可。散熱設計需要考慮下面幾個方面:

保證留給散熱片足夠的空間

溫度敏感器件不要放置在散熱片下

注意散熱片槽的方向,保證熱空氣快速流走

S32G2導熱路徑路徑如下圖所示,大部分的熱量都通過散熱片發散。

S32G2 布板布線設計

NXP 官方開發板使用Allegro設計。用戶如果使用其他工具的話,可以進行格式轉換,不過需要注意,轉換完成之后,可能會出現部分錯誤,需要手動調整。

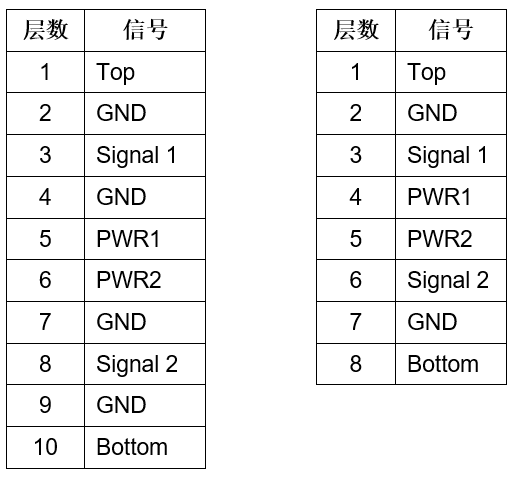

層疊設置

由于S32G2 引腳比較多,推薦至少8層板設計,層疊設置對于高速信號的質量比較關鍵,高速信號需要有臨近的參考平面來減少串擾。下面兩種層疊設置可供用戶參考。

高速信號走線設計:

優先走高速信號

走線做需要的阻抗控制

高速信號不要穿過參考平面間隙

高速信號過孔旁放置地過孔

晶體下面放置地平面

同步信號接口走線做合適的等長

PCB材質

PCB材質通常需要關注兩個參數:介電常數和介質損耗因子。選材時最好選適合高頻應用的材料。介電常數一般來說會隨著信號頻率的提高而降低。而高頻材料在一個很寬的頻率范圍(100MHz~幾GHz)都有相對穩定的介電常數以及相對較低介質損耗因子。介質損耗因子越低,信號功率損耗越低。

通常來說,FR4板材介質損耗因子會在0.02-0.01之間,而高速板材介質損耗因子會在0.009-0.002之間。FR4板材介電常數會在4.2-4.5之間,高速板材介電常數會在3.7-3.3之間如何通過layout降低PCB板材對信號完整性造成的影響?

信號線盡可能短,高速信號線層緊挨其參考平面,地平面緊挨電源平面,如果可以的話,高速信號盡量走頂層和底層,因為頂層和底層比內層有更低的傳輸延遲。

新板卡首次上電

這部分內容介紹一下,新板卡第一次上電注意事項。

首先,意外的大電流會損壞板卡,上電之前先用萬用表測量各個電源對地阻抗,看是否有短路情況。第一次上電盡量使用帶限流功能的電源,并觀察實時電流。

上電之后首先測量所有電源是否在正常范圍,防止出現過高電壓損壞器件。運行一個大負載程序,然后再測量一次所有電源是否正常。

如果有啟動問題需要確認下面幾個問題:

確認POR_B信號在所有電壓都正常之前一直處于拉低狀態

POR_B拉高之前保證EXTAL/XTAL引腳晶振或者晶體正常工作

各個電源符合datasheet上電時序的要求

以上是S32G硬件設計中關于電源、時鐘、啟動、布局布線等一些設計注意事項,下一篇文章我們將介紹關于S32G2 Memory 以及高速接口的設計。

-

處理器

+關注

關注

68文章

19882瀏覽量

234933 -

NXP

+關注

關注

61文章

1346瀏覽量

189195 -

汽車電子

+關注

關注

3037文章

8340瀏覽量

170080 -

恩智浦

+關注

關注

14文章

5978瀏覽量

116203 -

網關

+關注

關注

9文章

5641瀏覽量

52908

原文標題:【艾睿方案】NXP S32G2 硬件設計篇(上)

文章出處:【微信號:艾睿電子,微信公眾號:艾睿電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

使用實時處理器擴展恩智浦S32汽車平臺的意義

安富利基于恩智浦S32G汽車網絡處理器開發的eVTOL飛控系統解決方案

NXP推出全新S32G車輛網絡處理器,可簡化軟件復雜性提高安全性

恩智浦加速量產S32R41高性能雷達處理器

新型S32G汽車網絡處理器的主要角色將是面向服務的網關

恩智浦半導體推出了全新的S32G車輛網絡處理器

新思科技針對 S32G 車輛網絡處理器推出 VDK軟件產品

恩智浦擴展S32G網絡處理器系列以提升軟件定義汽車應用的性能

S32G2是NXP一款車規級高性能車輛網絡處理器系列

智慧加持!恩智浦S32G賦能零跑全新【四葉草】電子電氣架構

恩智浦宣布推出全新的S32N系列車輛超級集成處理器

恩智浦車輛網絡處理器S32G硬件設計(上)

恩智浦車輛網絡處理器S32G硬件設計(上)

評論