NXP S32G2 硬件設計篇(下)

接 NXP S32G2 硬件設計篇(上),下篇里我們將介紹關于 S32G2 的 Memory 以及高速接口的設計。

S32G2既可以外接LPDDR4也可以外接DDR3L。如果不使用外部DRAM,相關引腳可以懸空。(需注意S32G234M不支持DRAM接口)。

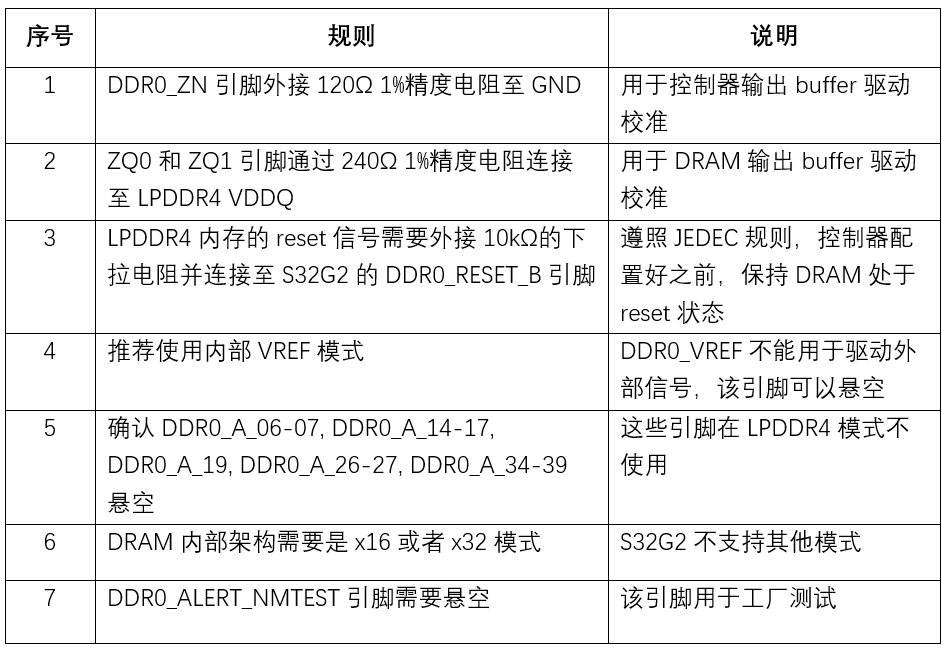

如果外接LPDDR4,需要按照下表規則:

數據線調序

在PCB layout 時,有時為了方便走線,需要調整接線方式,調整時需要按照如下要求:

首先,在LPDDR4系統中,信號按照下列方式分組

Channel A: Byte0 and Byte1, CA_A[5:0], CKE0_A, CKE1_A, CS0_A, CS1_A

Channel B: Byte2 and Byte3, CA_B[5:0], CKE0_B, CKE1_B, CS0_B, CS1_B

其中每組Byte內部的數據線,可以在組內隨意調換位置;

一個channel內的Byte 直接可以整體調換(如Byte0可以和Byte1整體調換,但是Byte0和Byte3不可以調換)。

LPDDR4 Layout規則

同一組的DQ信號需要在相同的層。

DQ信號線上有過孔的話,過孔旁邊可以放置地過孔,提高屏蔽能力以及保持阻抗連續

所有信號阻抗都到參考地平面。

走線不要經過分割的平面。

單端信號線阻抗設計為40 Ohm (+/-10%),差分信號線阻抗設計為80 Ohm (+/-10%)

信號線間距至少2倍于信號線到參考平面的距離,不同組之間的信號線間距以及到差分線的間距最好保持至少3倍。保持足夠的距離只參考平面邊緣。

信號線上盡量少的使用過孔,單根信號線最好不要超過2個。同組信號線保持相同的過孔數。在做等長計算時,過孔長度也需要考慮進去。

最大走線長度和拓撲結構、驅動能力、終端等都有關系。

地平面需要提供低阻抗的返回路徑。

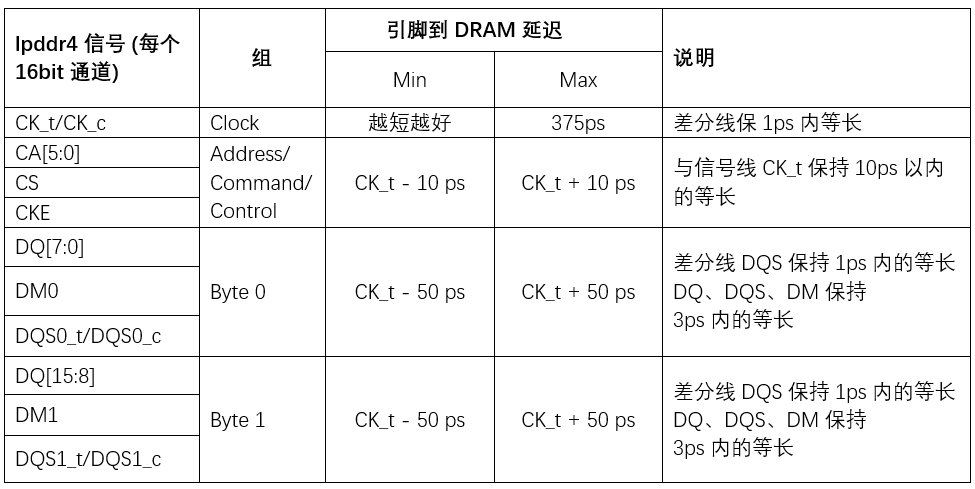

走線規則按照下表要求

當使用DDR3L時需要按照下面規則

數據線調序

和LPDDR4類似,在PCB layout 時,有時為了方便走線,也可以調整接線方式,調整時需要按照如下要求:

每組Byte內部的數據線,可以在組內隨意調換位置

一個channel內的Byte 直接可以整體調換

DDR3L Layout 規則

DDR3L layout時需要遵照下面規則:

VREF_DDR以粗線的方式進行走線

CK/CK#需要按點對點的方式從控制器走到DRAM,并且等長。單端信號線阻抗控制為50Ω,差分線阻抗控制為100Ω

ADD/CMD 需要按照T型拓撲走線,并且在末端通過40Ω的終端電阻連接至VTT。

ADD/CMD 阻抗在終端電阻之前控制為40Ω,終端電阻之后控制為50Ω,T型拓撲的分叉點需要盡可能靠近DRAM。

同組數據線保持等長,并盡量在同一層走線,單端信號線阻抗控制為50Ω,差分線阻抗控制為100Ω。

QSPI

QuadSPI 接口可以外接一個或者兩個外部flash(通過QSPI A 和QSPI B接口),每個都支持8位雙向數據線。

QSPI_A只支持1.8V,QSPI_B支持1.8V或者3.3V。QSPI_B和SDHC接口復用相同的引腳。對于1.8V的QSPI flash設備,如果有連接RESET_B,則需要一個電平轉換芯片,因為S32G2的RESET_B是3.3V的電平信號。

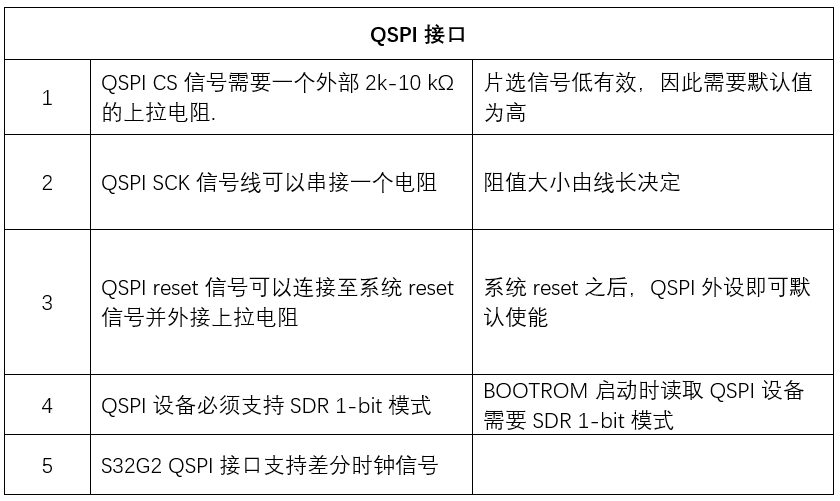

QSPI設計指導

QSPI Layout 規則

DQ信號線(包括RWDS)最大線長和負載容值相關

總的負載容值需要小于15pf,總容值包含以下幾種:

走線電容(FR4板材大約3.3pf/inch)

器件封裝引腳電容

和過孔相關的寄生電容

所有走線需要做+/- 50 mils 以內的等長

以太網設計有以下設計建議:

RGMII信號走線時需要按照下面規格:

Tx信號組合Tx信號組分別置于相同層

走線避免90度拐角

MAC到PHY走線長度不超過3 英寸

走線間距大于等于3倍線寬

所有 TX、TXCLK、RX、RXCLK信號做到組內+/-50 mil的等長

RJ45金屬外殼連到機殼地,從而減少EMI

MDI信號線對按照差分方式走線

SerDes

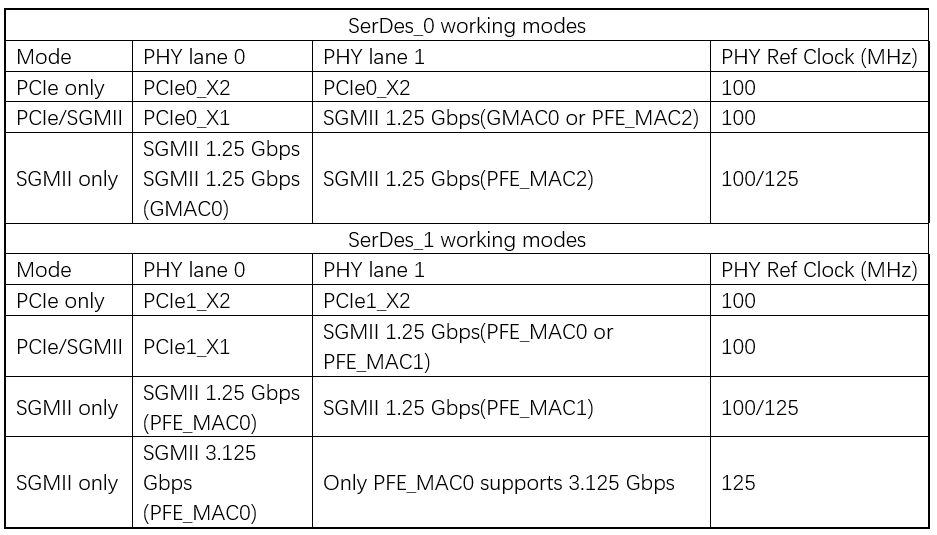

S32G2有兩個SerDes接口,每個都可以配置為PCIe或者SGMII。S32G234M上只支持PCIe_0。下表展示了可選的SerDes配置方式:

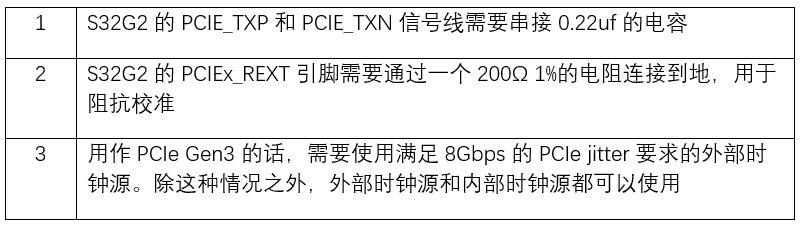

PCIe 設計推薦按照下面規則:

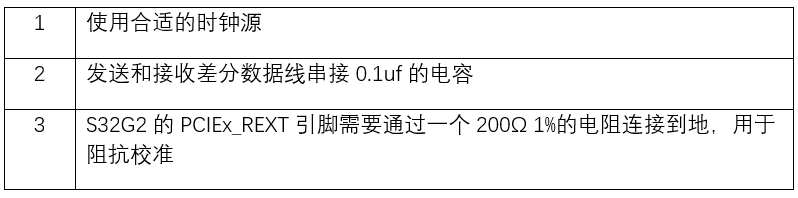

SGMII 設計推薦按照下面規則:

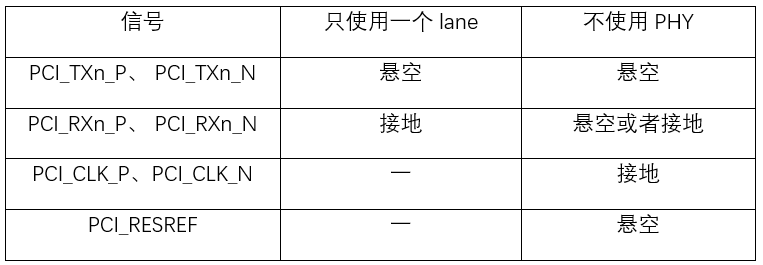

未使用引腳設計

SerDes布線按照下面規則:

走線參考平面需要連續,不要經過平面分割槽,放置連接器時,保證地平面包圍每個引腳

PCIEx_REXT信號走線盡可能短

差分信號線不要走晶振下面,也不要平行于時鐘走線以及數據信號線

差分線設計為100Ω 阻抗,并盡可能短

線寬和間距在整個走線過程中不要改變

差分線對的長度差距在5mil內

差分線兩根線過孔數量及規格保持一致,并且過孔對旁邊放置距離相等的地過孔

USB-ULPI

USBOTG符合USB2.0協議,可以作為主設備、從設備或者OTG設備。速度支持HS、full-speed(FS) 和 low-speed(LS),S32G234M不支持USB-ULPI。

-

處理器

+關注

關注

68文章

19740瀏覽量

232879 -

以太網

+關注

關注

40文章

5547瀏覽量

174193 -

恩智浦

+關注

關注

14文章

5930瀏覽量

111692

原文標題:【艾睿方案】NXP S32G2 硬件設計篇(下)

文章出處:【微信號:艾睿電子,微信公眾號:艾睿電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

使用實時處理器擴展恩智浦S32汽車平臺的意義

安富利基于恩智浦S32G汽車網絡處理器開發的eVTOL飛控系統解決方案

NXP推出全新S32G車輛網絡處理器,可簡化軟件復雜性提高安全性

恩智浦加速量產S32R41高性能雷達處理器

新型S32G汽車網絡處理器的主要角色將是面向服務的網關

恩智浦半導體推出了全新的S32G車輛網絡處理器

新思科技針對 S32G 車輛網絡處理器推出 VDK軟件產品

恩智浦擴展S32G網絡處理器系列以提升軟件定義汽車應用的性能

S32G2是NXP一款車規級高性能車輛網絡處理器系列

恩智浦宣布推出全新的S32N系列車輛超級集成處理器

恩智浦車輛網絡處理器S32G硬件設計(下)

恩智浦車輛網絡處理器S32G硬件設計(下)

評論