文章來源:學習那些事

原文作者:趙先生

3D閃存有著更大容量、更低成本和更高性能的優勢,本文介紹了3D閃存的制造工藝與挑戰。

使用 3D 閃存的意義

現存的包含 BE - SONOS 的 2D 閃存架構,在 1x 納米節點處遭遇了密度集成難題,這與邏輯電路持續微縮時面臨的困境類似,即現有的結構已無法契合繼續縮小尺寸后的性能需求。鑒于此,業界研發出 3D NAND 閃存架構,旨在解決在追求更低每比特成本以及實現更高密度過程中所面臨的問題。2012 年,韓國三星公司推出全球首款 3D NAND 閃存芯片,該芯片首次采用 32 層單層單元結構(single - level cell,SLC),存儲單元以垂直方式堆疊成多層。相較于現有的 2D 閃存,這是一種更為先進的閃存架構。

從 2D 閃存向 3D 閃存過渡時,工藝環節需增添多層存儲單元以及各層之間的互連結構。一款典型的 3D NAND 閃存芯片,層數可達 32 層、48 層、64 層、96 層,甚至 128 層。與 2D 閃存相比,層數的增加使得 3D 閃存的制造過程更為復雜且耗時。不過,多層架構讓存儲器件在擁有更短連接路徑的情況下,得以實現更高的位密度,進而展現出更優的性能。3D 閃存具備以下優勢:

容量優勢:與 2D NAND 閃存相比,3D NAND 閃存擁有更大的存儲容量與數據密度。通過堆疊多層存儲單元構建三維存儲矩陣,在相同的芯片面積 —— 即占用空間內,能夠提供更大的存儲容量。同理,更為密集的芯片可被集成到更緊湊、容量更高的設備之中。

成本優勢:閃存與其他存儲技術一樣遵循每字節成本的關聯規律。相較于 2D NAND 閃存,3D NAND 閃存能夠顯著降低每字節成本。

性能與功率優勢:當存儲單元以 2D 矩陣布局時,數據移入和移出單元的距離存在限制。而這一距離等同于時間 —— 也就是延遲。為增大 2D 矩陣的存儲容量,這些距離以及延遲也必然隨之增加,這實際上降低了更大容量 2D NAND 閃存設備的性能。3D 閃存通過堆疊并互連閃存存儲單元層,能夠縮短物理距離,進而減少延遲,使得在更高存儲容量下仍能維持較高性能。此外,3D NAND 閃存可實現單次寫入,功耗相較于 2D NAND 降低 50%。

閃存的制造工藝

在當下的 3D NAND 閃存工藝技術領域,柵極形成工藝主要朝著兩個不同方向發展,分別為電荷陷阱工藝技術以及浮柵技術工藝。一方面,像三星、SK 海力士以及東芝等公司,正在運用電荷陷阱閃存技術。該技術運用氮化硅構成的非導電層,此層環繞在單元的控制柵極周圍,能夠捕獲電荷,以此維持單元的完整性。與之形成對比的是,Intel 和美光公司并未選用電荷陷阱技術。相反,他們將原本應用于 2D 閃存的浮柵結構拓展至 3D NAND 閃存當中。在浮柵結構里,柵極本質上是一種導體,而看似浮柵的電荷陷阱層實則為絕緣體。浮柵技術在實施過程中,涉及一些較為復雜的圖案化步驟,尤其是在制作垂直孔的側面時,圖案化操作難度較大,必須歷經諸多額外的流程步驟。相對而言,電荷陷阱技術的優勢在于無需進行圖案化處理,然而其缺點在于電荷傳輸效率方面存在問題,而這一問題實際上也反映為成本問題。圖 1 展示了不同公司所采用的 3D NAND 工藝技術情況。

圖1:現代3DNAND閃存結構

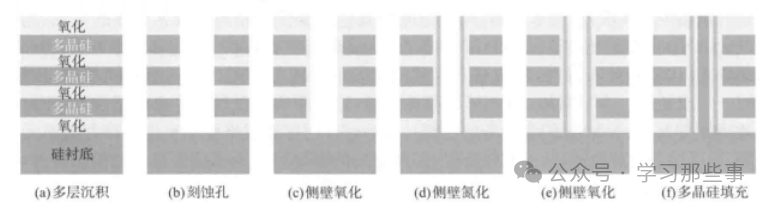

以位列堆疊(bit column stacked,BiCS)架構為例,3D NAND 閃存的具體工藝步驟如下:首先,在硅晶圓襯底之上制造一層 CMOS 邏輯芯片,將其作為外圍邏輯。同時,在襯底上構建導電路徑,用于連接成對的相鄰列,隨后使用一層二氧化硅進行絕緣處理。接著,在其頂部沉積導電多晶硅層,以此形成第一字線和控制柵極,并且讓二氧化硅層在多晶硅頂部生長,目的是使其與后續將沉積在上方的多晶硅層相互絕緣。這一系列操作將重復多次,成對的多晶硅層和二氧化硅層會在整個晶片上層層堆疊,最終形成薄片結構。這種結構類似于蛋糕坯和糖霜交替層疊而成的夾心蛋糕,如圖 2(a)所示。

一旦在晶片上沉積了所需數量的上述層之后,便要在晶片上對圓孔陣列進行圖案化處理,隨后將這些孔刻蝕貫穿所有層,直至抵達基板。圖 2(b)展示了其中一個孔的情況。這種刻蝕技術與 DRAM 溝槽單元技術類似,僅需一個掩模步驟,便能為器件中的所有層形成孔。即便串中可能包含 16、32、64 或更多數量的晶體管,也僅需這一個掩模步驟。相較于現今的 2D NAND 制造工藝,這無疑是一種極為經濟高效的光刻技術。

接下來便是制作浮柵極和溝道孔的內壁。首先,涂抹一層二氧化硅層 [見圖 2(c)],以此創建柵極電介質(即控制柵極和浮柵之間的電介質)。可以將其想象為一個襯在洞里的管子。其次,通過在二氧化硅層上沉積氮化硅層來制作浮柵,這就如同在管內又形成了一個管 [見圖 2(d)]。隨后,在氮化硅層上再沉積另一個氧化物層,用于形成隧道電介質 [見圖 2(e)],這便是排列在孔壁上的三個同心管中的第三個。最后,通過向其中沉積多晶硅 [見圖 2(f)],來填充整個孔(或者在這些同心管在側壁上完成分層之后所剩余的空間)。BiCS 技術屬于一種電荷陷阱技術,因其使用的是絕緣層,所以即便每個單元的電荷陷阱之間并無差異,兩個相鄰的電荷陷阱也不會相互干擾。而且這一層完全無需進行圖案化操作。

圖2:BICS構架3DNAND閃存的基本工藝步驟

閃存的工藝挑戰

盡管 3D NAND 閃存的存儲單元結構相對直觀易懂,然而,不管采用何種架構,無論是電荷陷阱工藝技術,還是浮柵工藝技術,3D NAND 閃存的制造工藝都極為艱難復雜。從原始晶圓加工成完整的晶粒裸片或芯片,需歷經數千個獨立工藝步驟。制造過程中,任何一處出現錯誤或遭受污染,都可能產生缺陷,致使整個芯片報廢。因此,要實現高質量制造,必須采取極為嚴格的污染預防措施,對制造過程進行精準控制,并確保材料純度極高。接下來,主要探討現代 3D 閃存工藝面臨的難點與挑戰。

1) 交替層的堆疊沉積

在 2D NAND 的制造中,先進的光刻技術起著關鍵作用。但在 3D NAND 制造里,供應商采用的是 40nm 至 20nm 的后緣設計規則。雖說先進光刻技術仍在使用,可已不再是最關鍵的環節。對于 3D NAND 而言,工藝挑戰已從光刻工藝轉移至沉積工藝與刻蝕工藝。實際上,3D NAND 為業界帶來了諸多全新且難度頗高的工藝步驟。通過將位串拓展至第三維度,該技術雖緩解了諸多圖案微縮難題,卻引入了一些極為復雜的新流程。這些流程的一致性至關重要,挑戰主要聚焦于對幾個關鍵流程的可變性控制。

3D NAND 的工藝流程始于襯底。隨后,供應商便面臨首個主要挑戰 —— 交替堆疊沉積。利用化學氣相沉積(CVD)技術,交替堆疊沉積指的是在基板上逐層沉積并堆疊薄膜的過程。這一過程恰似制作夾心蛋糕,簡單來講,就是先在基板上沉積一層材料,接著在其上再沉積另一層材料,如此重復多次,直至特定器件達到所需的層數。不同制造商采用不同的材料組合來構建層堆棧。比如,三星公司在硅襯底上交替沉積氮化硅和二氧化硅層;東芝的 3D NAND 技術則由導電多晶硅和絕緣二氧化硅的交替層構成。交替堆疊沉積必須具備良好的均勻性與低缺陷率。所有沉積層的均勻性都要好,這樣才能實現良好的應力控制。由于交替的薄膜各不相同,對于每一層薄膜,都可能因材料不匹配而產生應力問題。而且,隨著 3D NAND 閃存層數的增加,工藝難度與挑戰也在持續攀升。

2) 高深寬比刻蝕

完成交替堆疊沉積步驟后,需在表面施加硬掩模,并進行圖案化處理,以形成所需的孔。此時便進入工藝流程中最為棘手的部分 —— 高深寬比刻蝕,即從器件頂部向襯底刻蝕微小的溝槽或通道。為了說明這一步驟的復雜程度,以某類 3D NAND 芯片為例,同一芯片中存在 250 萬個微小通孔,且每個通孔都必須保持平行且均勻。目前的高深寬比刻蝕工具能夠滿足 32 層和 48 層器件的需求,對于這些芯片,深寬比范圍在 30:1 至 40:1 之間。這種刻蝕過程極為復雜,要在大量刻蝕過程中保持高度的統計學一致性,對存儲設備的性能有著極為嚴苛的要求。而對于 64 層及以上的芯片,以目前的刻蝕能力而言,難度過高,現有的刻蝕和硬掩模技術未必適用于 60:1 或 70:1 這樣的高深寬比。

因此,NAND 供應商目前同時推進兩條技術發展路徑。第一條路徑是等待下一代高深寬比刻蝕工具以及其他相關技術的問世。一旦刻蝕機按時研發完成,現有的 3D NAND 技術將按照如下順序實現擴展:從現有的 32 層和 48 層,逐步發展到 64 層,進而邁向 96 層,最終達到 128 層。而在第二條路徑中,NAND 制造商致力于開發下一代串堆疊技術。所謂串堆疊技術,簡言之,就是把多個 3D NAND 閃存器件進行堆疊,并且每個器件之間可能會用絕緣層加以隔離。例如,制造商計劃開發 48 層的 3D NAND 閃存器件,這一過程需要歷經前文所提及的各類工藝流程,諸如交替層沉積、刻蝕等操作。供應商會采用同樣的流程制造出另外的 48 層 NAND 芯片,之后將它們堆疊在一起。需要注意的是,該工藝并不局限于 48 層芯片。倘若相關技術成熟,制造商甚至可以對 64 層、96 層乃至 128 層的芯片進行堆疊。從理論層面考量,通常會優先選用 32 層和 48 層芯片來實施串堆疊,原因在于相較于 96 層或 128 層芯片,單個 32 層或 48 層器件所承受的應力相對較小。

然而,最終帶有串堆疊的 3D NAND 技術或許會在堆疊層數達到 300 層左右時遭遇瓶頸。隨著堆疊層數的增加,因堆疊過程中產生的缺陷而導致的良品率損失會持續攀升,這無疑將成為限制技術發展的一大因素。此外,所有堆疊的薄膜材料都會受到應力方面的制約。可以確定的是,字符串堆疊技術目前仍存在諸多未知因素以及挑戰。即便不考慮字符串堆疊技術,整個行業在 3D NAND 技術領域依舊面臨著一些難題。無論處于何種情形,業界都必須持續深入研究并完善 3D NAND 的各個工藝步驟。否則,該項技術的成本仍將居高不下。

3) 金屬沉積

在完成柵極的制作后,接下來的通孔形成工藝同樣充滿挑戰。此環節需要借助金屬沉積步驟,利用金屬導體對 3D NAND 閃存器件進行回填操作。

通常情況下,會選用鎢作為回填通孔孔洞的材料。這一沉積步驟極具難度,因為它屬于非視線沉積方式。倘若沒有合理設計工藝流程,在沉積過程中極有可能錯誤地鍍出金屬鎢的前體金屬。這些前體金屬在進入接觸柱孔洞時,可能會立刻脫落,進而導致接觸柱出現空隙。

-

NAND

+關注

關注

16文章

1722瀏覽量

138107 -

制造工藝

+關注

關注

2文章

205瀏覽量

20360 -

閃存芯片

+關注

關注

1文章

131瀏覽量

19909 -

3D閃存

+關注

關注

0文章

22瀏覽量

6688

原文標題:3D閃存工藝

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

制造業革命——3D打印的主流工藝盤點

美光推出首款3D XPoint閃存 展現出了3D XPoint閃存的強大實力

3D打印技術是怎么推動制造業的

一種用于制造電動機永磁體的冷噴涂3D打印工藝

3D工藝的轉型步伐較慢,NAND閃存依然處于供給吃緊的狀態

3D打印助力汽車零部件制造工藝提升

三星正在研發160層及以上的3D閃存

三星正在開發160堆棧3D閃存 將大幅改進制造工藝

美光發布176層3D NAND閃存

不要過于關注3D NAND閃存層數

英國大學開發了一種全新3D打印工藝

3D閃存的制造工藝與挑戰

3D閃存的制造工藝與挑戰

評論