概述

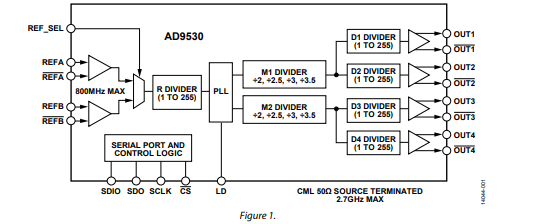

AD9530是一款針對40 Gbps/ 100 Gbps OTN應(yīng)用的完全集成式PLL和分配器件,支持時鐘清零和頻率轉(zhuǎn)換。 內(nèi)部PLL可鎖定至兩個參考頻率之一以生成最高達(dá)2.7 GHz的四個離散輸出頻率。

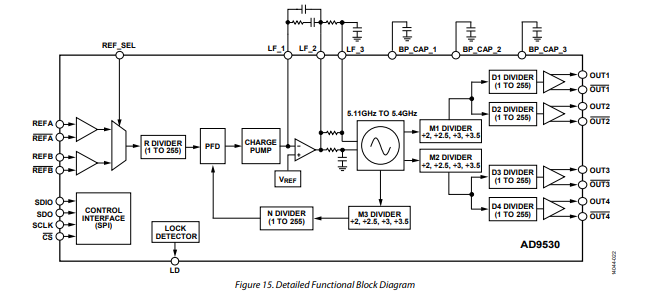

AD9530集成了內(nèi)部5.11 GHz至5.4 GHz、超低噪聲壓控振蕩器(VCO)。 所有四個輸出均從內(nèi)部VCO進(jìn)行單獨(dú)分頻,并使用兩個高速VCO分頻器(Mx分頻器)和四個獨(dú)立的8位通道分頻器(Dx分頻器)。 高速VCO分頻器提供2、2.5、3、和3.5固定分頻,提供寬覆蓋范圍的可能輸出頻率。 AD9530配置用于小于15 kHz的環(huán)路帶寬以便衰減基準(zhǔn)電壓源噪聲。

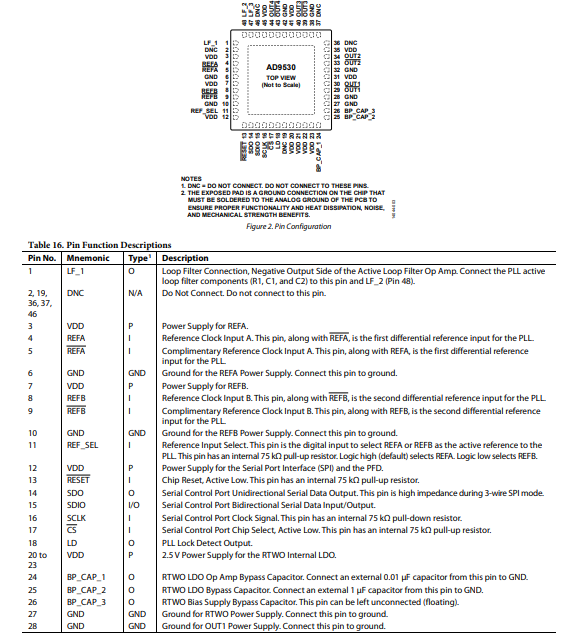

AD9530提供48引腳LFCSP封裝,采用典型2.5 V單電源供電。

AD9530的工作溫度范圍為?40°C至+85°C的擴(kuò)展工業(yè)溫度范圍。

數(shù)據(jù)表:*附件:AD9530集成5.4 GHz VCO的4路CML輸出、低抖動時鐘發(fā)生器技術(shù)手冊.pdf

應(yīng)用

- 40 Gbps/100 Gbps光傳輸網(wǎng)絡(luò)(OTN)線路端時鐘

- 高速模數(shù)轉(zhuǎn)換器(ADC)和數(shù)模轉(zhuǎn)換器(DAC)時鐘

- 數(shù)據(jù)通信

特性 - 完全集成式超低噪聲鎖相環(huán)(PLL)

- 4個差分、2.7 GHz共模邏輯(CML)輸出

- 帶可編程內(nèi)部端接選項(xiàng)的2個差分基準(zhǔn)電壓輸入

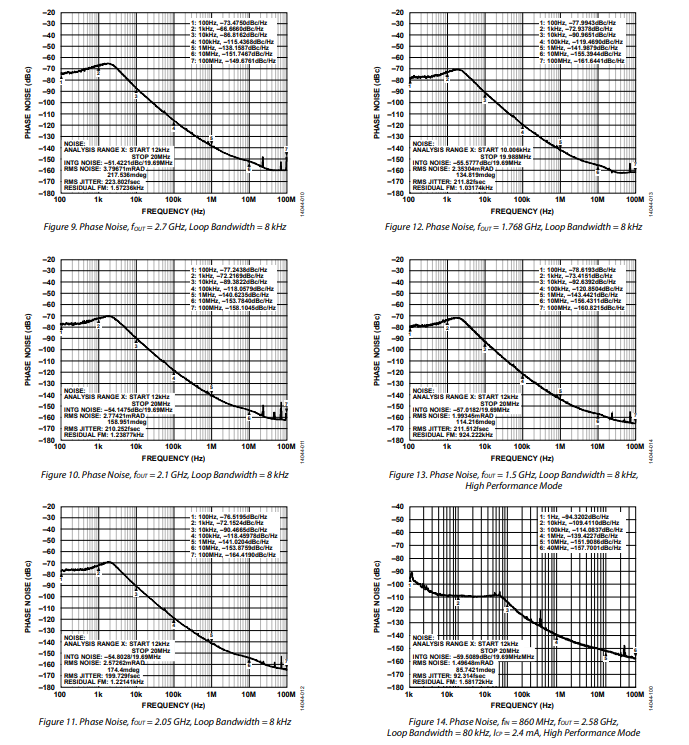

- 絕對抖動小于232 fs rms(12 kHz至20 MHz),具有非理想基準(zhǔn)電壓和8 kHz環(huán)路帶寬

- 絕對抖動小于100 fs rms(12 kHz至20 MHz),具有80 kHz環(huán)路帶寬和低抖動輸入?yún)⒖紩r鐘

- 支持適合抖動衰減應(yīng)用的低環(huán)路帶寬

- 手動切換

- 采用典型2.5 V單電源供電

- 48引腳、7 mm × 7 mm LFCSP封裝

框圖

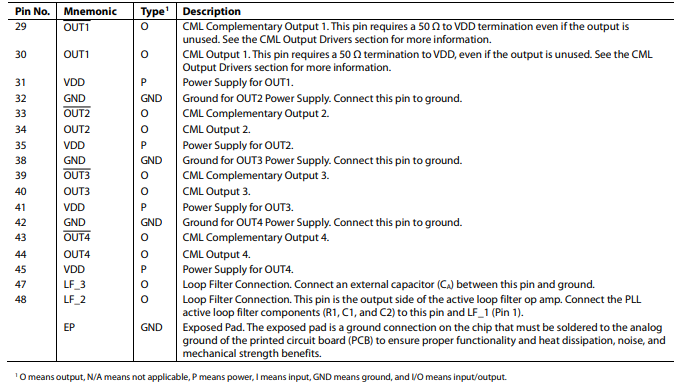

引腳配置描述

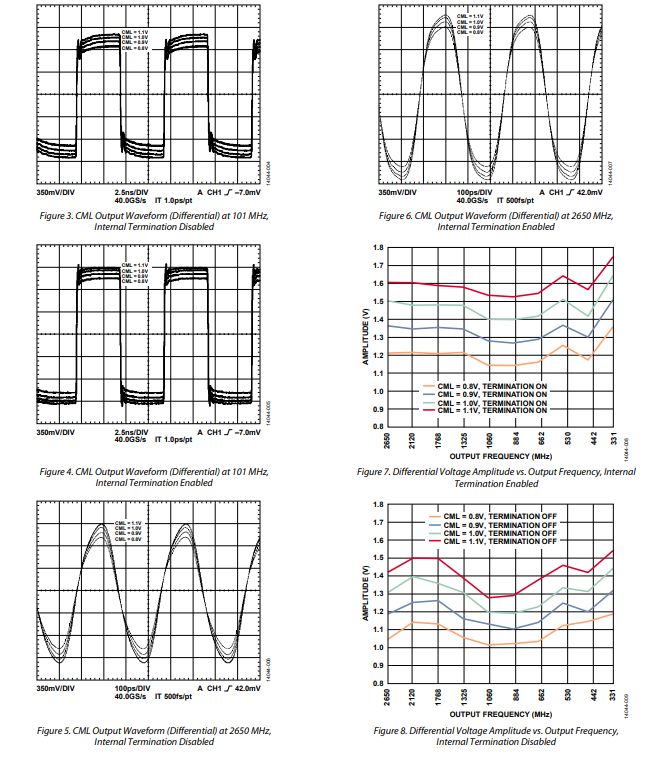

典型性能特征

操作原理詳細(xì)功能框圖

AD9530 是一款全集成的整數(shù) N 型鎖相環(huán)(PLL),具有超低噪聲的內(nèi)部 5.11 GHz 至 5.4 GHz 壓控振蕩器(VCO),能夠產(chǎn)生小于 232 fs(均方根,12 kHz 至 20 MHz)抖動的兩路正交信號,參考信號為非相干信號。AD9530 適用于 40 Gbps 和 100 Gbps 光傳輸網(wǎng)絡(luò)(OTN)應(yīng)用,這些應(yīng)用對轉(zhuǎn)換器和專用集成電路(ASIC)時鐘的規(guī)格要求嚴(yán)格。

AD9530 集成了片上鎖相環(huán)、內(nèi)部壓控振蕩器,以及四個具有集成驅(qū)動器的輸出通道和共模邏輯(CML)驅(qū)動器。鎖相環(huán)包含一個部分內(nèi)部有源環(huán)路濾波器,這需要少量外部組件來實(shí)現(xiàn)環(huán)路帶寬低于 15 kHz,以抑制參考相位噪聲。

AD9530 的四個輸出具有獨(dú)立的分頻器,可生成高達(dá) 2.7 GHz 的四個不同頻率。

鎖相環(huán)配置

鎖相環(huán)的配置是通過對各種設(shè)置進(jìn)行編程來實(shí)現(xiàn)的,包括 R 分頻器、N 分頻器、M3 分頻器、電荷泵電流,以及壓控振蕩器的組合。這些設(shè)置與環(huán)路濾波器共同決定了鎖相環(huán)的帶寬和穩(wěn)定性。

鎖相環(huán)的成功運(yùn)行和令人滿意的性能在很大程度上取決于適當(dāng)?shù)膬?nèi)部鎖相環(huán)設(shè)置和環(huán)路濾波器。ADIsimCLK 是一款免費(fèi)軟件,有助于設(shè)計和探索 AD9530 的功能特性,包括鎖相環(huán)和濾波器的設(shè)計。

鑒頻鑒相器(PFD)

鑒頻鑒相器接收來自 R 分頻器輸出和反饋分頻器路徑的輸入,產(chǎn)生一個與兩者之間的相位和頻率差成正比的輸出。它包含一個可調(diào)節(jié)延遲元件,用于控制反沖脈沖的寬度。該脈沖可確保鑒頻鑒相器中不存在死區(qū),從而實(shí)現(xiàn)相位和頻率噪聲的最小化。

鑒頻鑒相器的最大允許輸入頻率在表 5 中有具體規(guī)定。

電荷泵(CP)

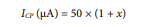

電荷泵由鑒頻鑒相器控制。鑒頻鑒相器監(jiān)測兩個輸入之間的相位和頻率關(guān)系,并使電荷泵相應(yīng)地充電或放電,對作為環(huán)路濾波器一部分的積分節(jié)點(diǎn)進(jìn)行操作。經(jīng)過積分和濾波的 CP 電流被轉(zhuǎn)換為一個電壓,該電壓驅(qū)動調(diào)諧節(jié)點(diǎn),使壓控振蕩器朝著目標(biāo)頻率上升或下降。電荷泵電流可進(jìn)行 52 步編程,每步對應(yīng)電流增加 50 μA。

通過以下公式計算電荷泵電流 (I_{CP}:

其中 x 是寫入寄存器 0x025 第 5:0 位的值。

-

pll

+關(guān)注

關(guān)注

6文章

888瀏覽量

136172 -

分配器

+關(guān)注

關(guān)注

0文章

203瀏覽量

26190 -

時鐘發(fā)生器

+關(guān)注

關(guān)注

1文章

223瀏覽量

68988

發(fā)布評論請先 登錄

用于評估AD9530 2.7 GHz時鐘發(fā)生器的評估板AD9530/PCBZ

MAX3625A 低抖動、精密時鐘發(fā)生器,提供三路輸出(應(yīng)用

MAX3624 低抖動、精密時鐘發(fā)生器,提供四路輸出

AD9530 集成5.4 GHz VCO的4路CML輸出、低抖動時鐘發(fā)生器

AD9520-0:12路LVPECL/24路CMOS輸出時鐘發(fā)生器,集成2.8 GHz VCO

AD9523-1:低抖動時鐘發(fā)生器,14路LVPECL/LVDS/HSTL輸出或29路LVCMOS輸出 數(shù)據(jù)手冊

AD9520-2:12集成2.2 GHz壓控振蕩器數(shù)據(jù)表的LVPECL/24 CMOS輸出時鐘發(fā)生器

AD9530:4 CML輸出、低抖動時鐘發(fā)生器,集成5.4 GHz壓控振蕩器數(shù)據(jù)表

AD9522-3:12集成2 GHz壓控振蕩器數(shù)據(jù)表的LVDS/24 CMOS輸出時鐘發(fā)生器

AD9522-4:12集成1.6 GHz壓控振蕩器數(shù)據(jù)表的LVDS/24 CMOS輸出時鐘發(fā)生器

集成2.2 GHz VCO數(shù)據(jù)表的AD9522-2:12 LVDS/24 CMOS輸出時鐘發(fā)生器

AD9520-4:12集成1.6 GHz壓控振蕩器數(shù)據(jù)表的LVPECL/24 CMOS輸出時鐘發(fā)生器

CDCM61004四路輸出、集成VCO、低抖動時鐘發(fā)生器數(shù)據(jù)表

CDCM61002兩路輸出、集成VCO、低抖動時鐘發(fā)生器數(shù)據(jù)表

AD9530集成5.4 GHz VCO的4路CML輸出、低抖動時鐘發(fā)生器技術(shù)手冊

AD9530集成5.4 GHz VCO的4路CML輸出、低抖動時鐘發(fā)生器技術(shù)手冊

評論