概述

AD9574具有多路輸出時鐘發生器功能,內置專用鎖相環(PLL)內核,針對以太網和千兆以太網線路卡應用進行了優化。 整數N PLL設計基于ADI公司成熟的高性能、低抖動頻率合成器產品系列,確保實現高的網絡性能。 AD9574還適合要求低相位噪聲和抖動性能的其他應用。

數據表:*附件:AD9574以太網 千兆以太網時鐘發生器技術手冊.pdf

配置AD9574以用于特定應用時,只需將外部上拉或下拉電阻連接到適當的引腳編程讀取器引腳(PPRx)即可。 通過這些引腳可以控制內部分頻器,以建立所需的頻率轉換、時鐘輸出功能和輸入參考功能。 將外部19.44 MHz或25 MHz振蕩器連接到參考輸入REF0_P/REF0_N和REF1_P/REF1_N或其中之一時,便可得到PPRx引腳規定的一組輸出頻率。 將穩定的時鐘源(8 kHz/10 MHz/19.44 MHz/25 MHz/38.88 MHz)連接到監控器時鐘輸入時,可選監控器電路便可提供REF0或REF1的服務質量(QoS)狀態。

PLL部分由低噪聲鑒頻鑒相器(PFD)、精密電荷泵(CP)、部分集成環路濾波器(LF)、低相位噪聲電壓控制振蕩器(VCO)、反饋分頻器和輸出分頻器組成。 分頻器值取決于PPRx引腳。 集成環路濾波器只要求將單個外部電容連接到LF引腳。

AD9574采用48引腳7 mm × 7 mm LFCSP封裝,只需3.3 V單電源, 工作溫度范圍為?40°C至+85°C。

應用

特性

- 冗余輸入參考時鐘功能

- 參考監控功能

- 全集成式VCO/PLL內核

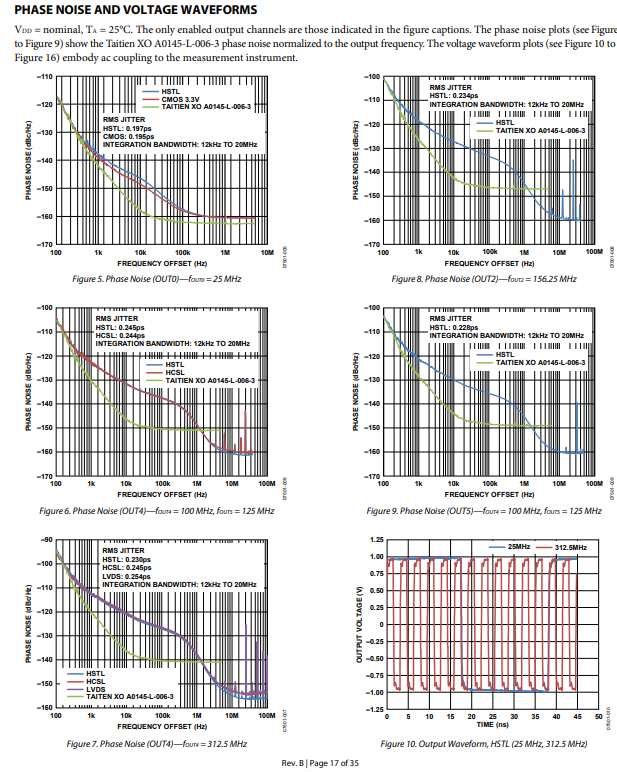

- 抖動(rms)

0.234 ps rms抖動(10 kHz至10 MHz,156.25 MHz時)

0.243 ps rms抖動(12 kHz至20 MHz,156.25 MHz時) - 輸入頻率: 19.44 MHz或25 MHz

- 預設頻率轉換

- 采用19.44 MHz輸入參考

19.44 MHz、38.88 MHz、77.76 MHz、155.52 MHz - 采用25 MHz輸入參考

25 MHz、33.33 MHz、50 MHz、66.67 MHz、80 MHz、100 MHz、125 MHz、133.3 MHz、156.25 MHz、160 MHz、312.5 MHz

- 采用19.44 MHz輸入參考

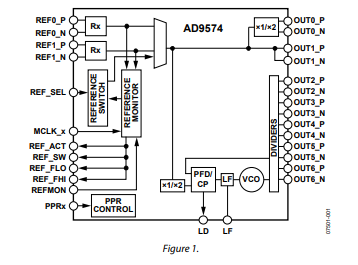

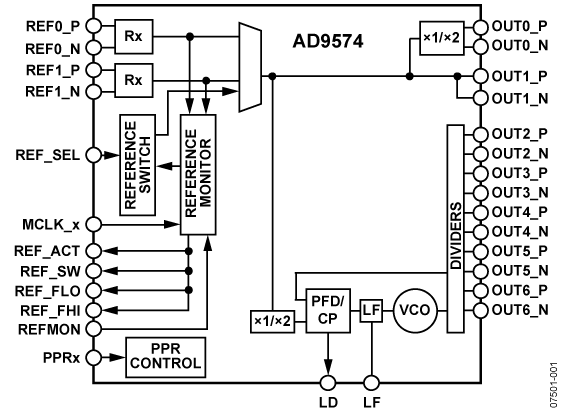

框圖

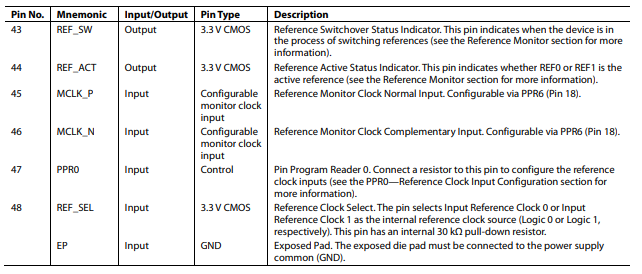

引腳配置描述

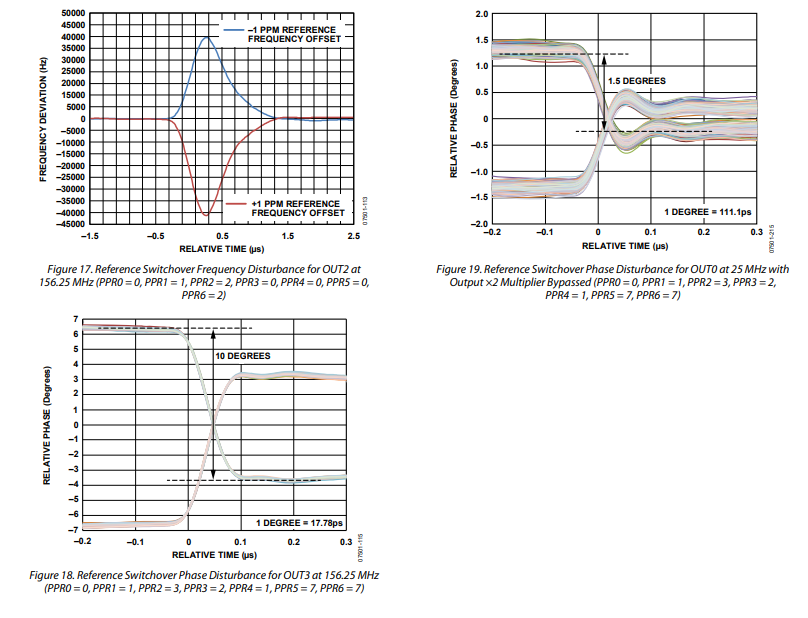

典型性能特征

操作理論

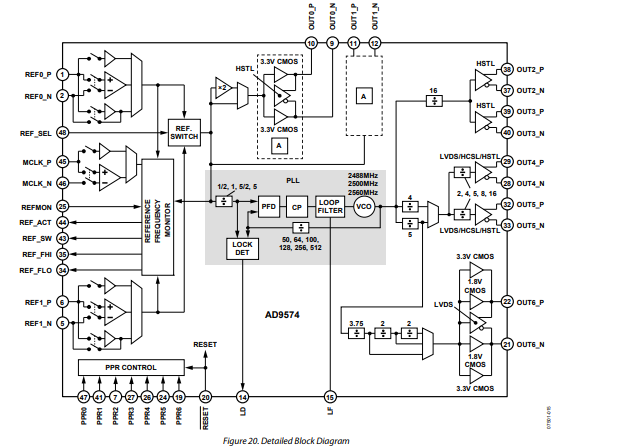

圖20展示了AD9574的框圖。AD9574可接收19.44 MHz或25 MHz的參考時鐘(REF0_x和/或REF1_x輸入)。它還支持0.08 MHz、10 MHz、19.44 MHz、25 MHz或38.88 MHz的監控器時鐘輸入(MCLK_x輸入)。監控器時鐘作為器件內部參考頻率的穩定頻率參考。輸入接收器可提供差分或單端輸入配置。

AD9574可提供多達六個輸出通道時鐘(OUT0至OUT6)。OUT0和OUT1通道提供REF0或REF1通道頻率的復制,或通過OUT2至OUT6通道實現頻率加倍。OUT2至OUT6通道通過集成鎖相環(PLL)和分頻器鏈提供各種輸出頻率。輸出時鐘驅動器可提供多種模式,包括LVDS、HSTL、HCSL、1.8 V CMOS和3.3 V CMOS,不過并非所有模式在每個輸出上都可用。

集成鎖相環可實現必要的頻率轉換。鎖相環輸入端的分頻器模塊由一個×2乘法器、一個二分頻器和一個乘法器組成,配置為實現圖20中可能的分頻值(1/2、1、1/5、2或5)。

PPRx引腳

AD9574利用七個PPRx引腳對器件進行配置。內部電路會掃描PPRx引腳,以確定電阻終端情況,并相應地配置器件。PPRx引腳掃描會在加電或復位序列(即POWER_ON_RESET (POR)部分)期間自動進行,或在RESET引腳置位后進行。

每個PPRx引腳可控制特定功能或功能模塊內的器件(見圖19)。功能模塊的配置取決于相應PPRx引腳的掃描狀態。掃描基于外部上拉或下拉電阻(最大10%容差)設置的七個可能狀態之一。

-

以太網

+關注

關注

40文章

5585瀏覽量

174819 -

pll

+關注

關注

6文章

883瀏覽量

136047 -

時鐘發生器

+關注

關注

1文章

223瀏覽量

68876 -

ad9574

+關注

關注

0文章

4瀏覽量

4016

發布評論請先 登錄

基于Xilinx FPGA的千兆以太網控制器的開發

簡談基于FPGA的千兆以太網設計

ATM與千兆以太網的區別

以太網千兆以太網時鐘發生器ad9574數據表

AD9574 以太網/千兆以太網時鐘發生器

以太網技術聯盟發布了800千兆位以太網的規范

AD9574:以太網/Gigabit Ethernet Clock數據Sheet

AD9574以太網 千兆以太網時鐘發生器技術手冊

AD9574以太網 千兆以太網時鐘發生器技術手冊

評論