概述

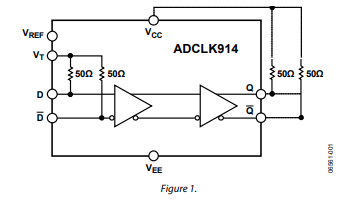

ADCLK914是一款采用ADI公司專利的互補雙極性(XFCB-3)硅鍺(SiGe)工藝技術(shù)制造的超快型時鐘/數(shù)據(jù)緩沖器。ADCLK914具備高壓差分信號(HVDS)輸出,適合用于驅(qū)動ADI最新的高速數(shù)模轉(zhuǎn)換器(DAC)。ADCLK914具備單個差分開集輸出。

數(shù)據(jù)表:*附件:ADCLK914超快型SiGe開集HVDS時鐘 數(shù)據(jù)緩沖器技術(shù)手冊.pdf

ADCLK914緩沖器的工作頻率高達7.5 GHz,其傳播延遲為160 ps,僅增加110 fs的隨機抖動(RJ)。

輸入具有100 Ω中心抽頭片內(nèi)端接電阻,并接受LVPECL、CML、CMOS、LVTTL或LVDS(僅交流耦合)。VREF引腳可用來為交流耦合輸入提供偏置。

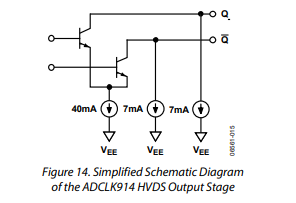

HVDS輸出級可以直接將每端1.9 V驅(qū)動至端接于VCC的50 Ω傳輸線路中,從而獲得3.8 V的總差分輸出擺幅。

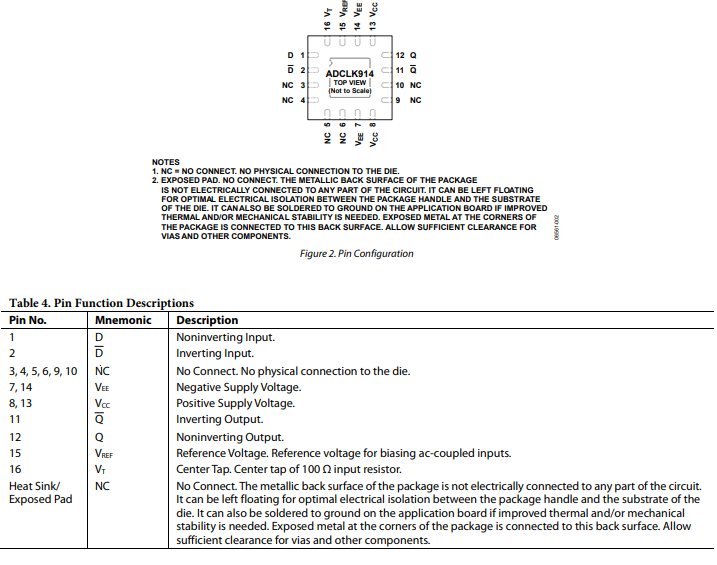

ADCLK914采用16引腳LFCSP封裝。額定工作溫度范圍為擴展的工業(yè)溫度范圍?40°C至+125°C。

應(yīng)用

特性

- 7.5 GHz工作頻率

- 160 ps傳播延遲

- 100 ps輸出上升時間/下降時間

- 110 fs隨機抖動

- 片內(nèi)輸入端接電阻

- 擴展工業(yè)溫度范圍:

?40°C to +125°C - 3.3 V電源(VCC ? V EE )

框圖

引腳配置描述

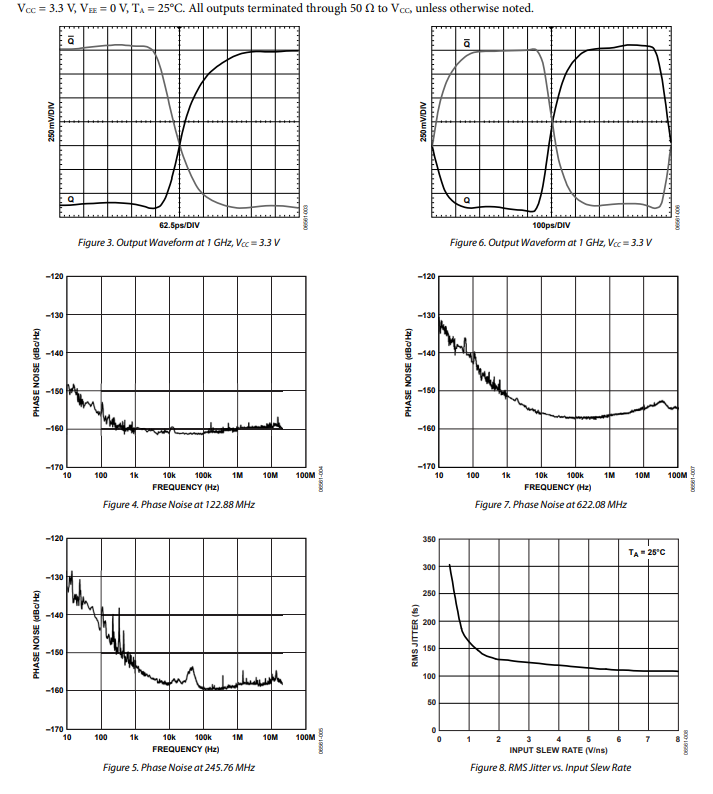

典型性能特征

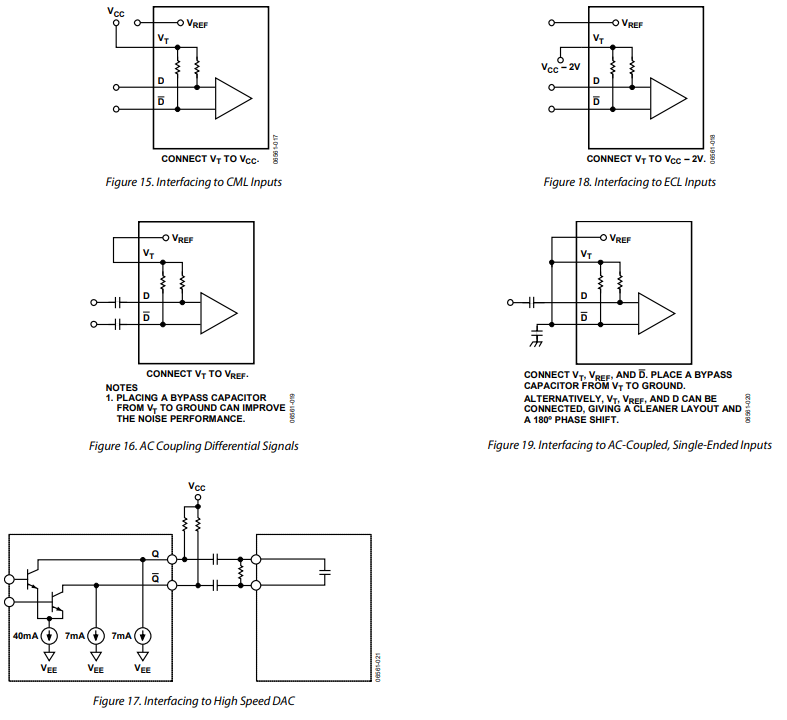

應(yīng)用信息

電源/接地布局和旁路

ADCLK914緩沖器專為高速應(yīng)用而設(shè)計。因此,必須采用高速設(shè)計技術(shù)才能達到規(guī)定的性能。對于多層電路板的負電源(V_{EE})和正電源(V_{CC})層,使用低阻抗電源層至關(guān)重要。提供最低電感的開關(guān)電流返回路徑可確保目標應(yīng)用獲得最佳性能。

充分旁路輸入和輸出電源也很重要。在接地層幾英寸范圍內(nèi)放置一個1 μF電解旁路電容。此外,放置多個高質(zhì)量的0.001 μF旁路電容,盡可能靠近每個**V_{CC}**電源引腳,并通過冗余過孔將電容連接到接地層。仔細選擇高頻旁路電容,以實現(xiàn)最低電感和等效串聯(lián)電阻(ESR)。為提高高頻旁路效率,盡量減少寄生布局電感。

大電流會在**V_{EE}和V_{CC}**引腳處產(chǎn)生顯著的寄生電感。應(yīng)嚴格避免器件被ADCLK914驅(qū)動時出現(xiàn)這種情況。

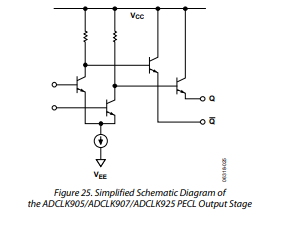

LVDS輸出級

ADCLK914可提供與任何CMOS器件的雙極接口。輸出可直接連接到接收器件的輸入,也可放置在靠近時鐘分配樹的位置,以實現(xiàn)單端CMOS和PECL電平。

互連線必須短且精心設(shè)計,因為單端端接設(shè)計在電壓較低的雙端端接傳輸技術(shù)方面余量較小。

與高速DAC接口

ADCLK914旨在驅(qū)動高幅度、低抖動時鐘信號進入高速、多輸入(MIPI)的DAC。ADCLK914應(yīng)放置在盡可能靠近時鐘輸入的DAC位置,以便高斜率和高幅度時鐘信號能夠到達這些器件,且不會導(dǎo)致占空比失真。

優(yōu)化高速性能

與任何高速電路一樣,正確的設(shè)計和布局技術(shù)對于實現(xiàn)預(yù)期的特定性能至關(guān)重要。串擾、電容、電感、電感耦合以及其他寄生效應(yīng)會導(dǎo)致信號完整性問題,進而嚴重影響輸入和輸出傳輸線的性能,還可能降低輸出斜率。

輸入和輸出匹配對性能有顯著影響。ADCLK914緩沖器提供內(nèi)部50 Ω端接電阻,用于兩個Buff D和D輸出。通常,返回引腳連接到提供的參考引腳,或連接到與不同PECL一起使用時為V_{CC} - 2 V的匯點,或與標準或低擺幅PECL、CML、CMOS或LVTTL源一起使用時為**V_{CC}**的匯點,如圖15所示。

注意,ADCLK914 **V_{CC}電源應(yīng)持續(xù)監(jiān)控,以避免因V_{CC}或V_{EE}**瞬間短路以及電容充電電流而造成損壞,因為這些情況會使電源無法充分供電。

仔細使用陶瓷電容旁路端接電位,以防止寄生電感對輸入信號產(chǎn)生不必要的干擾。由于輸入直接耦合到源,必須注意確保引腳處于指定的差分和共模范圍內(nèi)。

如果返回引腳浮空,器件將呈現(xiàn)100 Ω交叉端接,但此時信號源必須控制共模電壓并提供輸入偏置電流。

輸入引腳之間設(shè)有靜電放電(ESD)/鉗位二極管,以防止輸入晶體管產(chǎn)生過大偏移。ESD二極管并非針對最佳性能進行優(yōu)化。如果需要鉗位,建議使用合適的外部二極管。

隨機抖動

ADCLK914緩沖器經(jīng)過專門設(shè)計,可在較寬的輸入斜率范圍內(nèi)將額外的隨機抖動降至最低。只要有可能,應(yīng)使用快速肖特基二極管衰減器來降低過大輸入信號的斜率,因為衰減器應(yīng)采用低損耗電介質(zhì)或具有良好高頻特性的電纜。

典型應(yīng)用電路

-

SiGe

+關(guān)注

關(guān)注

0文章

99瀏覽量

23953 -

時鐘

+關(guān)注

關(guān)注

11文章

1887瀏覽量

132947 -

adclk914

+關(guān)注

關(guān)注

0文章

3瀏覽量

1875 -

數(shù)據(jù)緩沖器

+關(guān)注

關(guān)注

1文章

11瀏覽量

1903

發(fā)布評論請先 登錄

ADCLK914輸出功率過小

ADCLK914 mu中的dll一直鎖不定是怎么回事?

ADCLK914,pdf datasheet (HVDS C

超快SiGe集電極開路HVDS時鐘/數(shù)據(jù)緩沖區(qū)adclk914數(shù)據(jù)表

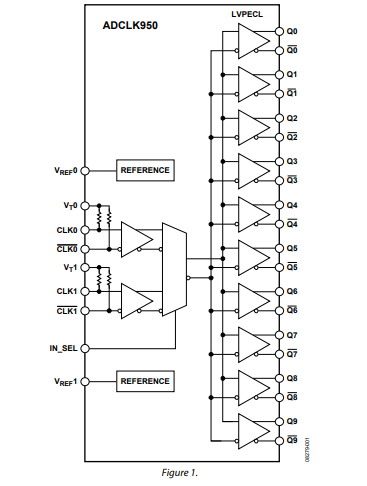

ADCLK950:兩個可選輸入、10個LVPECL輸出、SiGe時鐘扇出緩沖器數(shù)據(jù)表

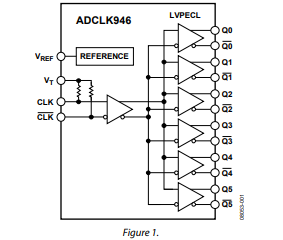

ADCLK946:六路LVPECL輸出,SiGe時鐘扇出緩沖器數(shù)據(jù)表

ADCLK954:兩個可選輸入、12個LVPECL輸出、SiGe時鐘扇出緩沖器數(shù)據(jù)表

ADCLK948:兩個可選輸入、8個LVPECL輸出、SiGe時鐘扇出緩沖器數(shù)據(jù)表

ADCLK914:超高速、SiGe、開放采集器HVDS時鐘/數(shù)據(jù)緩沖器數(shù)據(jù)表

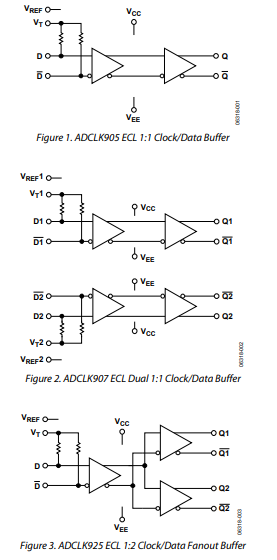

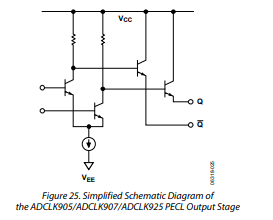

ADCLK905超快型SiGe ECL時鐘/數(shù)據(jù)緩沖器技術(shù)手冊

ADCLK907超快型SiGe ECL時鐘/數(shù)據(jù)緩沖器技術(shù)手冊

ADCLK925超快型SiGe ECL時鐘/數(shù)據(jù)緩沖器技術(shù)手冊

ADCLK914超快型SiGe開集HVDS時鐘/數(shù)據(jù)緩沖器技術(shù)手冊

ADCLK914超快型SiGe開集HVDS時鐘/數(shù)據(jù)緩沖器技術(shù)手冊

評論