來都來了,我們就來好好講講為什么萬能的FPGA如此青睞FMC?

來都來了,我們就來好好講講為什么萬能的FPGA如此青睞FMC?

Why FMC?

FMC即FPGA Mezzanine Card(FPGA中間層板卡),由子板模塊和載卡兩部分構成。

FMC載卡:為子板模塊提供插槽,使用母座FMC連接器。載卡連接器引腳與具有可配置IO資源的芯片例如FPGA引腳通過PCB設計連接在一起。

FMC 子板模塊:子板模塊上使用公座FMC連接器。子卡通過設計不同的IO接口實現不同的功能,使載卡連接不同的子板從而實現不同的擴展功能。

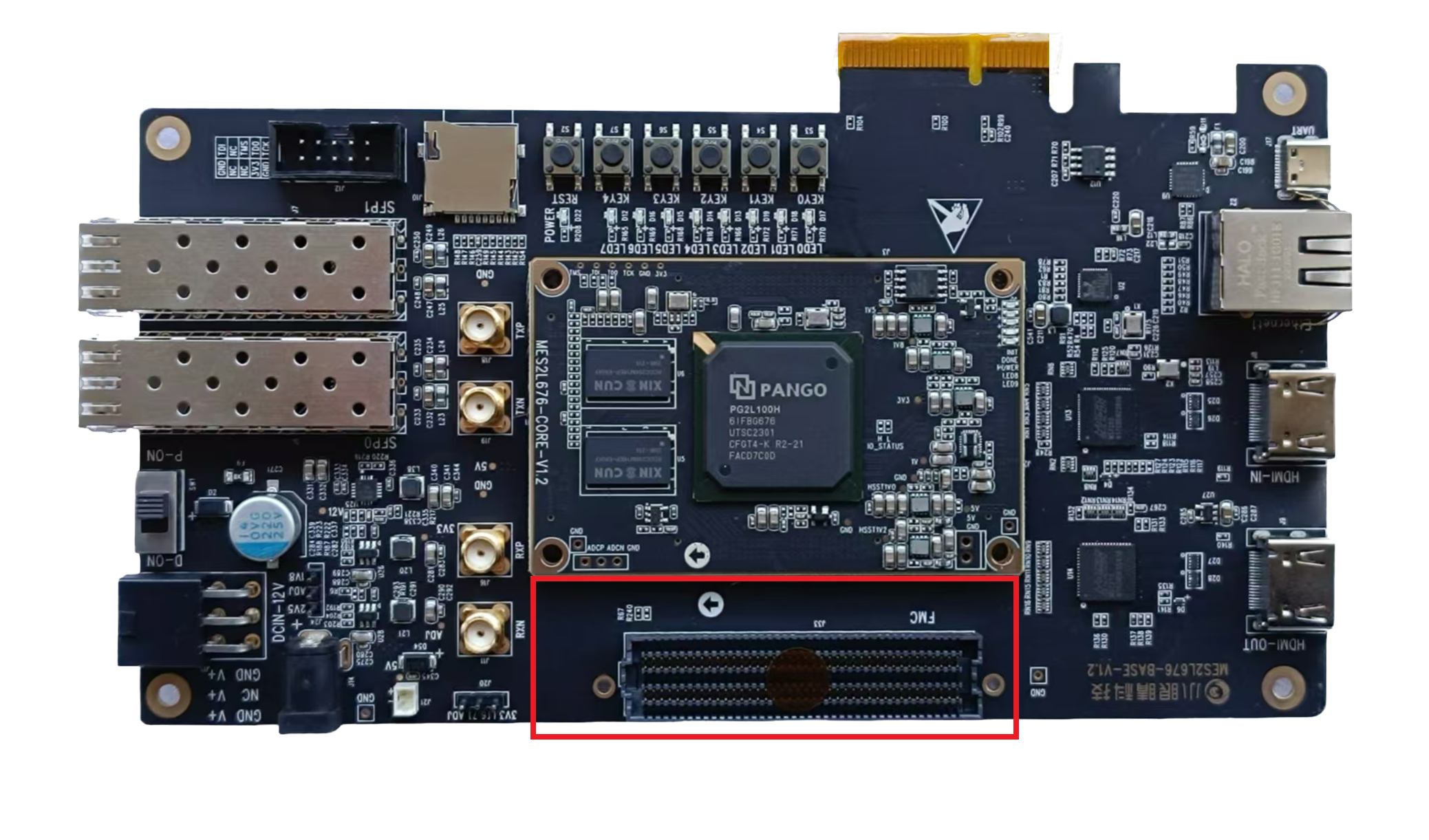

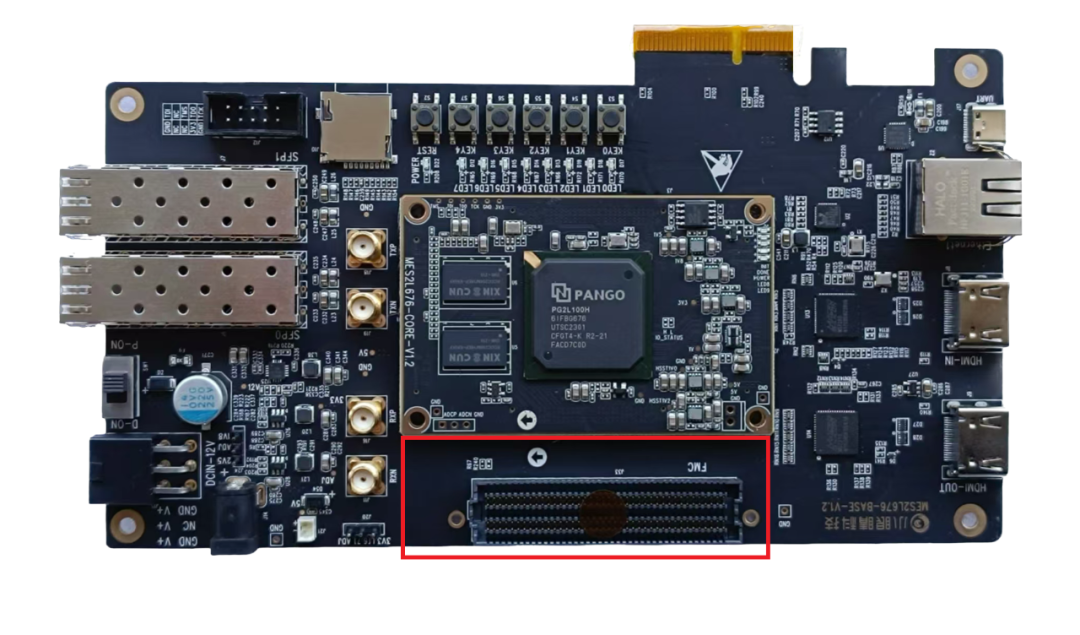

*盤古100pro+開發板FMC接口

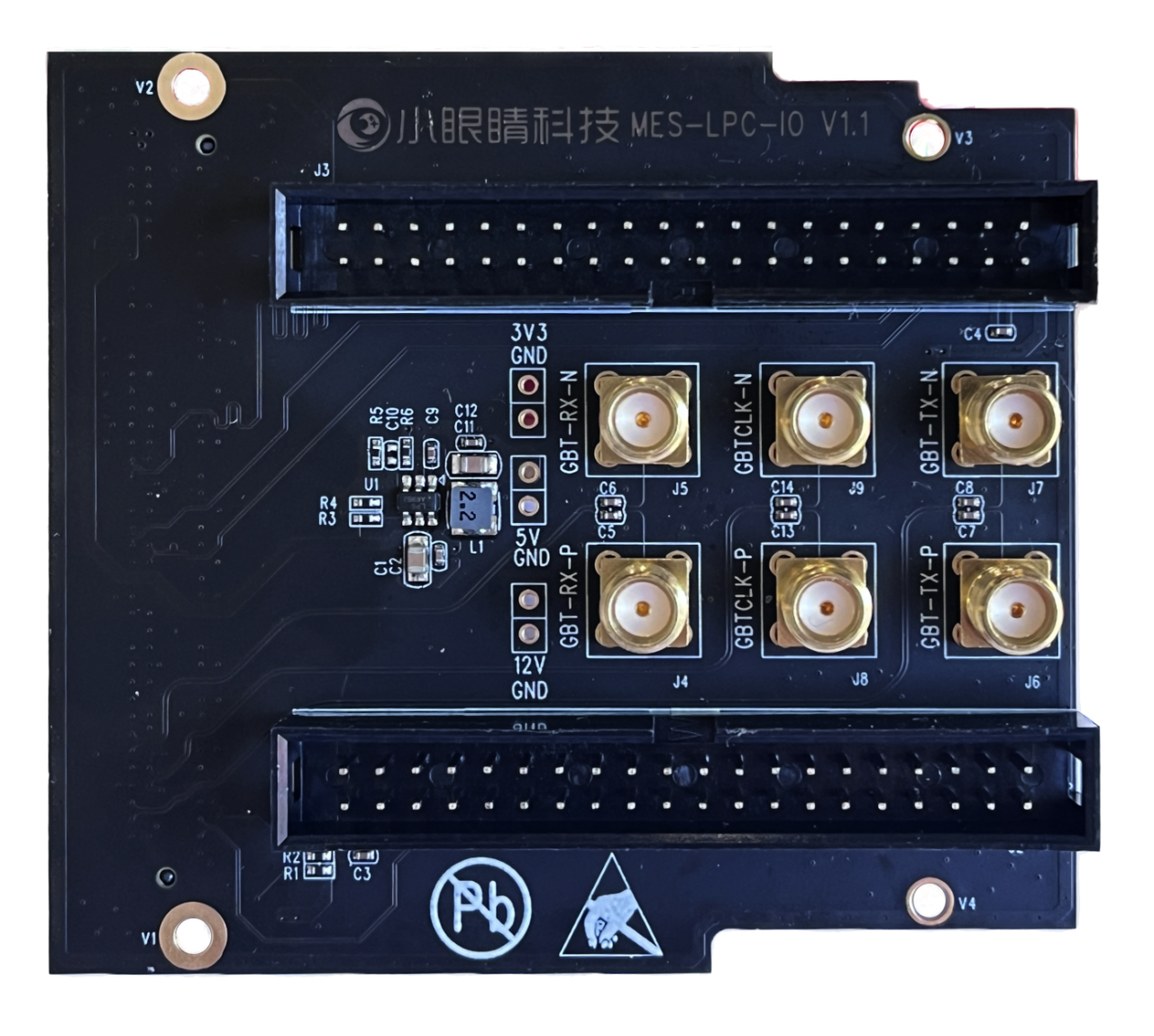

*盤古100pro+開發板FMC子板

美國國家標準

根據美國國家標準對FMC 標準(ANSI/VITA57.1-2008)的規定,FMC 子板有單寬和雙寬兩種尺寸,其具體尺寸信息如下:

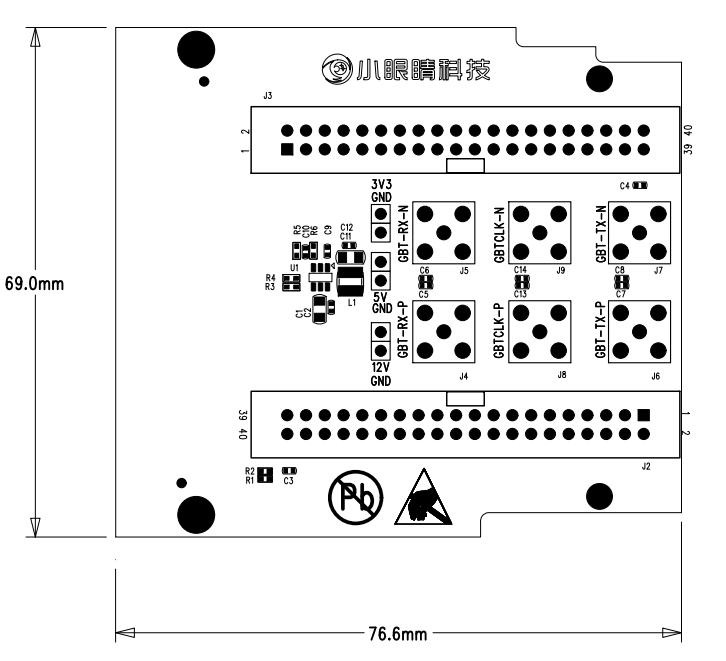

單寬子板:寬度69mm/長度76.5mm,也有其他尺寸如84.1mm/高度8.5mm和10mm兩種,但一般默認10mm

雙寬子板:寬度139mm/長度一般是76.5mm/高度同樣是有8.5mm和10mm兩種,默認高度10mm。

這玩意都能整上美國國標了,嗯,就很高!大!上!

*盤古100pro+開發板FMC子板結構圖

為使不同的FMC 子卡和載卡能相互兼容,FMC 接口管腳定義遵循 ANSI/VITA 57 等標準。每個管腳都有特定的功能,如:

CLK0_C2M_P、CLK0_C2M_N:從載卡到 IO 子板模塊的差分時鐘信號。

CLK0_M2C_P、CLK0_M2C_N:從 IO 子板模塊到載卡的差分時鐘信號。

HA(00..23)_P、HA(00..23)_N:HPC 上 bank A 的用戶自定義信號,為差分信號對。

HB(00..21)_P、HB(00..21)_N:HPC 上 bank B 的用戶自定義信號,為差分信號對。

LA(00..33)_P、LA(00..33)_N:差分信號對,一般用于 LPC 或作HPC 中 bank A 的部分信號。

設計人員能依據這些明確的定義,合理規劃子卡和載卡的功能,確保各部分之間的信號傳輸和交互準確無誤,實現系統的預期功能。

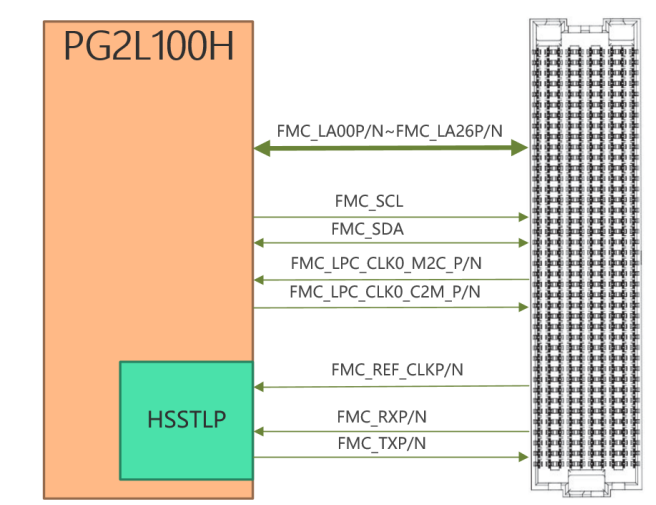

*盤古100pro+開發板FMC子板接口信號定義

FMC接口連接器分為HPC連接器和LPC連接器:

·HPC 連接器:具有400 引腳,排列方式為 40 行 ×10 列。提供 160 個用戶定義的單端信號或者 80 個用戶定義的差分對、10 個串行收發器對以及更多時鐘,可傳輸高速信號。

·LPC 連接器:有160 引腳,排列行不變,列只有 CDGH。除 68 個用戶定義的單端信號或者 34 個用戶定義的差分對外,還提供 1 個串行收發器對、時鐘、JTAG 接口和 1 個作為基礎智能平臺管理接口命令可選支持的 I2C 接口。

FMC接口支持高達10Gb/s 的信號傳輸速率,子卡和載卡之間潛在總帶寬達 40Gb/s。單端和差分信號傳輸速率可達 2Gb/s。

應用場景及優勢

FMC 標準能滿足多種應用場景需求,如智能采集系統、雷達 / 聲吶、實時視頻處理、無線通信等,開發板配備FMC 接口可讓用戶在不同應用領域快速搭建系統。

FPGA開發板常用FMC接口,有以下優點:

·設計重復利用性:采用FMC 標準,可將現有的 FPGA / 載卡設計重新用到新的 I/O 上,只需更換 FMC 模塊并對 FPGA 設計略作調整。

·兼容性:標準化的電源和規范的信號定義,使得不同廠家的FMC 子卡和載卡之間具有較好的兼容性。

·多I/O 特性:提供充足的I/O 數量,且引腳緊密排列,空間占用少,能夠滿足多種不同應用對 I/O 的需求。

市面上通常中高端及以上級別的FPGA 開發板會配備 FMC 接口

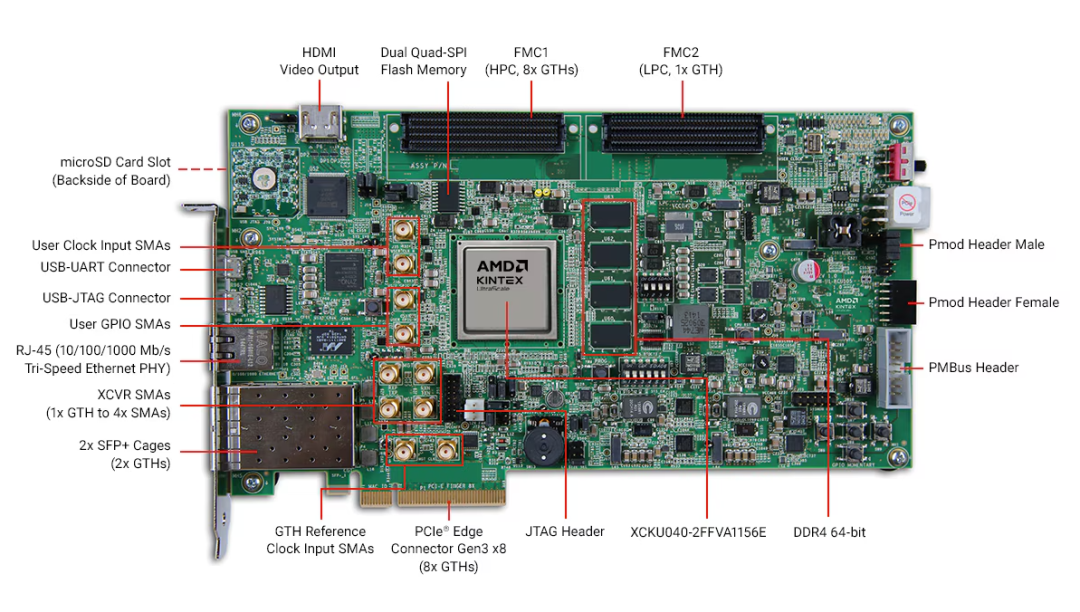

如:EK-U1-KCU105-G

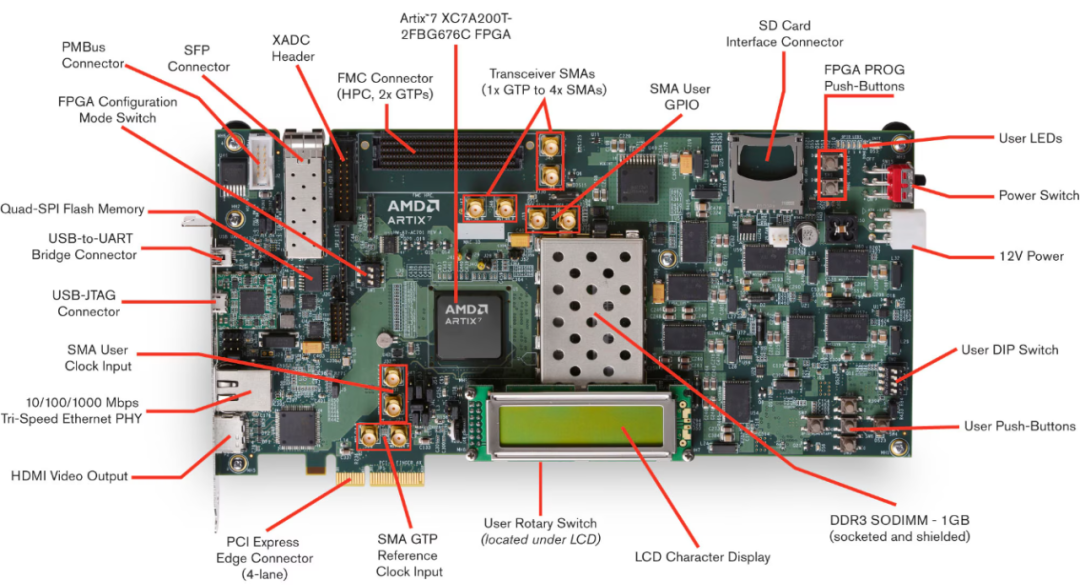

EK-A7-AC701-G

與傳統排針接口相比,FMC接口具有更高的數據傳輸能力,更節省空間,更具備兼容性、設計復用性和穩定性。

01

高數據傳輸能力

速率高:FMC 接口支持高達 10Gb/s 的信號傳輸速率,子卡和載卡之間潛在總帶寬達 40Gb/s,而傳統排針一般難以達到如此高的傳輸速率,無法滿足高速數據傳輸的需求。

信號質量好:FMC 連接器采用差分信號傳輸等技術,抗干擾能力強,能更好地保證高速信號傳輸的完整性和穩定性。傳統排針在高速信號傳輸時,容易受到電磁干擾等因素影響,導致信號失真、衰減。

02

高集成度與空間優勢

引腳密度高:FMC 連接器有 160 引腳的低引腳數(LPC)和 400 引腳的高引腳數(HPC)兩種類型,可在較小空間內提供大量 I/O 接口。

尺寸緊湊:FMC 標準定義了單寬度(69mm76.5mm)和雙寬度(139mm76.5mm)兩種尺寸,模塊設計緊湊,在對空間要求苛刻的應用中更具優勢3。

03

兼容性與靈活性

標準統一:FMC 有統一的標準,不同廠家的 FMC 子卡和載卡只要符合標準,就能相互兼容和連接。傳統排針通常沒有這樣統一嚴格的標準,不同廠家的排針在引腳定義、間距、電氣特性等方面可能存在差異,兼容性較差。

引腳分配靈活:FMC 接口可根據實際需求靈活分配引腳功能,能適應多種不同的應用場景和功能擴展。傳統排針的引腳功能通常在設計時就固定了,后期難以更改。

04

可靠性與穩定性

連接穩固:FMC 連接器通常采用 BGA 封裝等方式,與電路板的連接更加穩固,抗震性能好,能適應惡劣的工作環境。

抗干擾能力強:FMC 接口的信號完整性設計較好,具備良好的電磁兼容性,能有效抵抗外界電磁干擾,也不會對周圍環境產生過多的電磁輻射。傳統排針的抗干擾能力相對較弱,在電磁環境復雜的情況下,可能會影響系統的正常運行。

05

設計復用性

模塊可替換:采用FMC 標準的設計,可通過更換 FMC 模塊并對 FPGA 設計略作調整,將現有的 FPGA / 載卡設計應用到新的 I/O 上,提高了設計的復用性,縮短了開發周期,降低了成本。

便于升級維護:當需要對系統進行升級或維護時,只需更換相應的FMC 子卡,而無需對整個系統進行大規模的改動。傳統排針連接的系統在升級或維護時,可能需要重新設計和布線,工作量大,成本高。

盤古100Pro+開發板擴展底板預留了一組FMC LPC擴展口,符合FMC接口規范,可用于外接FMC模塊。

*盤古100 Pro+開發板FMC接口

盤古100Pro+開發板FMC擴展口共擴展24對差分IO(盤古200Pro+開發板FMC擴展口共擴展34對差分IO),1路I2C總線信號,一路 HSSTLP 高速串行數據收發信號以及為 HSSTLP 提供的一路參考時鐘。FMC擴展的差分信號分別連接在BANK L6、BANK L5、BANK L4、BANK L7上,其中BANK L6的IO電壓由L6_VADJ決定,BANK L7的IO電壓由L7_VADJ決定,底板L6_VADJ和L7_VADJ使用相同電源,可通過跳線帽座連接J20處和J24處的不同針腳決定為3.3V或2.5V或1.8V。

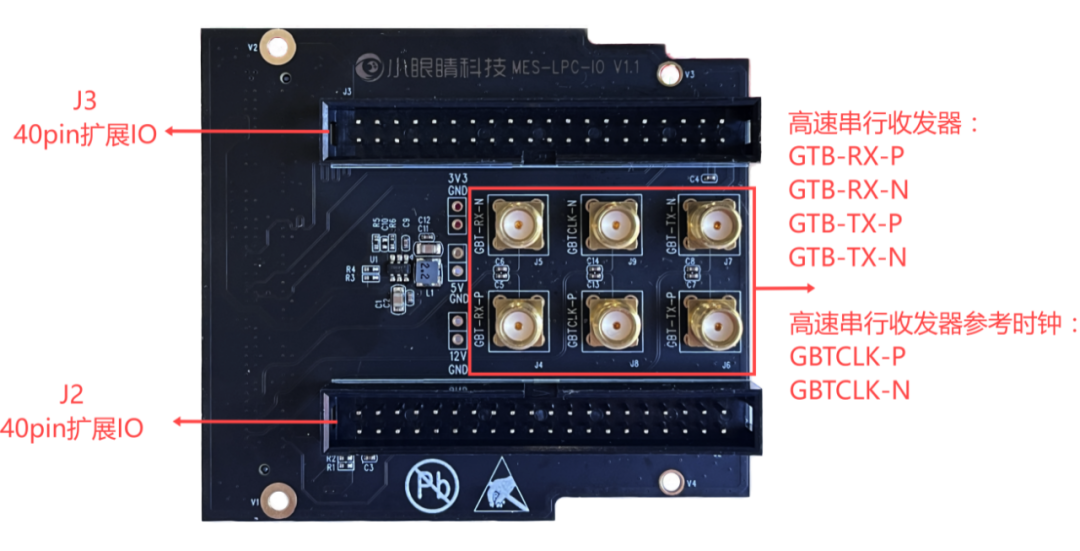

* FMC擴展IO子卡接口圖

FMC擴展IO子卡(型號:MES-FMC-LPC-IO)為FPGA開發板FMC接口擴展2路40pin擴展IO,共68個用戶IO,提供豐富的IO連接外部設備,40pin擴展IO與小眼睛科技FPGA開發板的40pin IO線序一致,配套外設模塊在子卡上可直接連接使用。FMC擴展子卡上6個SMA接口連接一路高速串行收發器和一路高速串行收發器參考時鐘輸入,支持高速數據傳輸。

FMC擴展IO子卡的2路40pin擴展IO可連接小眼睛科技雙目攝像頭模塊、ADC-DAC模塊、或通過PMOD擴展模塊連接多種PMOD模塊(如:音頻輸入模塊、音頻輸出模塊、1.3寸OLED屏模塊、分頻器模塊、蜂鳴器模塊等),此外擴展SMA_HSST接口可實現高速數據傳輸。

*FMC外接雙目攝像頭演示

*FMC外接ADDA模塊演示

-END-

-配套資料獲取-

淘寶購買鏈接:

手機版:https://h5.m.taobao.com/awp/core/detail.htm?ft=t&id=694482461265

網頁版:

https://item.taobao.com/item.htm?ft=t&id=694482461265&spm=a21dvs.23580594.0.0.1d292c1bdTj7cV

or 搜索店鋪:小眼睛半導體

原文標題:Why FPGA開發板喜歡FMC?

文章出處:【微信公眾號:小眼睛科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【國產FPGA入學必備】刀劍在鞘,兵器先藏 | 盤古676系列國產FPGA開發板

發布|CAE1200+FPGA開發板

Why FPGA開發板喜歡FMC?

Why FPGA開發板喜歡FMC?

評論