概述

AD9549為包括同步光纖網絡 (SONET/SDH)在內的許多系統(tǒng)提供同步。AD9549可以產生與兩個外部輸入基準之一同步的輸出時鐘。外部基準可能包含非常惡劣的時間抖動,或者相位噪聲。在基準丟失期間、甚至兩個基準都丟失的情況下,AD9549能夠利用數控環(huán)路和保持(holdover)電路連續(xù)產生有效的干凈的(低抖動)輸出時鐘。

AD9549工作溫度在工業(yè)溫度范圍,為-40°C ~ +85°C。

數據表:*附件:AD9549雙輸入網絡時鐘發(fā)生器 同步器技術手冊.pdf

應用

特性

- 靈活的基準輸入

- 輸入頻率8 kHz到750 MHz

- 兩個基本輸入

- 基準丟失指示器

- 自動與手動保持(Holdover)/轉換模式

- 自動與手動保持(Switchover)/轉換模式

- 平滑的A ~ B輸出相變

- 保持(holdover)模式具有卓越的穩(wěn)定性

- 可編程的16+1位輸入分配器

- 差分HSTL時鐘輸出

- 輸出頻率高達750 MHz

- 單端CMOS輸出;頻率<50MHz

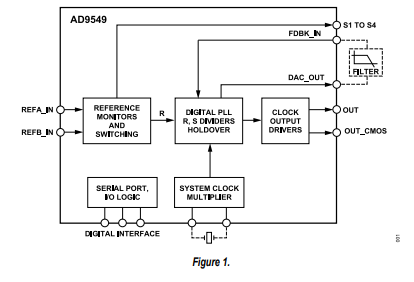

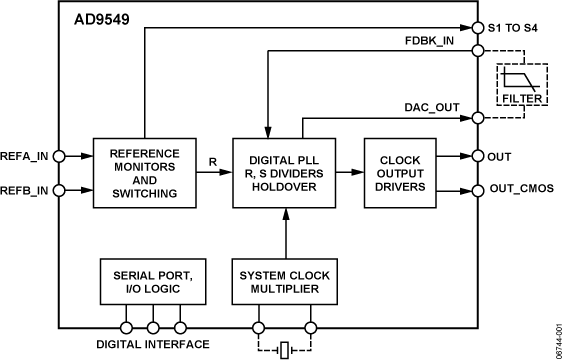

框圖

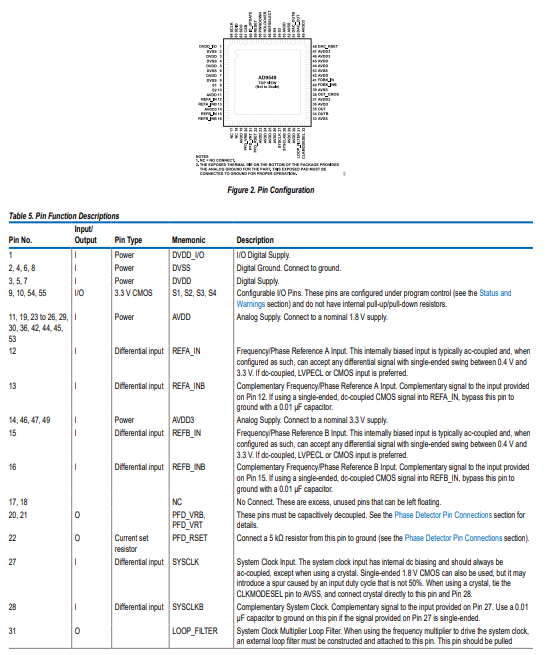

引腳配置描述

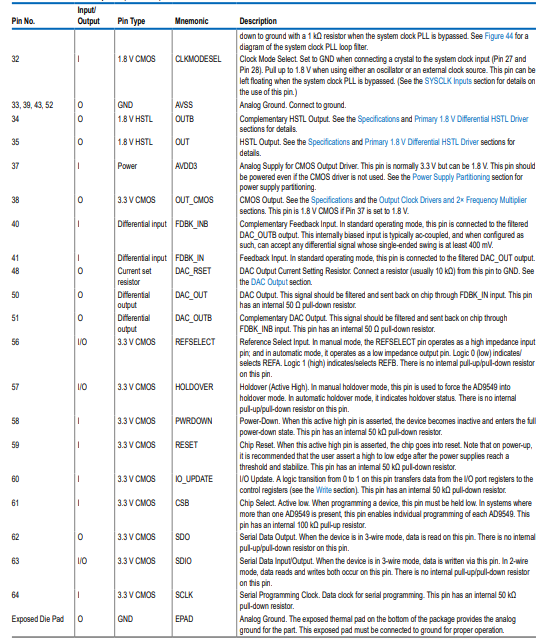

典型性能特征

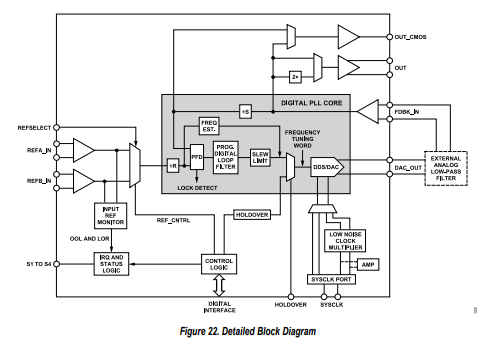

操作理論

AD9549 提供的時鐘輸出,其相位和頻率與所選的(激活的)參考信號(REFA 或 REFB)直接相關,但其相位噪聲頻譜主要由系統(tǒng)時鐘決定。參考頻率由支持的時鐘提供。現有參考信號中的抖動通過可編程數字濾波器(數字鎖相環(huán),PLL)大幅降低,這是本產品的核心技術。AD9549 支持手動和自動校準。在鎖定期間,AD9549 持續(xù)運行以提供輸出,只要系統(tǒng)時鐘保持正常工作。輸出頻率是系統(tǒng)時鐘在自動校準之前的穩(wěn)態(tài)輸出頻率的平均值。

此外,AD9549 還提供手動和自動切換模式,用于在兩個參考信號之間進行切換,以防其中一個信號出現故障或丟失。通過使用數字控制振蕩器(DCO)實現數字合成器(DDS),并集成數模轉換器(DAC),由系統(tǒng)時鐘對其進行時鐘控制。旁路 PLL 反饋頻率乘法器可使系統(tǒng)時鐘直接用作低頻源,以實現更好的抖動性能。應直接為數字頻率合成器提供采樣理論集上限,該上限為輸出頻率的 50%(其中 fs 是 DAC 速率),但實際限制為 40%,以便能夠選擇性地啟用片外重構濾波器。AD9549 的輸出信號會反饋到數字 PLL 中,完成 PLL 閉環(huán),并包括直通輸出電路。輸出電路包含 HSTL 和 CMOS 輸出緩沖器,以及用于 DDS 必須生成高于奈奎斯特電平頻率的混頻器設計。

各個功能模塊將在以下部分進行介紹。

數字鎖相環(huán)內核(DPLLC)

數字鎖相環(huán)內核(DPLLC)包含頻率估計模塊和驅動 DDS 的信號鏈鎖定控制模塊。

DPLLC 的起始信號是參考信號 (f_R) ,它出現在 REFA 或 REFB 輸入引腳上。該信號的頻率可通過前向分頻器按整數因子 (R) 進行分頻。前向分頻器的輸出是饋送到鑒頻鑒相器(PFD)的相位/頻率檢測信號。因此,PFD 的輸入頻率由下式給出:

PFD 輸出一系列數字字,這些數字字被路由到數字環(huán)路濾波器。數字濾波器的實現方式具有諸多優(yōu)勢:濾波器響應由數值系數而非離散元件值確定;不存在元件老化、漂移或隨時間變化的問題;不存在熱噪聲(在環(huán)路濾波器中),并且不存在控制節(jié)點泄漏電流(這會導致傳統(tǒng)模擬 PLL 中出現參考雜散)。

環(huán)路濾波器的輸出是一系列數字字。這些數字字被應用于 DDS 的頻率調諧輸入,以調節(jié) DCO 頻率。DDS 通過集成 DAC 有效地模擬了壓控振蕩器(VCO)的操作,從而產生模擬輸出信號。

-

發(fā)生器

+關注

關注

4文章

1401瀏覽量

62608 -

時鐘

+關注

關注

11文章

1887瀏覽量

132977 -

同步器

+關注

關注

1文章

106瀏覽量

15106 -

ad9549

+關注

關注

0文章

3瀏覽量

3805

發(fā)布評論請先 登錄

用于評估AD9549A 8kHz至750MHz輸入時鐘發(fā)生器的評估板AD9549A/PCBZ

ADI AD9547網絡時鐘發(fā)生與同步方案

雙輸入網絡時鐘發(fā)生器/同步器ad9549數據表

AD9549 雙輸入網絡時鐘發(fā)生器/同步器

如何選擇合適的時鐘發(fā)生器

毫微微時鐘網絡同步器、抖動衰減器和時鐘發(fā)生器RC32112A 數據表

AD9547雙路/四路輸入網絡時鐘發(fā)生器/同步器技術手冊

AD9549雙輸入網絡時鐘發(fā)生器/同步器技術手冊

AD9549雙輸入網絡時鐘發(fā)生器/同步器技術手冊

評論