概述

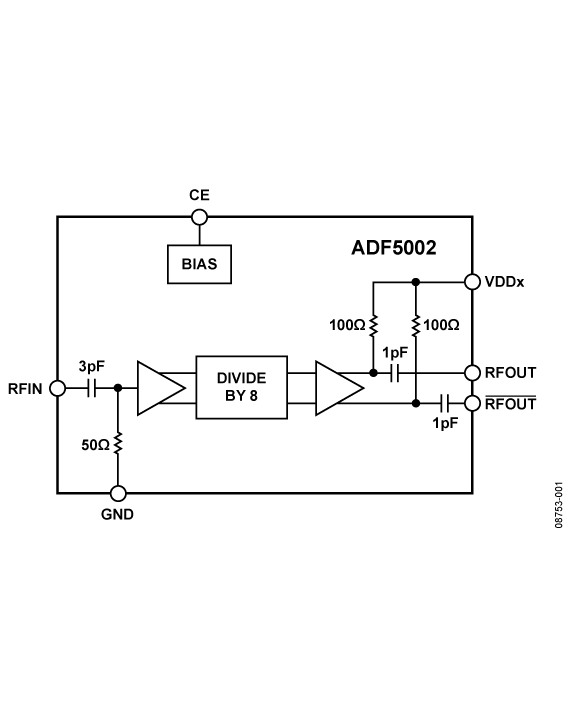

ADF5002預分頻器是一款低噪聲、低功耗、固定RF分頻器模塊,可用來將高達18GHz的頻率分頻至適合輸入到 [ADF4156]或[ADF4106]等PLL IC的較低頻率。ADF5002提供8分頻功能,采用3.3V電源供電,具有差分100Ω RF輸出,可以直接與ADF4156和ADF4106等PLL的差分RF輸入接口。

數據表:*附件:ADF5002 4GHz至18GHz 8分頻預分頻器技術手冊.pdf

應用

- PLL 頻率范圍擴展器

- 點對點無線電

- VSAT無線電

- 通信測試設備

特性

- 8分頻預分頻器

- 高工作頻率:4GHz至18GHz

- 集成RF去耦電容

- 低功耗

主動模式: 30 mA省電模式: 7 mA - 低相位噪聲:?150dBc/Hz

- 單直流電源:3.3V,兼容ADF4xxxPLL

- 溫度范圍:?40°C至+105°C

- 小型封裝:3mm×3mmLFCSP

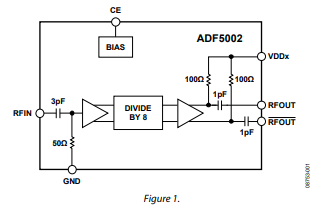

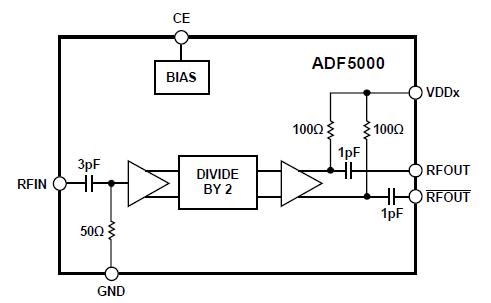

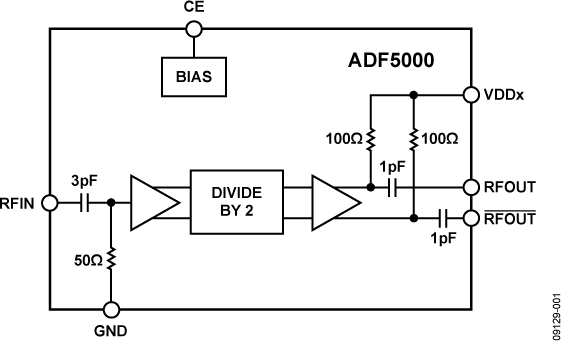

框圖

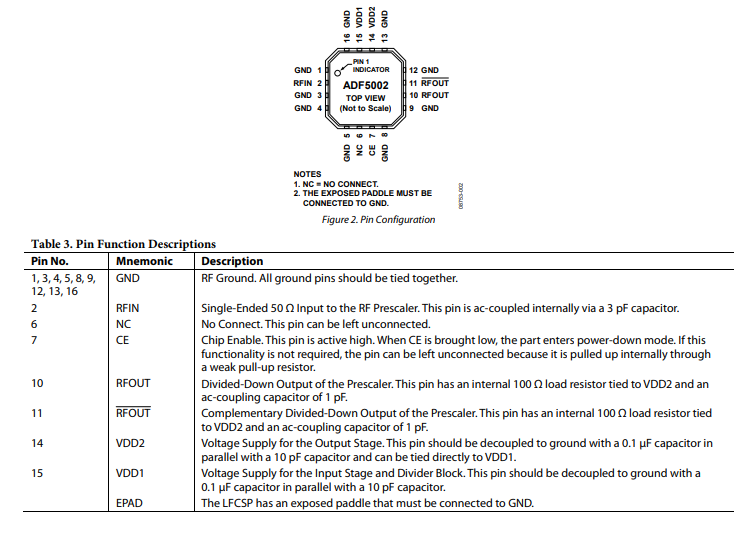

引腳配置描述

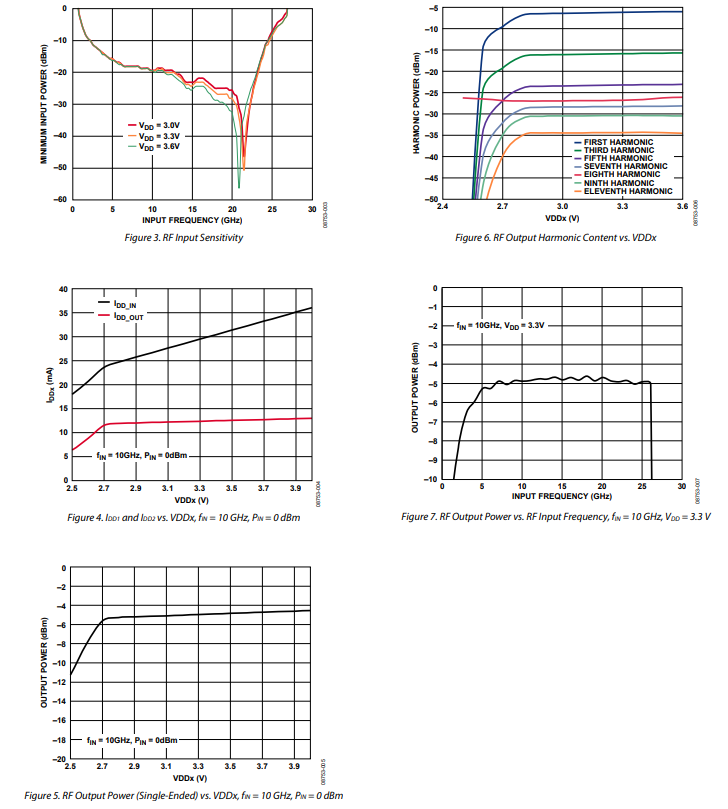

典型性能特征

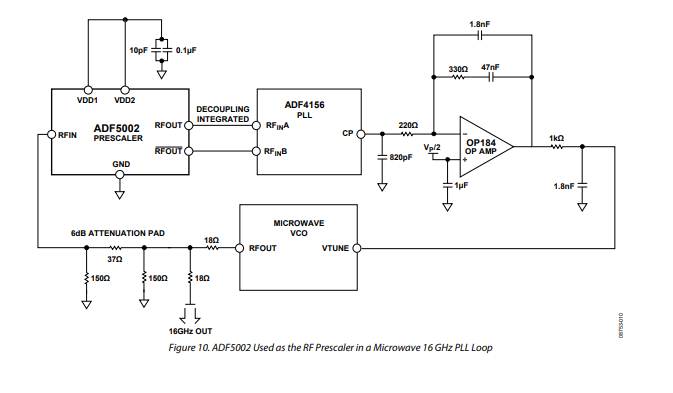

應用電路

ADF5002可以單端或差分方式連接到亞德諾半導體(Analog Devices)鎖相環(PLL)系列的任意一款芯片。為實現最佳性能并達到最大功率傳輸,建議采用差分連接方式。圖10所示的應用電路展示了ADF5002的情況。ADF5002用作射頻預分頻器,接入微波16 GHz鎖相環(PLL)。ADF5002將16 GHz射頻信號分頻至2 GHz,隨后以差分方式輸入到ADF4156鎖相環中。采用由OP184運算放大器構成的有源濾波器拓撲結構,為微波壓控振蕩器(VCO)提供所需的寬范圍調諧電壓。

OP184的正輸入引腳偏置為ADF4156電荷泵電源(V?)電壓的一半。這可通過簡單的電阻分壓器輕松實現,同時要確保在OP184的+IN引腳附近進行充分去耦。這樣的配置使得能夠使用單個正電源為運算放大器供電。或者,為優化性能,可通過確保干凈的偏置電壓,使用低噪聲調節器(如ADP150 ),為電阻分壓器網絡供電,或直接為+IN引腳供電。

-

分頻器

+關注

關注

43文章

492瀏覽量

51093 -

RF

+關注

關注

65文章

3175瀏覽量

168847 -

ADF5002

+關注

關注

0文章

3瀏覽量

1352

發布評論請先 登錄

ADI公司推出低功耗射頻預分頻器-- ADF500x

ADI 公司推出低功耗射頻預分頻器

4千兆赫至18千兆赫八分頻分頻器ADF5002數據表

ADF5002 4GHz 至18GHz _8分頻預分頻器

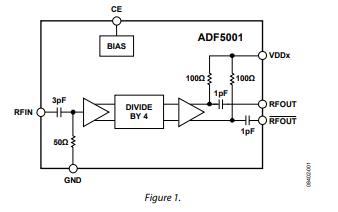

ADF5001 4GHz 至18GHz _4分頻預分頻器

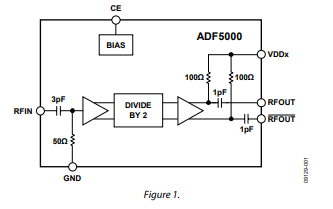

ADF5000 4GHz 至18GHz 2分頻預分頻器

HMC434:0.2 GHz至8 GHz,GaAs,HBT MMIC,除以8個預分頻器數據表

ADF5002 4GHz至18GHz 8分頻預分頻器技術手冊

ADF5002 4GHz至18GHz 8分頻預分頻器技術手冊

評論