一、前言

DDR SDRAM,即雙數(shù)據(jù)速率同步動態(tài)隨機(jī)存取存儲器,是現(xiàn)代數(shù)字系統(tǒng)中至關(guān)重要的一種核心組件,其應(yīng)用范圍極其廣泛。無論是在消費(fèi)電子產(chǎn)品中,還是在商業(yè)和工業(yè)設(shè)備里,亦或是從終端產(chǎn)品到數(shù)據(jù)中心,DDR SDRAM均作為CPU進(jìn)行數(shù)據(jù)處理和運(yùn)算的緩存發(fā)揮著不可或缺的作用。過去二十多年間,存儲技術(shù)經(jīng)歷了從SDRAM向DDR RAM的重大演進(jìn),直至今日的DDR5。每一代DDR技術(shù)都在帶寬、性能以及功耗等方面實(shí)現(xiàn)了顯著的改進(jìn),極大地促進(jìn)了計(jì)算性能的飛躍發(fā)展。這一技術(shù)的進(jìn)步不僅推動了個人電子設(shè)備的革新,也對大規(guī)模數(shù)據(jù)中心的高效運(yùn)作產(chǎn)生了深遠(yuǎn)影響。

二、DDR標(biāo)準(zhǔn)發(fā)展和DDR5簡介

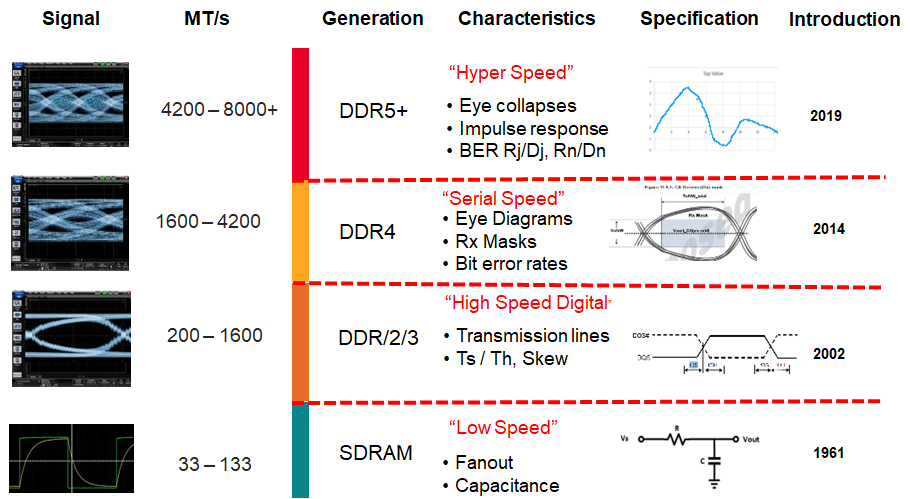

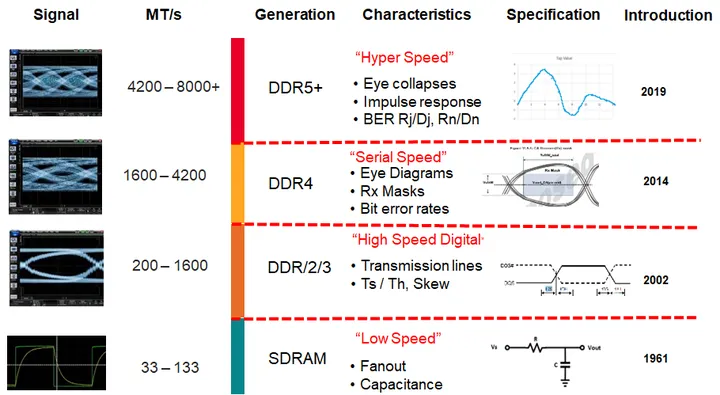

圖1展示了過去20多年來RAM(隨機(jī)存取存儲器)的發(fā)展歷程及其信號特點(diǎn)。在SRAM時期,由于信號速率相對較低,設(shè)計(jì)時主要關(guān)注的是信號的扇出和布線引起的容性負(fù)載問題。然而,隨著DDR1/2/3時代的到來,信號速率顯著提升,傳統(tǒng)的基于集總參數(shù)的電路分析方法已難以滿足需求,此時更需關(guān)注信號的建立與保持時間以及信號線間的延遲差異(skew)。

進(jìn)入DDR4時代后,受限于PCB、連接器等傳輸通道的有限帶寬,原始信號中的高頻成分可能會被削弱甚至完全去除,這導(dǎo)致信號的時域波形出現(xiàn)邊沿變緩、振鈴或過沖的現(xiàn)象。因此,在這一階段,對于數(shù)據(jù)眼圖、接收端模板及誤碼率的關(guān)注變得尤為重要,就如同分析傳統(tǒng)串行數(shù)據(jù)一樣。

面對AI、機(jī)器學(xué)習(xí)和5G技術(shù)的迅猛發(fā)展,DDR4逐漸顯現(xiàn)出其局限性。為此,第5代高速I/O數(shù)據(jù)傳輸技術(shù)——DDR5應(yīng)運(yùn)而生,并開始廣泛走向市場,以應(yīng)對新一代技術(shù)對存儲器性能的更高要求。

圖1 DDR標(biāo)準(zhǔn)發(fā)展和信號特點(diǎn)演進(jìn)

2.1 DDR5的新特性

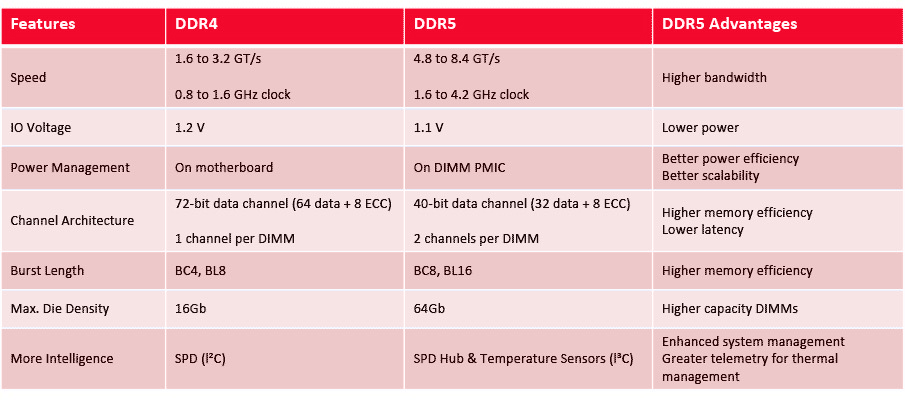

如下表所示,DDR5相比DDR4而言,帶來了一系列關(guān)鍵的性能提升,同時也帶來了新的設(shè)計(jì)挑戰(zhàn)。

表1 DDR4和DDR5比較(源自Rambus)

2.1.1 速率的提升

近年來,內(nèi)存與CPU性能發(fā)展之間的差距逐漸拉大,對內(nèi)存帶寬的需求變得愈加緊迫。在1.6GHz的時鐘頻率下,DDR4能夠?qū)崿F(xiàn)最高達(dá)3.2 GT/s的傳輸速率。相較之下,初代DDR5便將帶寬提升了50%,實(shí)現(xiàn)了4.8 GT/s的傳輸速率。而隨著技術(shù)的進(jìn)步,DDR5內(nèi)存的數(shù)據(jù)傳輸速率預(yù)期最終將達(dá)到8.4 GT/s的高速度。這一演進(jìn)不僅緩解了內(nèi)存帶寬的瓶頸問題,也為系統(tǒng)性能的整體提升提供了強(qiáng)有力的支持。

2.1.2 電壓的降低

降低工作電壓(VDD)有助于平衡因高速運(yùn)行帶來的功耗增加。在DDR5 DRAM中,寄存時鐘驅(qū)動器(RCD)的工作電壓從1.2V降低到了1.1V。此外,命令/地址(CA)信號的邏輯類型從SSTL(Stub Series Termination Logic)轉(zhuǎn)換為PODL(Pseudo Open Drain Logic)。這種轉(zhuǎn)變的優(yōu)勢在于,當(dāng)引腳處于高電平狀態(tài)時不會消耗靜態(tài)功率,從而進(jìn)一步降低了整體功耗。這些改進(jìn)使得DDR5在提升速度的同時,還能保持較低的能耗,實(shí)現(xiàn)了性能與能效的雙重優(yōu)化。

2.1.3 DIMM 新電源架構(gòu)

在使用DDR5 DIMM時,電源管理將從主板轉(zhuǎn)移至DIMM自身。具體來說,DDR5 DIMM將在模塊上配備一個12V電源管理集成電路(PMIC),從而實(shí)現(xiàn)更精細(xì)的系統(tǒng)電源負(fù)載分配。此PMIC負(fù)責(zé)提供1.1V的工作電壓(VDD),通過在DIMM層面精準(zhǔn)控制電源,不僅有助于提升信號完整性,還能有效減少噪音干擾。這樣的設(shè)計(jì)改進(jìn),使得DDR5 DIMM在性能提升的同時,也確保了更高的可靠性和穩(wěn)定性。

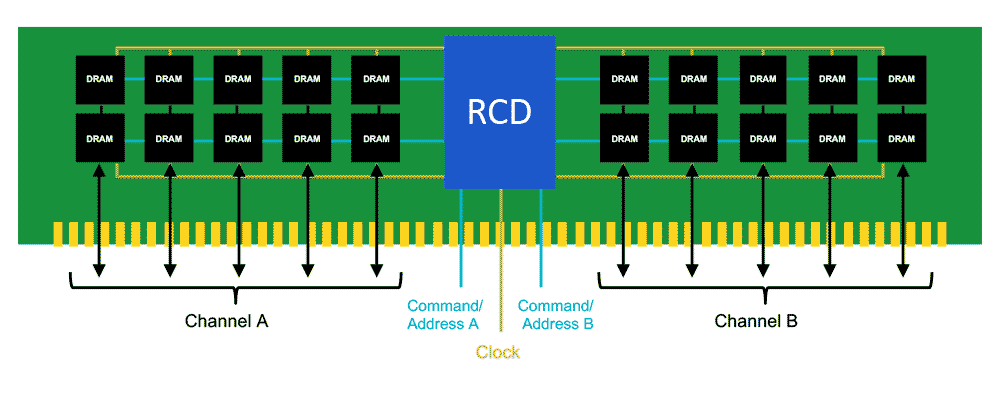

2.1.4 DIMM通道架構(gòu)

DDR4 DIMM配備了一個72位寬的總線,其中包括64個數(shù)據(jù)位和8個ECC位,用于錯誤檢測與糾正。而在DDR5中,每個DIMM被設(shè)計(jì)為包含兩個通道,每個通道寬度為40位,其中32位用于數(shù)據(jù)傳輸,8位專用于ECC。盡管在數(shù)據(jù)寬度上,DDR5與DDR4相同(總共64位),但DDR5通過采用兩個獨(dú)立的小型通道來提高內(nèi)存訪問效率。這種設(shè)計(jì)不僅支持更高的速度,還通過增強(qiáng)的數(shù)據(jù)處理效率進(jìn)一步放大了傳輸速率的優(yōu)勢。因此,DDR5不僅能帶來更快的速度,還確保了更高效的數(shù)據(jù)訪問和處理性能。

2.1.5 更長的突發(fā)長度

DDR4的突發(fā)長度設(shè)定為4或8,而在DDR5中,這一數(shù)值被擴(kuò)展到了8和16,以增加每次突發(fā)傳輸?shù)臄?shù)據(jù)量。具體來說,DDR5支持的突發(fā)長度為16(BL16),這意味著它可以單次突發(fā)訪問達(dá)到64字節(jié)的數(shù)據(jù),正好與典型的CPU高速緩存行大小相匹配。值得注意的是,借助于DDR5雙通道設(shè)計(jì)中的任意一個獨(dú)立通道即可實(shí)現(xiàn)這樣的數(shù)據(jù)訪問能力。因此,這不僅大幅提升了數(shù)據(jù)并發(fā)處理能力,同時也通過充分利用兩個通道增強(qiáng)了內(nèi)存使用的效率。這種改進(jìn)使得DDR5在提升數(shù)據(jù)傳輸速率的同時,也顯著優(yōu)化了整體性能和響應(yīng)速度。

2.1.6 更大容量的 DRAM

DDR4在單芯片封裝(SDP)中的最大容量為16Gb DRAM。相比之下,DDR5的單芯片封裝最大容量提升至64Gb,這意味著通過DDR5技術(shù)組建的DIMM容量可以達(dá)到驚人的256GB,是原先的四倍之多。這一顯著的增長,不僅滿足了現(xiàn)代計(jì)算對高容量內(nèi)存的需求,也為處理復(fù)雜和數(shù)據(jù)密集型任務(wù)提供了強(qiáng)有力的支持。

2.2 DDR5 設(shè)計(jì)面臨的挑戰(zhàn)

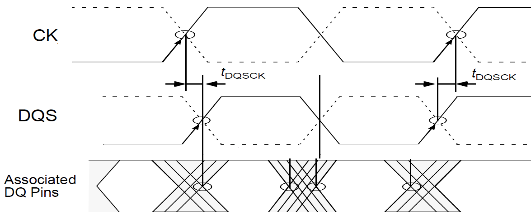

2.2.1采用分離式全速率時鐘,對應(yīng)6400M T/s頻率的時鐘速率高達(dá)3.2GHz(未來會支持到8400M T/s)。

DDR5 DQS控制DQ讀寫時序

時鐘控制命令信號,選通信號控制數(shù)據(jù)。對時鐘信號抖動的要求更加嚴(yán)格,對各種命令信號與數(shù)據(jù)和地址信號的時序要求也更高。

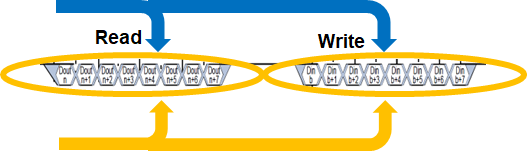

2.2.2 雙向復(fù)用的數(shù)據(jù)總線,讀寫數(shù)據(jù)分時復(fù)用鏈路。

由于鏈路通道和布板空間等資源的限制,讀寫操作不得不繼續(xù)共享同一總線,并因此需要采用分時復(fù)用的方式進(jìn)行。從驗(yàn)證和測試的角度來看,這也意味著需要分別對讀和寫信號進(jìn)行隔離檢查,以確保它們各自符合規(guī)范要求。這種做法不僅有助于保證數(shù)據(jù)傳輸?shù)目煽啃裕瑫r也為優(yōu)化性能提供了必要的診斷支持。通過這種方式,可以有效地識別并解決潛在的信號完整性問題,確保系統(tǒng)的穩(wěn)定運(yùn)行。

DDR5讀寫共享總線

2.2.3突發(fā)DQS和DQ信號在更高速率的背景下在有限帶寬的鏈路傳輸時帶來更多ISI效應(yīng)問題。

在DQS(數(shù)據(jù)選通信號)的讀寫前導(dǎo)位以及突發(fā)序列的第一個比特等方面,均表現(xiàn)出不同的效應(yīng)和特性。此外,由于存儲電路在設(shè)計(jì)上與串行電路存在顯著差異,導(dǎo)致阻抗不匹配問題較為常見,這使得反射問題及干擾引發(fā)的ISI(碼間干擾)更為嚴(yán)重。存儲器系統(tǒng)中這些復(fù)雜的信號完整性挑戰(zhàn),要求更加精細(xì)的設(shè)計(jì)和優(yōu)化措施,以確保高效、可靠的數(shù)據(jù)傳輸。通過解決這些問題,可以有效提升整體系統(tǒng)的穩(wěn)定性和性能表現(xiàn)。

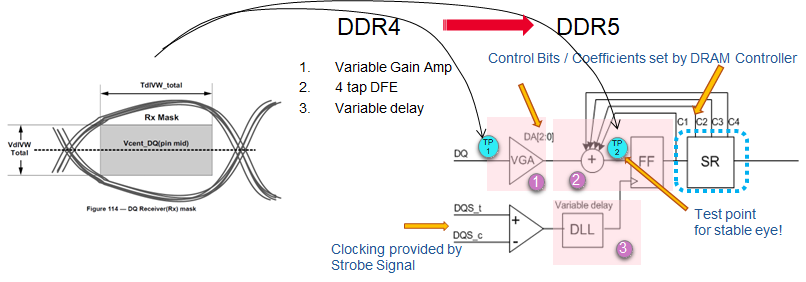

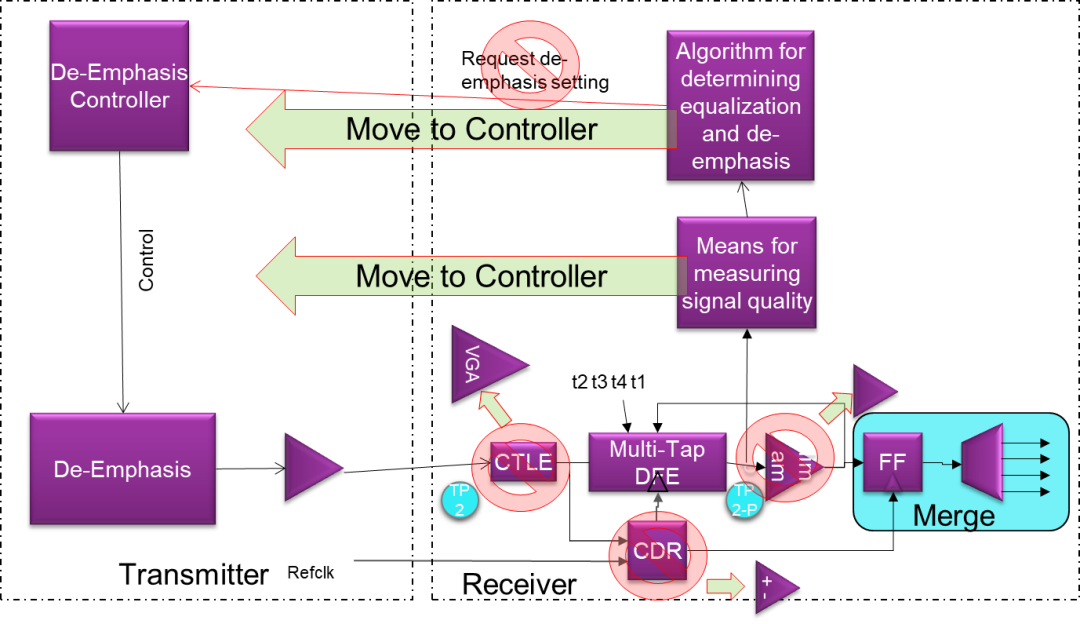

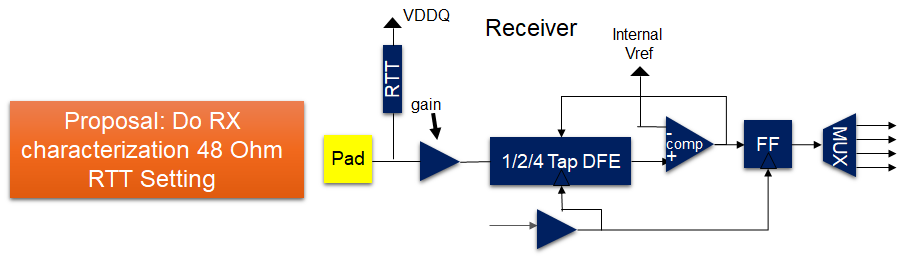

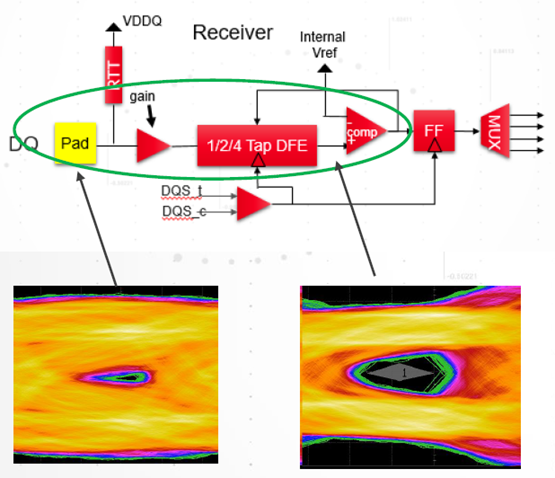

DDR5在接收端采用更多的類似高速串行總線的信號處理

因此,在接收端數(shù)據(jù)速率超過3600 MT/s時,采用類似高速串行電路和標(biāo)準(zhǔn)總線中已成熟應(yīng)用的判決反饋均衡(DFE)技術(shù),可以有效應(yīng)對信號完整性挑戰(zhàn)。可變增益放大(VGA)則通過MR寄存器進(jìn)行配置,以補(bǔ)償在更高傳輸速率下鏈路中的損耗。盡管DDR4標(biāo)準(zhǔn)采用的連續(xù)時間線性均衡(CTLE)是一種簡單易實(shí)現(xiàn)的線性均衡方法,但它往往會放大噪聲,這在高速率傳輸時成為一個不容忽視的問題。相比之下,DDR5總線設(shè)計(jì)中未采用CTLE,主要是考慮到反射噪聲的影響。此外,隨著并行總線中串?dāng)_和反射現(xiàn)象的增加,各信號抖動的定義和分析方法也隨之發(fā)生變化,這要求更加細(xì)致的評估與處理策略來確保信號完整性和系統(tǒng)穩(wěn)定性。通過這些優(yōu)化措施,DDR5能夠在保持高數(shù)據(jù)傳輸速率的同時,提供更佳的信號質(zhì)量和可靠性。

三、DDR5的測試新方法

3.1 發(fā)送端TX測試挑戰(zhàn)

3.1.1 讀寫分離

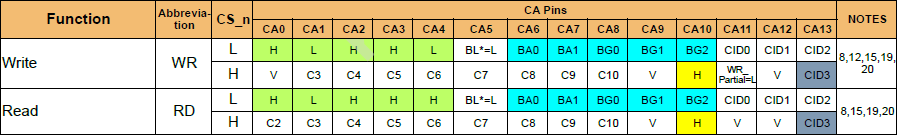

根據(jù)DDR5的規(guī)范,其不再像傳統(tǒng)DDR那樣在引腳處對讀寫操作有嚴(yán)格的相位差異。這意味著依賴DQS(數(shù)據(jù)選通)和DQ(數(shù)據(jù))之間的相位差以及前置信號模式的傳統(tǒng)方法可能不再適用于讀寫數(shù)據(jù)的分離。因此,需要采用新的方法來區(qū)分讀寫數(shù)據(jù)。

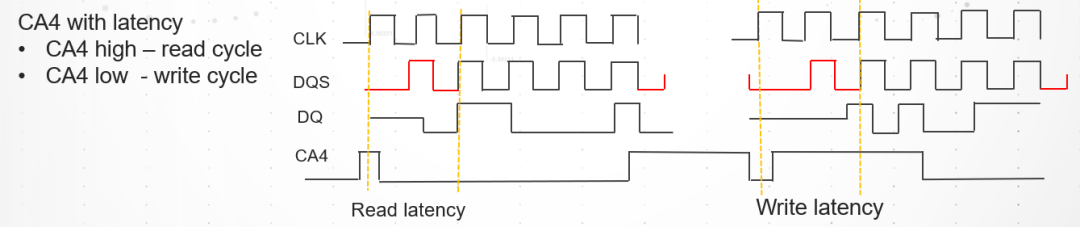

在DDR5中,可以通過觀察發(fā)現(xiàn)CA4(命令/地址信號之一)在讀寫操作期間表現(xiàn)出不同的邏輯電平。基于這一特性,可以利用CA4的狀態(tài)結(jié)合讀寫延遲來進(jìn)行讀寫數(shù)據(jù)的有效分離。具體來說,通過分析真值表中CA4在不同操作下的邏輯狀態(tài),可以更準(zhǔn)確地識別并分離出讀操作與寫操作的數(shù)據(jù)流,從而確保數(shù)據(jù)傳輸?shù)臏?zhǔn)確性和效率。這種方法不僅適應(yīng)了DDR5的新特性,也為實(shí)現(xiàn)更高效的存儲器控制提供了可能。

3.1.2新增的測試參數(shù)

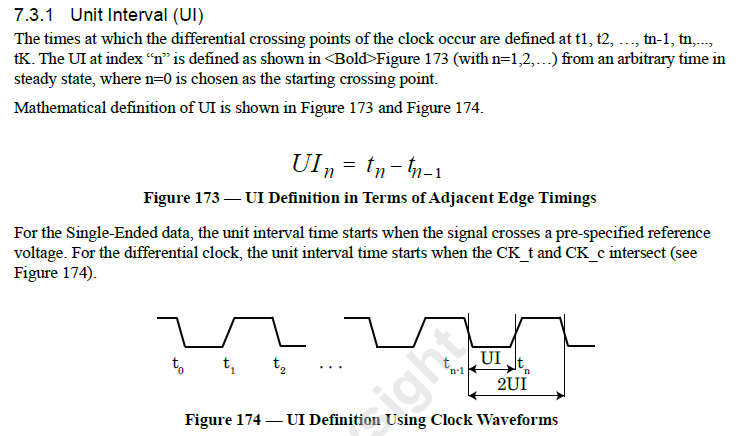

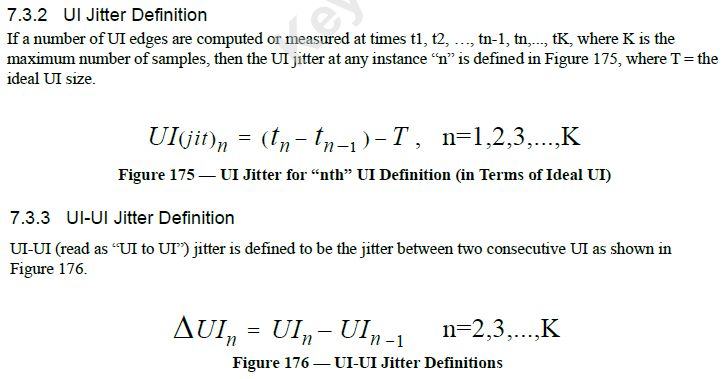

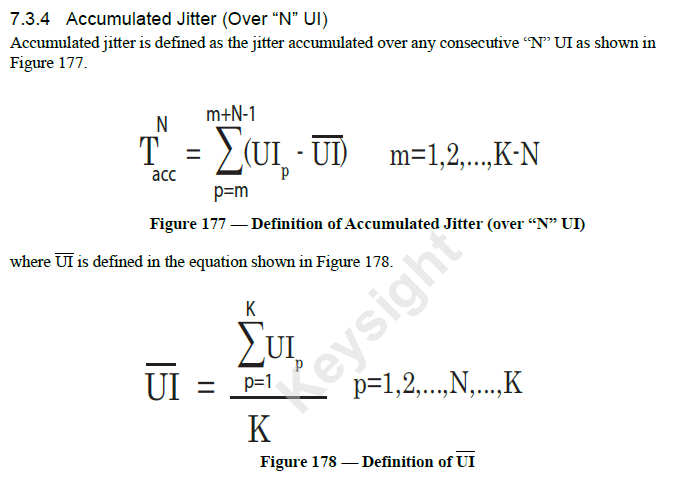

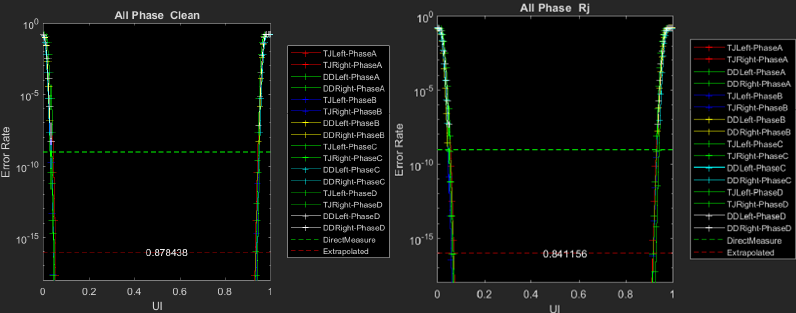

由于速率的提高,可能需要新的測試參數(shù)來鑒定關(guān)鍵信號。抖動成為關(guān)鍵信號的重要組成部分。規(guī)范定義了全新的UI抖動定義。

以及針對該UI的測量算法。

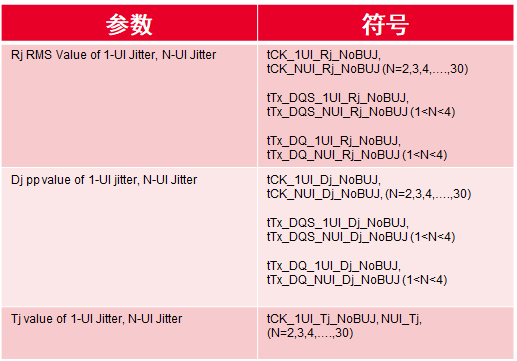

UI的測量項(xiàng)將覆蓋CLK(input)、DQS(tx)和DQ(tx) 信號,且要求非常嚴(yán)格。

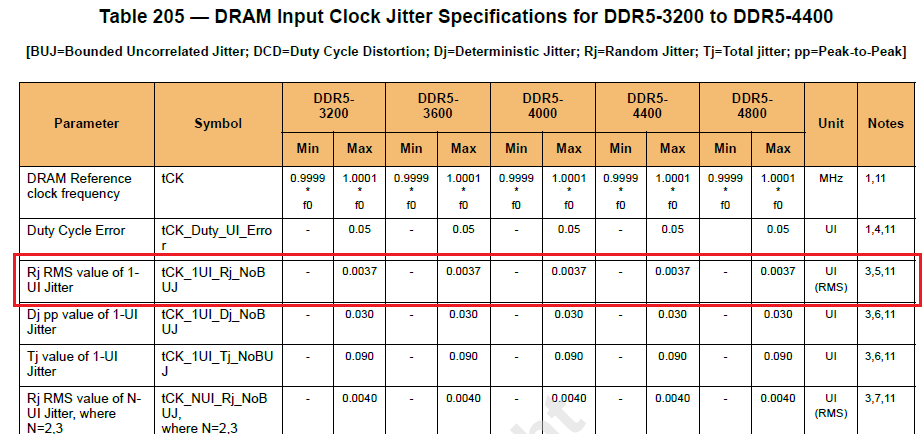

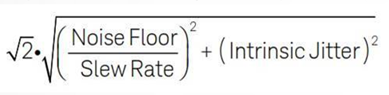

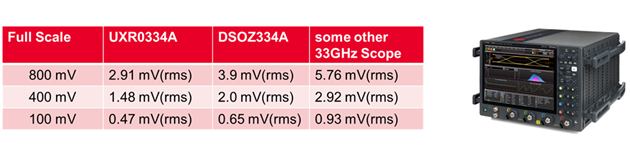

根據(jù)下表的計(jì)算,按照DDR5 4800的速率為例,要求測量出來的Rj最大值為0.0037UI,也就是769.6fs。

如此高要求的測量結(jié)果,也對儀表本身的性能提出了非常高的要求。儀表的抖動測量本底計(jì)算公式如下,可以看出示波器的本底噪聲以及本底抖動,對抖動測量起了非常大的影響。

是德科技UXR旗艦級實(shí)時示波器,具有25fs的極低本底抖動,165μV(rms)(16G帶寬下) 的本底噪聲。可以提供可靠的DDR5的相關(guān)抖動測試。

3.1.3 測試方法

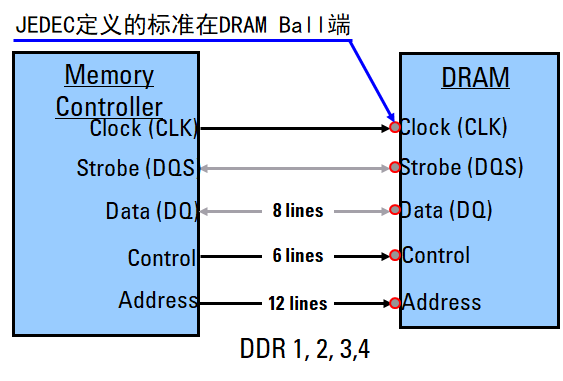

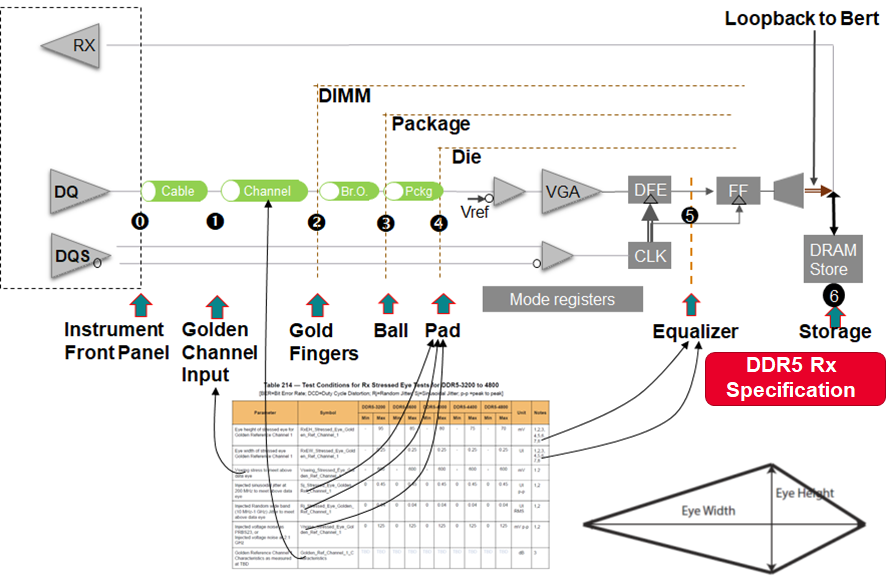

DDR的TX測量手法,一直是我們所關(guān)心的內(nèi)容。在DDR4以前,規(guī)范規(guī)定的測試點(diǎn),均在DRAM的ball處。DDR5里,除了眼圖測試以外,其他測試點(diǎn)沒有做額外更新。

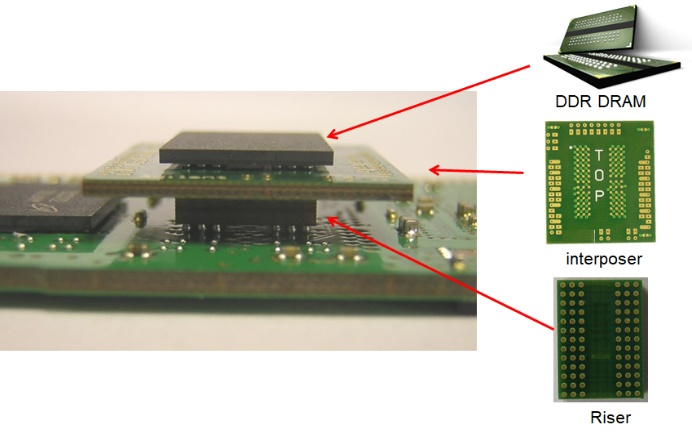

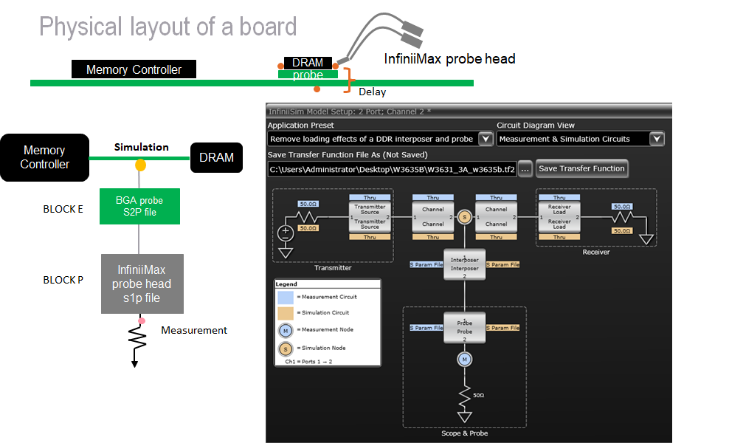

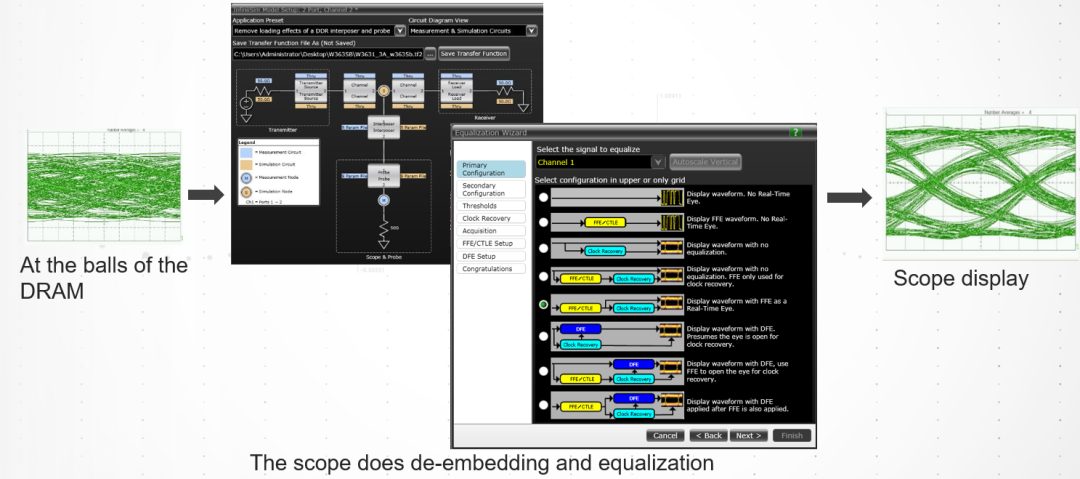

我們推薦使用interposer的方式來進(jìn)行測量,如下圖所示。

測量完成后,通過S參數(shù)的數(shù)學(xué)計(jì)算,實(shí)現(xiàn)從實(shí)測點(diǎn)到理論測試點(diǎn)的波形轉(zhuǎn)換。

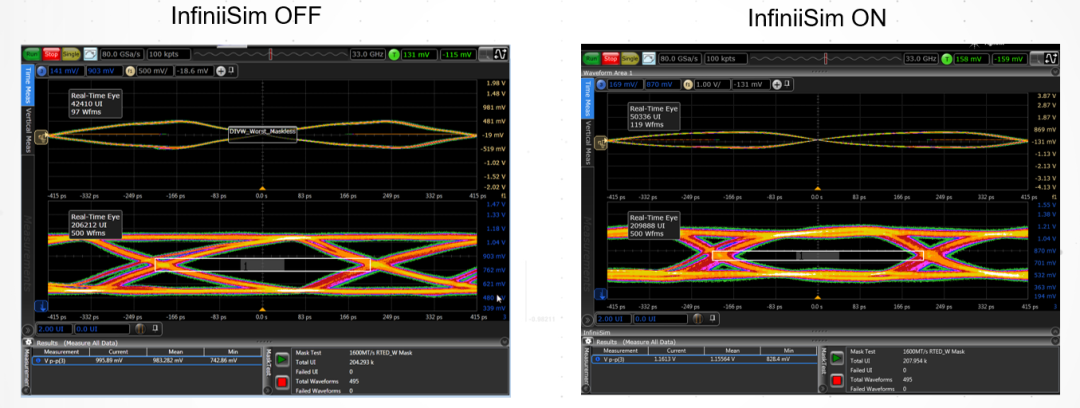

而針對于DDR5的眼圖測試,如果打開了DFE功能,示波器可以在去嵌的基礎(chǔ)上,進(jìn)一步完成均衡的操作,最后得到需要的波形。

當(dāng)然,是德科技已經(jīng)提供自動化的測試App,方便的給用戶提供可視化的一鍵測試方案。

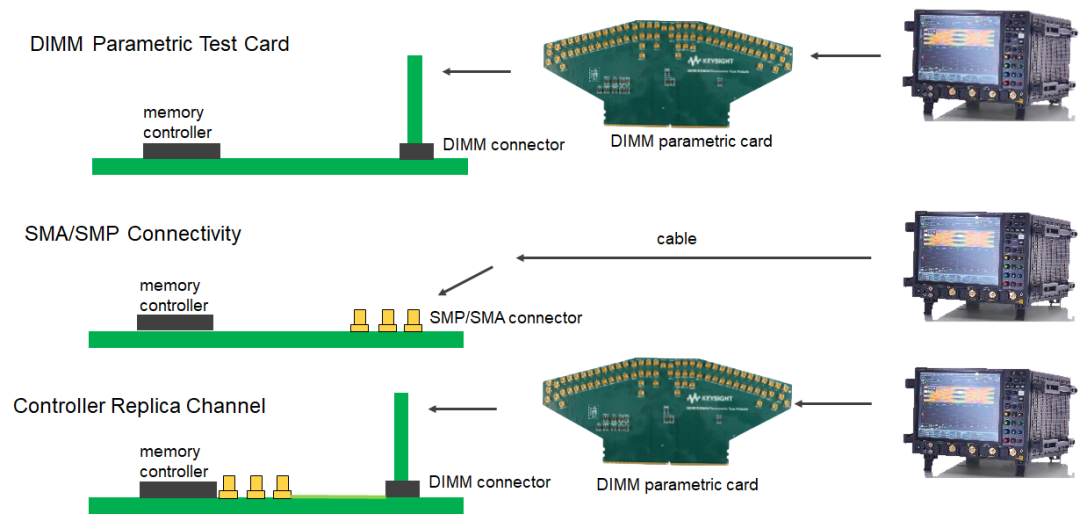

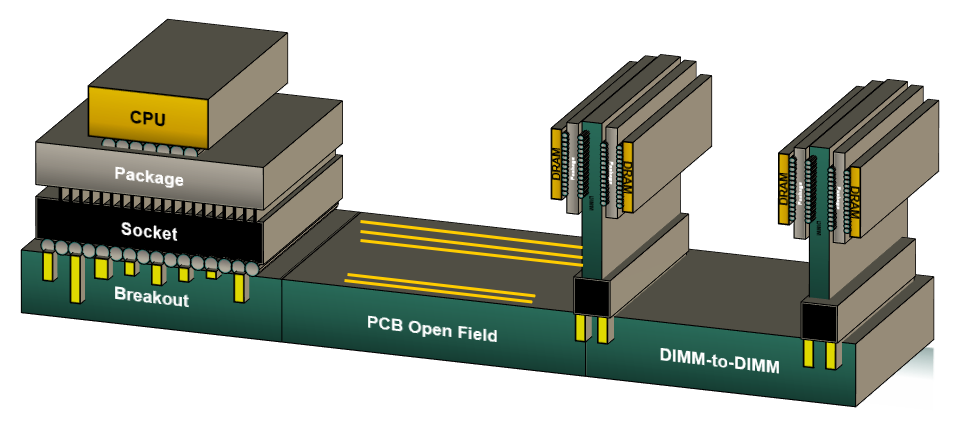

3.1.4 控制器測試新場景

隨著信號速率的不斷提升,控制器、PCB互聯(lián)鏈路以及芯片的測試變得尤為重要。下圖展示了一個針對控制器和PCB互聯(lián)鏈路的發(fā)送端(TX)測試場景。在此場景中,通過使用示波器并配合特定的測試夾具,可以有效地進(jìn)行發(fā)送端的信號質(zhì)量測試。這種測試方法能夠幫助檢測和評估高速信號傳輸過程中的各種參數(shù),如信號完整性、噪聲水平和定時誤差等,從而確保整個系統(tǒng)的穩(wěn)定性和可靠性。通過這種方式,可以及時發(fā)現(xiàn)潛在問題,并采取相應(yīng)的優(yōu)化措施,以適應(yīng)日益增長的高速數(shù)據(jù)傳輸需求。

3.2 接收端RX測試挑戰(zhàn)

3.2.1 接收端新技術(shù)

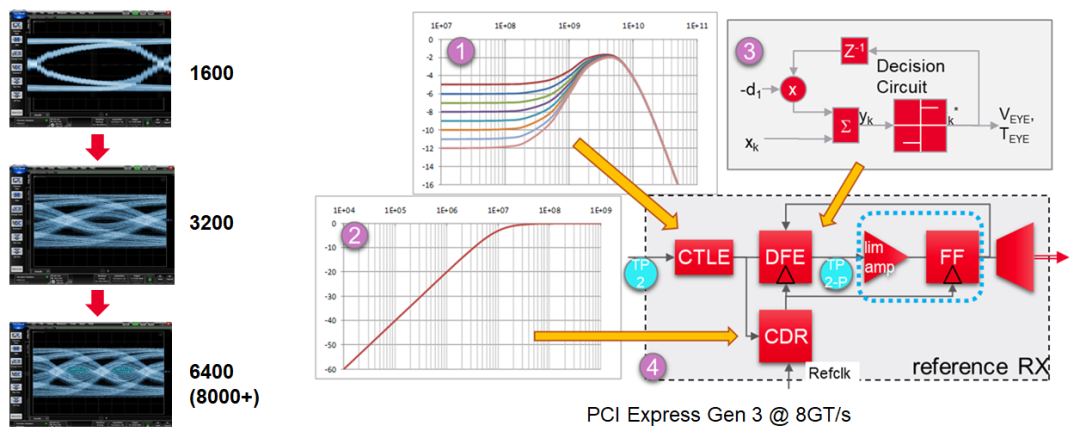

在以往的高速串行鏈路設(shè)計(jì)中,隨著數(shù)據(jù)傳輸速率的不斷提升,鏈路損耗和碼間干擾(ISI)對信號高頻分量的影響變得越來越顯著。因此,在PCIe Gen3的設(shè)計(jì)中,引入了接收端均衡的概念,以彌補(bǔ)因這些因素導(dǎo)致的高頻分量損失。通過這種方法,可以有效恢復(fù)在傳輸過程中衰減的高頻信號,確保數(shù)據(jù)傳輸?shù)耐暾院涂煽啃浴=邮斩司饧夹g(shù)的應(yīng)用,標(biāo)志著向更高效率和更穩(wěn)定的數(shù)據(jù)傳輸邁進(jìn)了一大步,為后續(xù)高速數(shù)據(jù)通信標(biāo)準(zhǔn)的發(fā)展奠定了基礎(chǔ)。

具體來看,有以下幾個關(guān)鍵點(diǎn):

接收端的信號首先會經(jīng)過連續(xù)時間線性均衡(CTLE)處理。圖中展示的是具有7個DC增益設(shè)置的CTLE響應(yīng)曲線。這一步驟旨在初步補(bǔ)償信道損耗,并增強(qiáng)高頻分量。

經(jīng)過CTLE均衡后的信號會被分成兩路:一路進(jìn)入時鐘數(shù)據(jù)恢復(fù)(CDR)電路。在CDR中,核心PLL的等效傳遞函數(shù)類似于一個高通濾波器,有助于從輸入信號中提取出穩(wěn)定的時鐘信息。

另一路信號則被送入帶有單抽頭的判決反饋均衡(DFE)。DFE的作用是在檢測到的數(shù)據(jù)符號基礎(chǔ)上進(jìn)一步消除碼間干擾。

值得注意的是圖中標(biāo)注的兩個測試點(diǎn)TP2和TP2'。通常情況下,TP2是使用示波器實(shí)際捕獲到的信號波形,而TP2'則是通過標(biāo)準(zhǔn)參考接收機(jī)模型生成的,用來模擬芯片實(shí)際接收到的波形。

a)

全速率時鐘

接收端沒有PLL

b)

單端信號

數(shù)量眾多,不僅要考慮損耗帶來的影響,更多的還需要考慮串?dāng)_帶來的影響

c)

分布式

多顆粒應(yīng)用場景,每片顆粒獨(dú)立的訓(xùn)練和均衡

了解了DDR5和傳統(tǒng)Serdes的幾個特別之處外,參考在PCIE上使用的均衡技術(shù),進(jìn)行了部分調(diào)整后如下。

首先,在時鐘數(shù)據(jù)恢復(fù)(CDR)方面,由于系統(tǒng)中已存在顯示時鐘,可以使用不具備頻率跟蹤能力的延遲鎖定環(huán)(DLL)模塊來替代原本復(fù)雜的CDR模塊。這不僅簡化了設(shè)計(jì),還提高了系統(tǒng)的穩(wěn)定性和可靠性。

其次,關(guān)于連續(xù)時間線性均衡(CTLE),盡管其實(shí)現(xiàn)相對簡單,但由于單端DDR5總線中存在的反射和串?dāng)_問題,嚴(yán)重影響了信噪比。因此,選擇使用可變增益放大器(VGA)來代替CTLE,以更好地適應(yīng)復(fù)雜的信號環(huán)境,并有效提升信號質(zhì)量。

第三,借鑒了成熟的判決反饋均衡(DFE)技術(shù)。通過引入DFE,可以在檢測到的數(shù)據(jù)符號基礎(chǔ)上進(jìn)一步消除碼間干擾,從而改善接收信號的質(zhì)量,確保高速數(shù)據(jù)傳輸?shù)目煽啃浴?/p>

最后,沿用了DDR以往的寫平衡(write leveling)和讀平衡(read leveling)機(jī)制。不過,與傳統(tǒng)做法不同的是,將原先在接收端實(shí)現(xiàn)的去加重功能轉(zhuǎn)移到控制器端來完成。這種調(diào)整有助于優(yōu)化整個鏈路的信號處理流程,提高數(shù)據(jù)傳輸效率和準(zhǔn)確性。

3.2.2 接收端測試的新挑戰(zhàn)

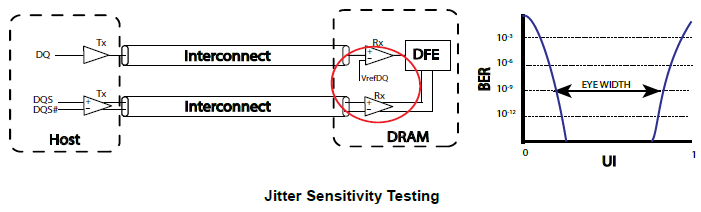

傳統(tǒng)的Serdes接收端測試(以PCIe為例),目的是確定DUT能否在芯片封裝的ball處(或者CEM規(guī)范的金手指處)可靠接收帶有指定受損的信號,達(dá)到要求的誤碼率要求。

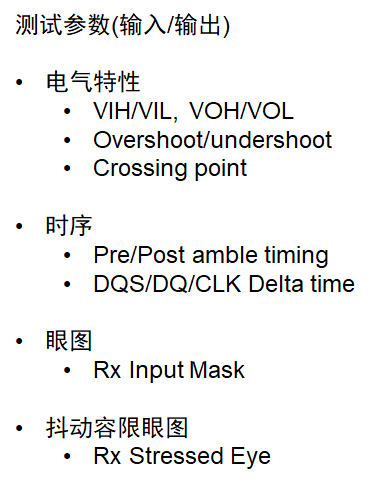

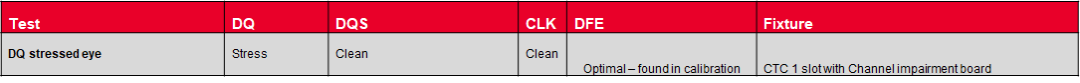

針對DDR的單端并行總線系統(tǒng),非相關(guān)抖動、電平干擾、ISI、串?dāng)_、反射,對于系統(tǒng)的可靠運(yùn)行至關(guān)重要。DDR5的接收端測試,不僅包括了壓力眼測試,也就是在給定的壓力眼信號下,達(dá)到特定的誤碼率要求,還包括了幅度電壓方面和水平抖動方面的靈敏度測試。

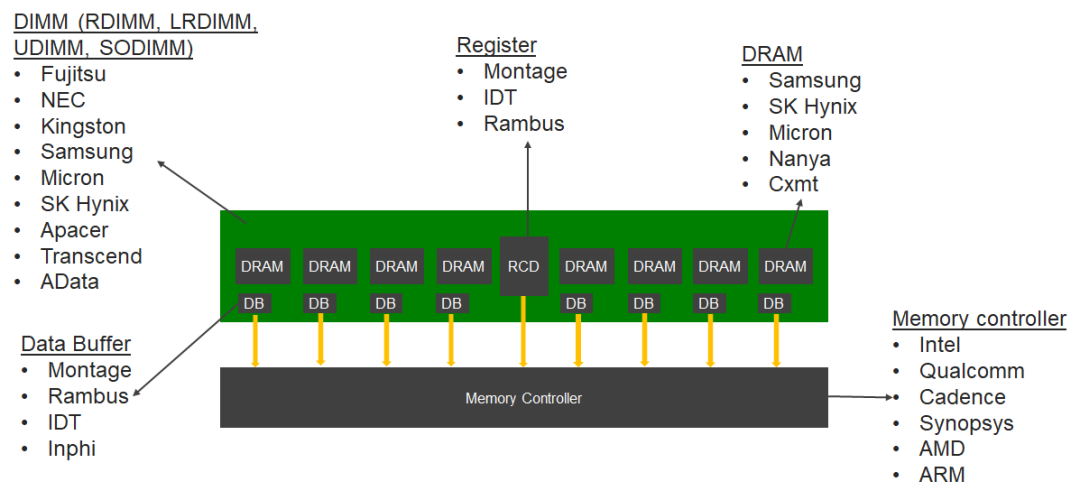

而被測DUT,可以是控制器、DRAM、緩沖器/寄存器、DIMM 等。

3.2.3 接收端測試的新方法

規(guī)范定義了接收端測試?yán)锏乃袦y試點(diǎn)要求,以及波形在均衡器之后的指標(biāo)要求。測試前,需要按照規(guī)范的要求進(jìn)行校準(zhǔn)。

在校準(zhǔn)之前,考慮到DDR總線的獨(dú)特性質(zhì),終端電阻(On-Die Termination, ODT)用于優(yōu)化從發(fā)送端到接收端的信號質(zhì)量。由于ODT允許設(shè)置不同的阻抗值,在接收端測試過程中,建議將ODT設(shè)置為48歐姆進(jìn)行校準(zhǔn),以盡可能減少與標(biāo)準(zhǔn)測試設(shè)備之間的阻抗不匹配。這種設(shè)置有助于確保測量結(jié)果的準(zhǔn)確性和可靠性。

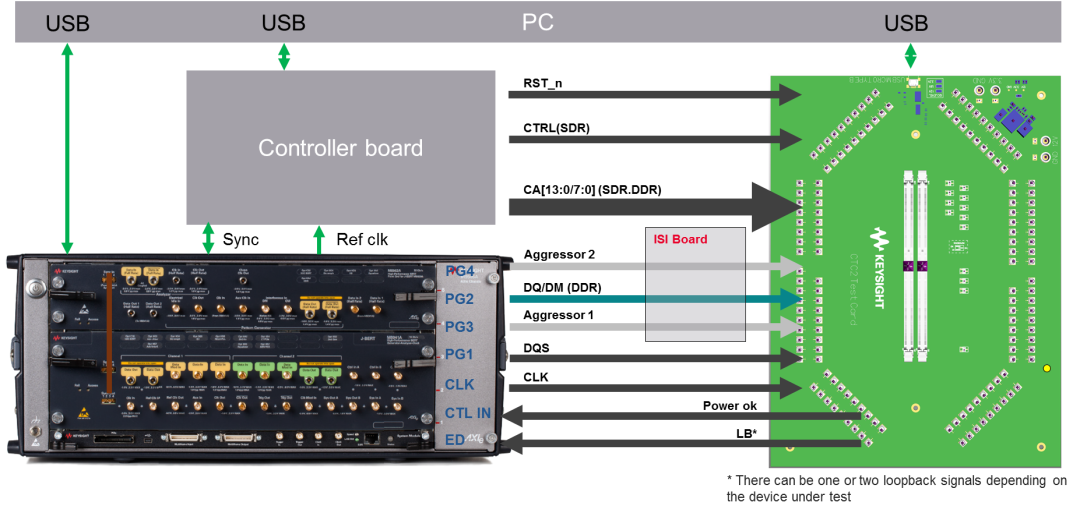

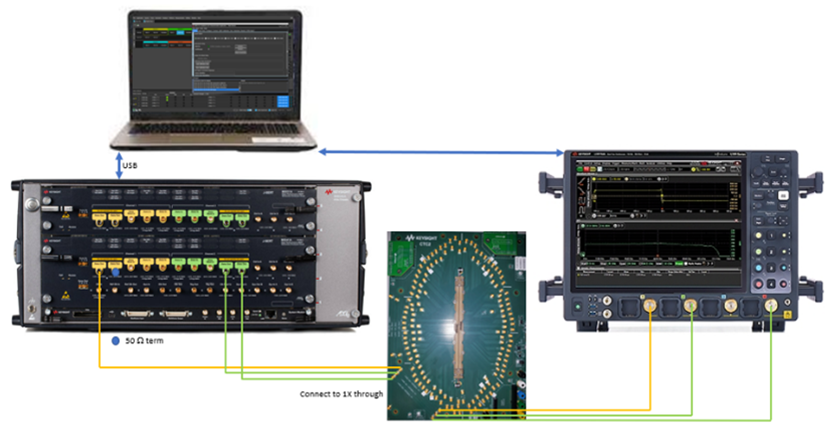

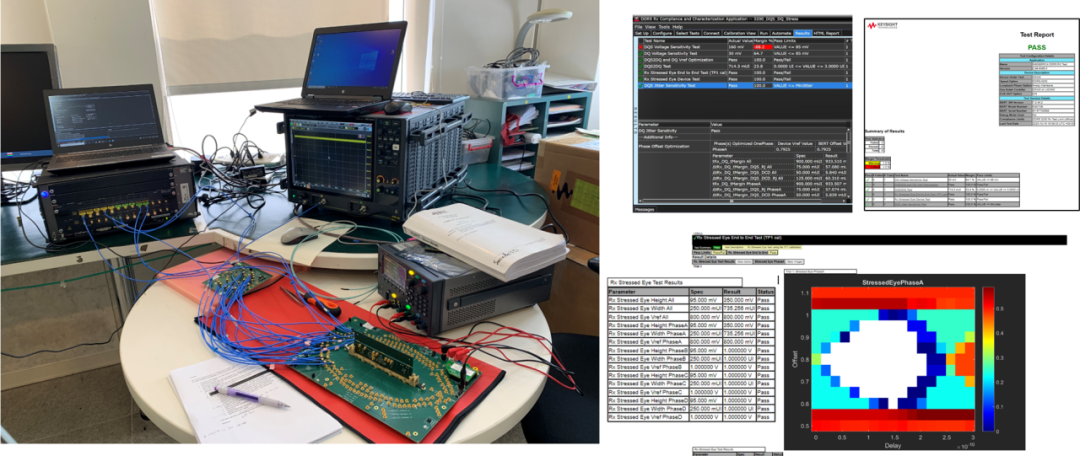

是德科技提供以M8000系列誤碼儀為基礎(chǔ)的DDR5接收端測試方案,支持控制器、DRAM、緩沖器/寄存器、DIMM的測試。

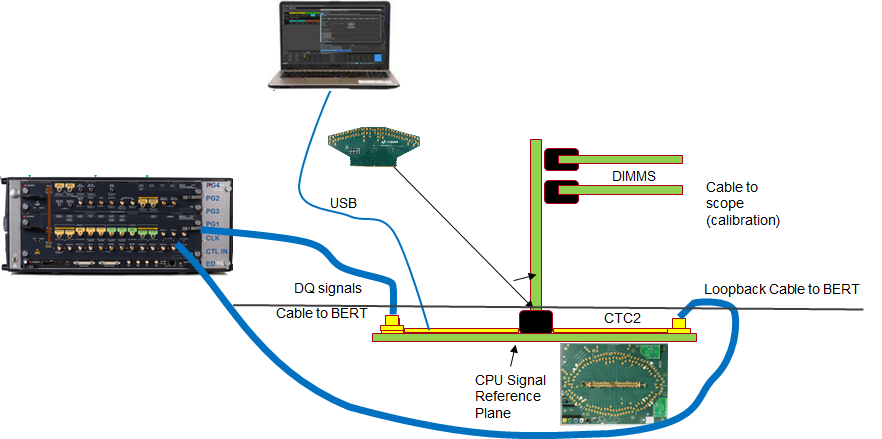

3.2.4 接收端測試的校準(zhǔn)

下圖是DDR在系統(tǒng)產(chǎn)品中實(shí)際應(yīng)用的拓?fù)浣Y(jié)構(gòu)。依次從DDR控制器,經(jīng)過PCB路徑,來到DIMM上的DRAM顆粒。

做校準(zhǔn)的時候,也是參考上圖的拓?fù)鋪硗瓿烧麄€路徑的模擬。針對DIMM或者顆粒而言,信號由BERT發(fā)出,經(jīng)過CTC2 Board和replicate card,最終由示波器接收,組成完整的端到端鏈路。

這里要特別說明的是,針對不同的產(chǎn)品測試,有對應(yīng)的夾具來進(jìn)行配合。主要的夾具有如下幾種。分別是下圖中的C2C test card,System Motherboard Test Fixture,Device Validation Fixture。

其中,CTC2 test card提供DIMM插座,同時將DIMM上所有信號包括CA/CMD、DQS,DQ通過SMP連接器的形式引出。用于DIMM、RCD測試夾具、Data Buffer測試夾具、DRAM測試夾具等的校準(zhǔn)和測試。

CTC2 test card

System Motherboard Test Fixture也同樣把CA/CMD、DQS,DQ的信號通過SMP的方式引出,用于控制器的發(fā)送端測試,以及控制器的接收端測試校準(zhǔn)和測試,同時還支持系統(tǒng)主板的通道特性驗(yàn)證。

System Motherboard Test Fixture

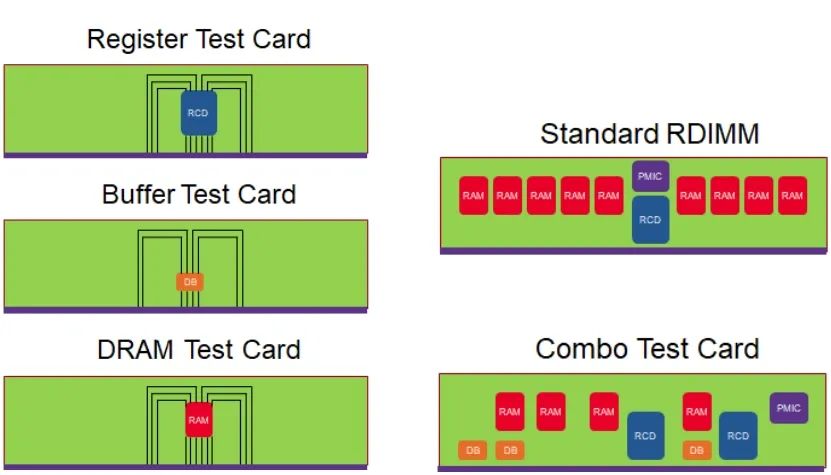

Device Validation Fixture包括了RCD的測試夾具,Data Buffer的測試夾具,DRAM的測試夾具,以及Combo測試夾具等。主要用于單個器件產(chǎn)品的校準(zhǔn)與測試,以及多器件的校準(zhǔn)與測試。測試時插在CTC2的test card上。

Device Validation Fixture

下圖展示的是基于CTC2 test card進(jìn)行的校準(zhǔn)操作。連接方式如圖所示。

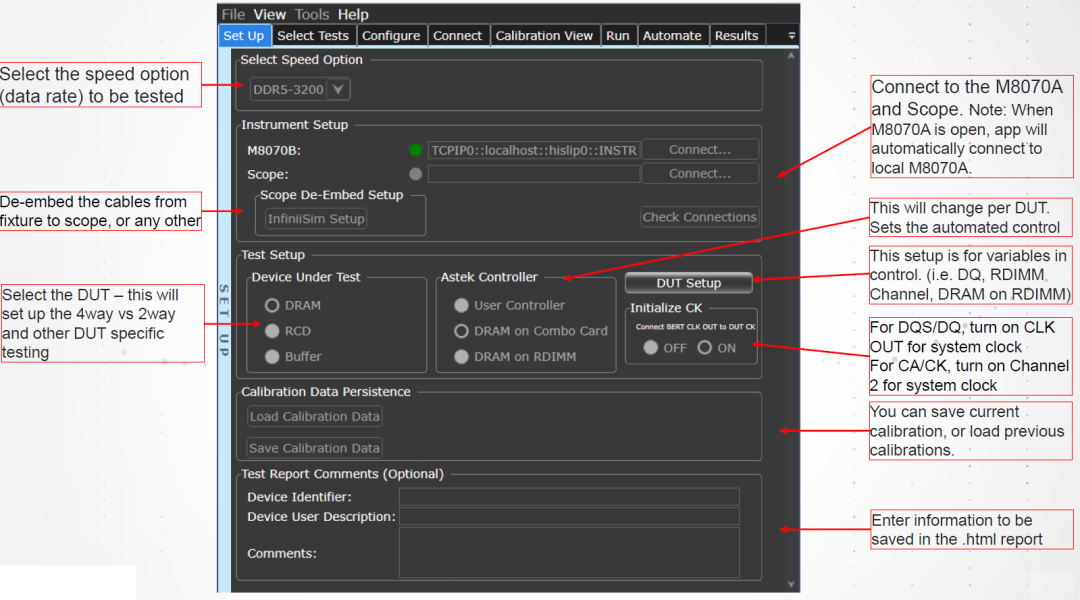

使用M80885RCA自動化軟件,根據(jù)向?qū)В瓿蓽y試環(huán)境參數(shù)的setup,并對DUT進(jìn)行初始化。

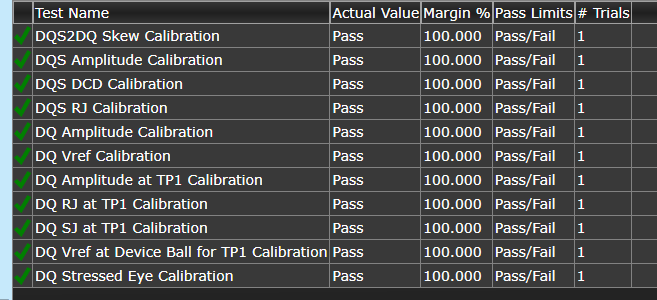

一步一步,實(shí)現(xiàn)DQS&DQ和CK&CA的各參數(shù)自動化校準(zhǔn)。完成自動化校準(zhǔn)后,可以查看每個校準(zhǔn)項(xiàng)目的測試結(jié)果,如下圖所示。

3.2.5 接收端測試

接收端測試包括兩大部分測試內(nèi)容,Sensitivity測試和Stressed Eye測試。其中Sensitivity測試又包含Voltage Sensitivity和Jitter Sensitivity。

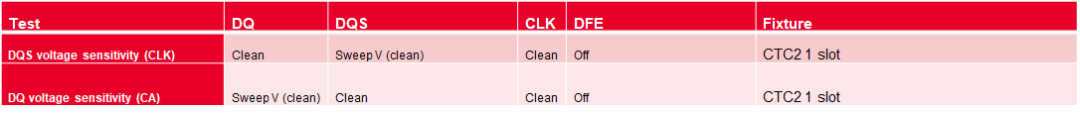

DQS和DQ的Voltage Sensitivity測試中,測試DQS的時候保持DQ的信號不變,測試DQ的時候保持DQS的信號不變。不斷調(diào)整另外一個參數(shù)的變量,遍歷整個參數(shù)的范圍后,統(tǒng)計(jì)誤碼率。

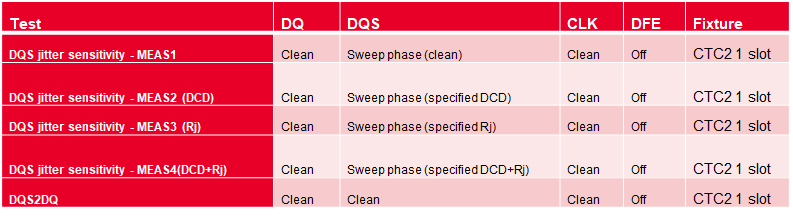

DQS的Jitter Sensitivity測試中,首先輸出clean的clk和dq。在此基礎(chǔ)上,遍歷DQS和DQ的相位,計(jì)算出本底jitter的Sensitivity測試。然后依次改變DCD和Rj以及DCD和Rj的組合,遍歷DQS和DQ的相位,完成各種場景下的jitter Sensitivity測試。

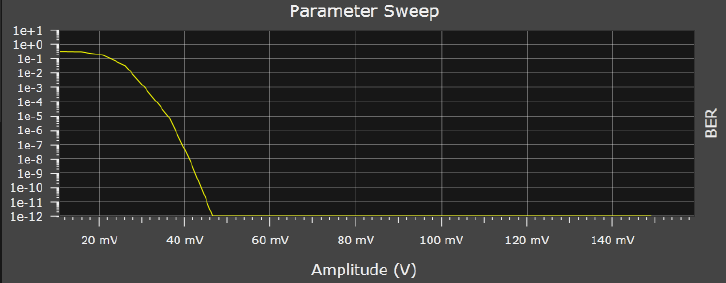

Stressed Eye測試中,使用校準(zhǔn)過程中的壓力信號(如下圖),來進(jìn)行環(huán)回誤碼率測試。

測試完成后,M80885一致性軟件會給出上圖右側(cè)的測試結(jié)果與測試報(bào)告。

四、總結(jié)

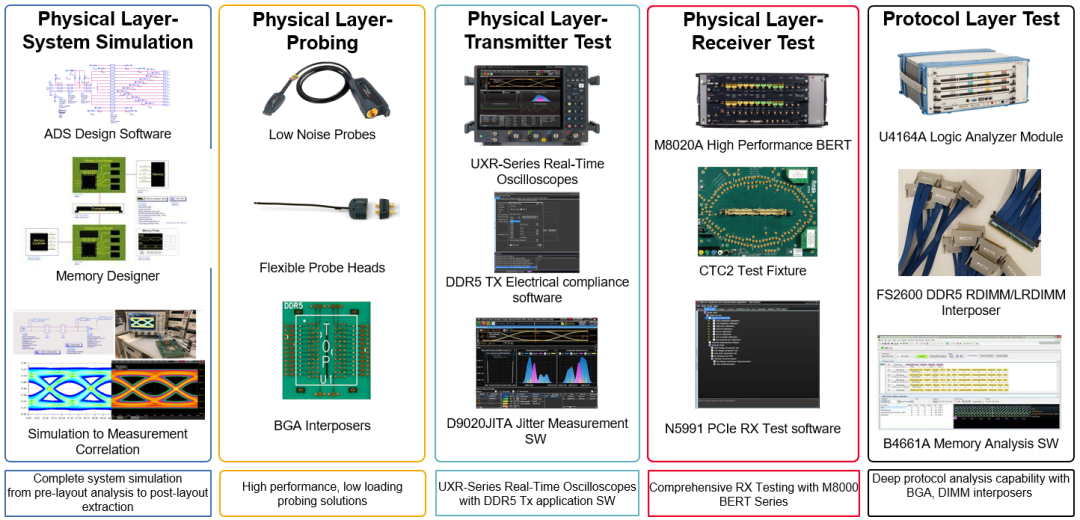

是德科技可以給大家?guī)硗暾亩说蕉私鉀Q方案。包括設(shè)計(jì)前期的仿真,涵蓋了memory designer的建模和ADS的前后仿真。發(fā)送端測試中,我們提供業(yè)內(nèi)旗艦級性能指標(biāo)的UXR實(shí)時示波器和高性能的RC模型探頭,有效降低測試負(fù)載。接收端測試中,我們提供all-in-box的M8000系列誤碼儀,支持控制器、DRAM、Data Buffer、RCD、DIMM的接收端校準(zhǔn)與測試。協(xié)議分析儀方面,U4164A系列,支持完整的DDR、LPDDR的協(xié)議解碼測試。

-

存儲器

+關(guān)注

關(guān)注

38文章

7636瀏覽量

166445 -

DDR

+關(guān)注

關(guān)注

11文章

731瀏覽量

66406 -

是德科技

+關(guān)注

關(guān)注

21文章

984瀏覽量

83237

發(fā)布評論請先 登錄

DDR5內(nèi)存接口芯片組如何利用DDR5 for DIMM的優(yōu)勢?

Introspect DDR5/LPDDR5總線協(xié)議分析儀

DDR3/4都還沒玩夠,DDR5已經(jīng)來啦

DDR5這么快,為啥還能那么穩(wěn)?

三種主流內(nèi)存技術(shù)(DDR、GDDR、LPDDR)的速度對比與應(yīng)用和DDR5芯片的設(shè)計(jì)

Cadence公司發(fā)布了關(guān)于即將發(fā)布的DDR5市場版本以及技術(shù)的進(jìn)展

DDR5內(nèi)存將在明年實(shí)現(xiàn)量產(chǎn)

專門為內(nèi)存顆粒測試設(shè)計(jì)的DDR4/DDR5 Interposr測試板

ddr5的主板可以用ddr4內(nèi)存嗎 幾代CPU才能上DDR5

XMP DDR5 8000內(nèi)存性能測試詳解

DDR5測試技術(shù)更新漫談

DDR5測試技術(shù)更新漫談

DDR5測試技術(shù)更新漫談

評論