VeriSim先進數字仿真器

產品簡介

VeriSim是一款先進的邏輯仿真器,提供全面的數字設計驗證解決方案,特別適用于大型SoC設計。它配備高性能的仿真引擎和約束求解器,旨在提高編譯時效率,并確保設計的正確性和穩定性。

VeriSim可適配眾多主流硬件描述語言,包括Verilog、VHDL、SystemVerilog、SystemC等,以及它們的組合,確保用戶能夠選用其熟悉的語言進行設計和驗證。

VeriSim支持兩種主要的數字邏輯驗證:一是行為級、RTL級和帶SDF后仿的門級數字電路門級Verilog和VHDL仿真;二是高階的系統級SystemVerilog加SystemC混合仿真,通過無縫集成通用驗證方法(UVM),VeriSim為用戶提供快速驗證測試臺的設置,使驗證過程更加高效和可控,其Assertion功能還可確保用戶在設計初期發現并修正潛在的錯誤,從而顯著縮短驗證周期,加快產品上市進程。

VeriSim提供全面的功能性和代碼覆蓋率測試,可生成多種格式的仿真數據。此外,VeriSim輸入文件可通過加密算法進行保護,確保客戶IP得到充分的安全保護。

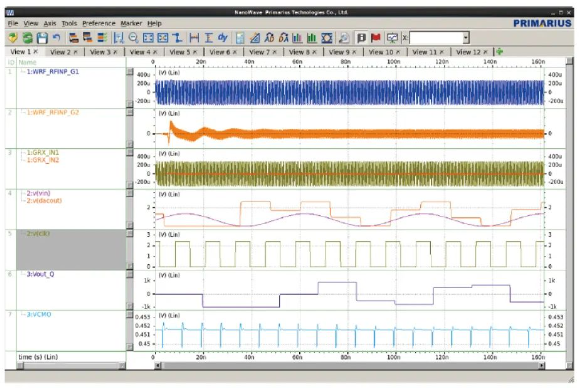

通過集成NanoSpice系列的各種晶體管級電路仿真器,VeriSim可提供完整的混合信號驗證解決方案,支持全面設計驗證,確保數字電路與模擬電路協同運行,進而提高系統可靠性。

產品優勢

·高性能&大容量

編譯、仿真和約束求解器引擎創新優化

·先進的仿真技術

X態傳播和競爭條件消除技術

·兼容性和可用性

易于使用并支持從現有工具快速遷移

·兼容不同CPU架構

支持X86和ARM

·一站式混合信號驗證解決方案

與NanoSpice系列晶體管級仿真器集成的數模混和信號仿真

技術規格

·語言支持

-Verilog:1995/2001/2005

-SystemVerilog(SV):2005/2009/2012/2017

-VHDL:ieee87/ieee93/ieee08

-SystemC

·仿真支持

-Verilog/SystemVerilog設計

-VHDL設計

-Verilog/SystemVerilog與SystemC設計

-VHDL和Verilog模塊互相調用的混合設計

·支持約束求解器

·支持功能覆蓋率和代碼覆蓋率測試

·支持波形轉儲

·支持UVM-1.1b,UVM-1.1d和UVM-1.2驗證方法學

·支持帶標準延遲格式(SDF)后仿信息的門級仿真

·支持IEEE1735加密

產品應用

·系統驗證testbench設置

·SystemVerilog和SystemC混合語言testbench

·集成NanoSpice實現數模混和SoC全芯片驗證

·行為級、RTL級和帶SDF后仿的門級數字電路

-

仿真器

+關注

關注

14文章

1034瀏覽量

85082 -

SoC設計

+關注

關注

1文章

151瀏覽量

19121 -

晶體管

+關注

關注

77文章

9992瀏覽量

140896 -

概倫電子

+關注

關注

1文章

112瀏覽量

8990

原文標題:先進數字仿真器 - VeriSim

文章出處:【微信號:khai-long_tech,微信公眾號:概倫電子Primarius】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

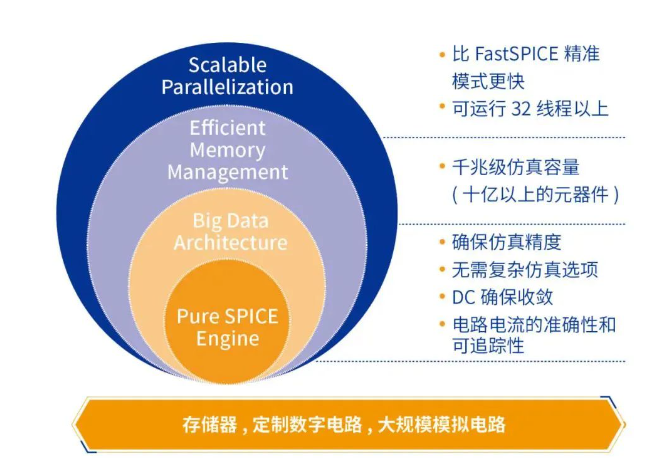

概倫電子千兆級電路仿真器NanoSpiceGiga?介紹

概倫電子先進的建模軟件平臺MeQLab介紹

DAC 2011:概倫電子電路仿真與驗證方案

并行SPICE電路仿真器NanoSpice,用于任意晶體管級電路仿真

概倫電子NanoSpice仿真器助力SK海力士CIS芯片驗證

概倫電子仿真器NanoSpice滿足大容量和高性能的高端電路仿真需求

概倫電子NanoSpice系列仿真器榮登工信部“2022年工業軟件優秀產品”名單

概倫電子與阿里云深化合作加速推動EDA上云

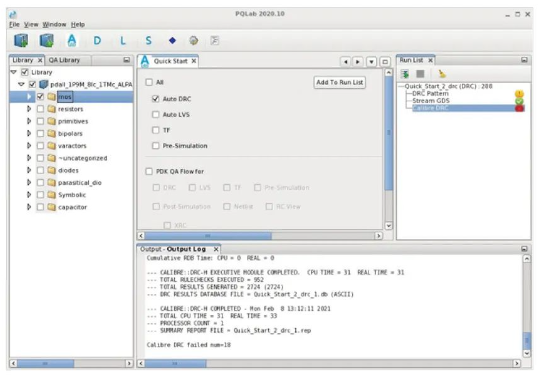

概倫電子先進PDK驗證平臺PQLab介紹

概倫電子電路類型驅動SPICE仿真器NanoSpice X介紹

概倫電子先進數字仿真器VeriSim介紹

概倫電子先進數字仿真器VeriSim介紹

評論