0 引言

在后摩爾定律的時代背景下,通過傳統的縮小晶體管尺寸的方式來提高集成度變得非常困難。現在的電子系統正朝著小型化、多樣化、智能化的方向發展,并最終形成具有感知、通信、處理、傳輸等功能的微系統。微系統的核心技術是集成,正在由平面集成向三維集成、由芯片級向集成度和復雜度更高的系統集成發展。近年來,半導體工藝技術快速發展,不僅體現在射頻、模擬、混合信號等傳統的半導體工藝,還體現在系統的異質集成等非傳統的半導體工藝。

1 異質集成

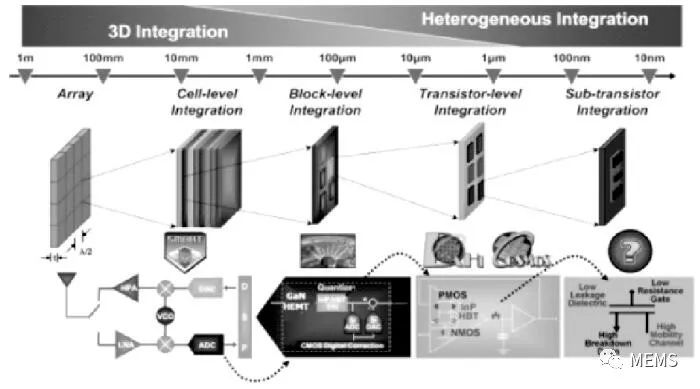

美國國防部高級研究計劃局(DARPA)在1990年代末率先提出了異質集成的概念,并勾畫出異質集成的發展方向,如圖1所示。異質集成可以集成的器件有:射頻/模擬電子系統中的雙極器件(SiGe和Ⅲ-Ⅴ族 HBT)、低頻模數混合信號系統中的CMOS器件、MEMS/NEMS等機械量檢測器件、光電/電光轉換器件等。

圖1 DARPA提出的三維集成和異質集成計劃

異質集成可以分為混合集成和單片集成。混合集成是將不同襯底材料的芯片通過鍵合實現的集成方式。它的代表技術是三維芯片堆疊,類似于系統級封裝(SiP)的概念。單片集成是將各種不同功能的器件在單芯片上集成,省去了這些芯片的封裝,但工藝制造難度較大。單片異質集成類似于片上系統(SoC)的概念,是工業界和學術界的研究熱點之一。可以預見,單片異質集成技術將有較大的發展空間。

2 單片異質集成

國外在異質集成方面的研究主要為單片異質集成:Si基CMOS微電子器件、Ⅲ-Ⅴ族微電子器件、Ⅲ-Ⅴ族光電子器件和MEMS器件等。Si基CMOS器件與Ⅲ-Ⅴ族器件的結合可以充分發揮各自的技術優勢,實現單一器件無法達到的性能。單片異質集成通常采用類似post-CMOS工藝的方法,首先制作Si基CMOS器件,然后進行Ⅲ-Ⅴ族器件的制作以及二者之間的互聯。這種方法的優點是Si基CMOS器件與Ⅲ-Ⅴ族器件的制作工藝相對獨立,制作Ⅲ-Ⅴ族器件時不會對已經完成的CMOS器件產生影響,采用Si材料作為襯底可以有效降低成本。

2.1 Si基CMOS和Ⅲ-Ⅴ族微電子器件

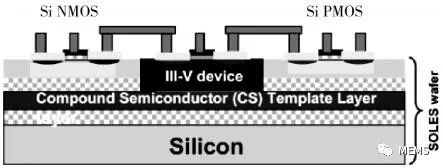

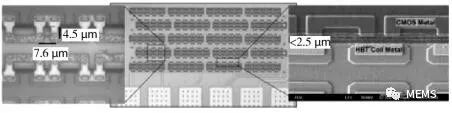

美國雷神公司在Ⅲ-Ⅴ族與Si基CMOS器件的異質集成方面進行了較多的 研究。該公司在2010年實現了在Si襯底上集成InP HBT和Si基CMOS器件,如圖2所示。這種單片異質集成方法基于美國麻省理工學院提出的SOLES工藝。SOLES工藝包括一個由Ⅲ-Ⅴ族化合物構成的模板層(template layer),在這個模板層上直接外延生長高質量的Ⅲ-Ⅴ族器件。SOLES工藝的模板層兼容標準的Si基CMOS工藝,但后續Ⅲ-Ⅴ族器件的制作并不與標準CMOS工藝兼容,需要額外的Ⅲ-Ⅴ族工藝配合完成。圖3給出了異質集成的CMOS-InP HBT器件的掃描電子SEM照片,可以看到兩種器件的間隔只有2.5μm,顯示出較高的集成度。雷神公司采用這種工藝實現了一種單位增益帶寬積高達20GHz的差分放大器和一種13位500MHz帶寬的高速高精度DAC,與傳統的InP襯底下同質外延生長和加工的HBT管相比,電學性能相當。

圖2 雷神公司基于SOLES工藝的Si基CMOS器件與Ⅲ-Ⅴ族器件的異質集成

圖3 雷神公司異質集成的CMOS-InP HBT器件的SEM照片

2011年,雷神公司采用相同的方法,實現了GaN HEMT和Si基CMOS器件的異質集成,但仍然存在不足:1)只能在小尺寸(100mm)的晶圓上實現;2)需要兩種制造工藝,Si基CMOS器件的制造在Si代工廠完成,而GaN HEMT以及后續的互聯工藝需要在Ⅲ-Ⅴ族代工廠完成。之后,研究人員采用一些方法解決了上述問題。比如,在200mm的Si襯底上采用分子束外延方法(MBE)外延生長GaN。相比于標準金屬有機化學氣相外延(MOCVD)生長技術,MBE外延技術的優點是所需的溫度較低,由高溫導致Si基CMOS器件性能退化的影響變小,還可提高GaN管的射頻性能。另外,傳統的GaN器件的歐姆接觸采用金屬Au,與Si基CMOS工藝不兼容。還有些研究人員則采用Ti/Al/W的歐姆接觸,實現了在Si基代工廠完成GaN器件的代工。

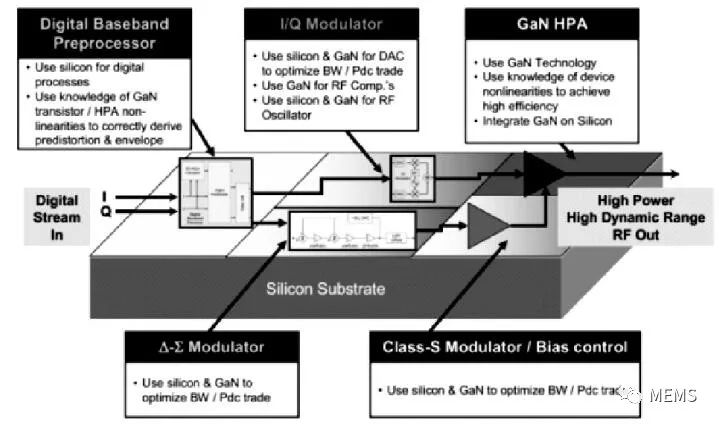

在實現Si基CMOS器件與GaN HEMT器件的單片異質集成后,雷神公司進一步實現了單片發射機芯片,在一個芯片上集成了數字基帶處理器、高線性度功率放大器、高輸出功率DAC、射頻發射機等,如圖4所示。該發射機芯片證明了單片異質集成技術在射頻、混合信號、數字電路等領域具有巨大的應用潛力。

圖4 雷神公司采用單片異質集成技術實現的線性化發射機

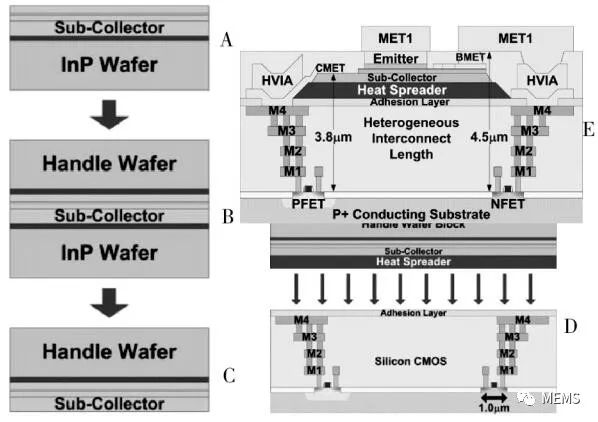

美國HRL公司也對單片異質集成進行了大量的研究。與雷神公司直接在模板層上異質集成外延Ⅲ-Ⅴ族材料的方法不同,HRL公司通過兩種器件襯底材料的直接鍵合實現芯片晶圓級的異質集成。工藝步驟如圖5所示,先在InP晶圓上外延生長InP DHBT外延層,隨后刻蝕掉InP襯底,將Si基與InP進行晶圓級鍵合,然后刻蝕制作出InP器件并與Si基CMOS器件互聯,最終實現250nm InP DHBT工藝與130nm RF CMOS工藝的單片異質集成。單片異質集成后的工藝可以稱為InP BiCMOS工藝。2014年,HRL公司又分別將40nm GaN HEMT工藝和250nm InP HBT工藝與65nm CMOS工藝進行了單片異質集成。

圖5 HRL公司的InP DHBT和CMOS工藝異質集成

2.2 Si基CMOS微電子器件和Ⅲ-Ⅴ族光電子器件、MEMS器件

光電子器件在超高速信號傳輸上的獨特優勢使得光電集成技術具有較好的應用前景。Si是間接帶隙材料,發光效率較低,不適合用作高效的發光器件。而Ⅲ-Ⅴ族化合物屬于直接帶隙材料,易于發射和吸收光。因此,將Ⅲ-Ⅴ族材料制造的光源和Si材料制造的微電子器件集成在一起,就可以實現Si基單片光電集成電路。

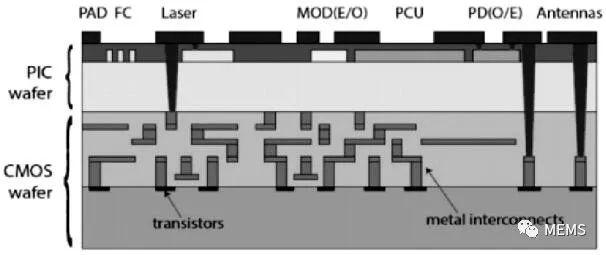

與成熟的Si基電子器件相比,Ⅲ-Ⅴ族光電集成電路(Photonic Integrated Circuits,PIC)仍然處于發展階段。2016年,荷蘭埃因霍溫理工大學的研究人員在60GHz毫米波頻率下,采用OTTD(Optical True Time Delay)的波束控制技術實現了相控陣列毫米波收發系統,并采用片上集成天線(Antenna-on-Chip,AoC)技術,將天線與電子器件互聯的損耗最小化。采用光傳輸的波束控制技術具有超寬頻帶和低損耗等優點。PIC電路主要包括InP材料實現的激光器和光電二極管。

圖6給出了單芯片上集成CMOS器件、光電集成電路以及片上天線等的器件結構圖。首先,獨立制作CMOS和PIC晶圓,并將PIC晶圓粘合在CMOS晶圓之上,然后將天線部分制作在PIC晶圓之上,最后加入CMOS器件、PIC電路和天線三者之間的互連線。圖6中,FC為光纖耦合器,MOD為電光調制器,PCU為光子控制單元,PD為光電二極管。

圖6 單芯片集成CMOS器件、光電集成電路、片上天線

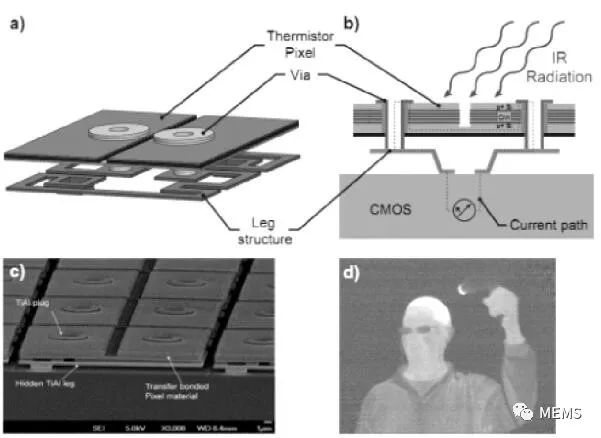

MEMS器件近年來也有了長足的發展,其主要發展方向是兼容Si基CMOS工藝。2016年,瑞典皇家理工學院微納系統實驗室的研究人員實現了微測熱輻射計陣列(由Si/SiGe量子阱熱敏電阻單元構成)和標準CMOS工藝實現的讀出電路的單片異質集成,如圖7所示。圖7給出了單個像素的微測熱輻射計的原理圖和微測熱輻射計陣列的SEM照片。

圖7 輻射熱測量器陣列和CMOS讀出電路的異質集成

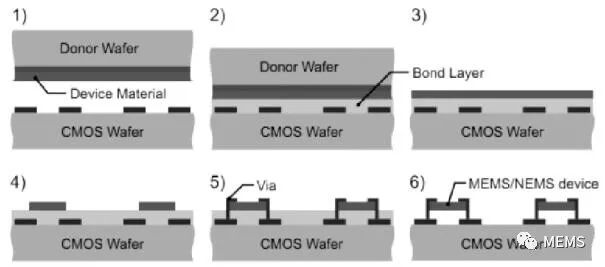

在工藝制造中,Si/SiGe量子阱熱敏電阻制作工藝的溫度超過了CMOS電子器件制作工藝的溫度。因此,Si/SiGe量子阱熱敏電阻器件首先被制作于SOI晶圓上,隨后被轉移到CMOS晶圓上,然后將SOI晶圓的襯底去除,刻蝕出器件,并制作通孔,實現CMOS與MEMS器件的互連,最終完成單片異質集成工藝。工藝步驟如圖8所示。

圖8 CMOS器件和MEMS器件單片異質集成工藝步驟

2.3 國內研究進展

國內已有不少研究機構和公司開展異質集成技術方面的研究,但大多數仍處于起步階段。國內研究以異質外延為主,即在Si襯底上直接外延生長Ⅲ-Ⅴ族化合物。但Ⅲ-Ⅴ族化合物與Si之間存在較大的晶格失配和熱失配,很難得到高質量的外延層,器件的可靠性較低。如何解決異質材料之間的晶格失配也是近年來的研究熱點之一。比如,有學者提出低溫晶片鍵合的方法,可廣泛應用于光電子器件、微機械智能系統和三維器件等。

2015年,南京電子器件研究所的吳立樞等人基于外延層剝離轉移、異類器件互聯等技術,實現了GaAs pHEMT與Si基CMOS器件異質集成的單片電路。最終實現的單片數字控制開關電路與傳統的GaAs pHEMT單片電路相比,芯片面積減小了15%。該異質集成電路如圖9所示。

圖9 異質集成電路FIB截面圖

3 面臨的挑戰

國內外異質集成技術雖然有了長足的發展,但由于技術較為復雜,仍然需要克服很多問題才能實現大規模的應用。本文列出了幾個關鍵的問題。

(1)技術限制。異質集成的工藝還不完善,尤其是單片異質集成,雖然目前已能實現,但尚未進行大規模量產。異質集成涉及的工藝步驟多且復雜,對工藝精度要求較高,同時對能夠異質集成的器件也有一定的約束。量產后的產品良率還有待進一步驗證。

(2)三維互連技術。異質器件的集成需要采用三維互聯中的硅通孔(TSV)技術。基于TSV工藝的三維集成可以實現短且密的層間互聯,有效縮短了互連線長度。但是TSV工藝較復雜,是易受到制造缺陷影響的敏感工藝。另外,一個芯片上的TSV數目較多,一個TSV的損壞會導致整個芯片損壞。因此,需要研究TSV工藝的故障機理,并提出降低故障概率的方法。

(3)異質集成芯片的測試技術。測試技術是異質集成面臨的主要挑戰之一。異質集成芯片的集成度遠高于二維芯片,但芯片的封裝引腳數量基本與二維芯片相同,因此,分配給每個電路模塊的測試引腳數相對變少,芯片的可控制性、可觀察性均有所降低,測試難度增大。

(4)散熱和可靠性問題。Ⅲ-Ⅴ族化合物的一個重要應用環境是高輸出功率放大器。異質集成技術提高了芯片的集成度,在十分有限的芯片面積下集成多種器件后,散熱問題就顯得尤為重要。在可靠性方面,需要對材料的性能、退化和失效機理作進一步研究,以建立有效的、多種物理、多尺度模型來準確預測失效的發生,提高芯片的可靠性。

(5)軟件和工藝PDK文件支持。軟件在集成電路制作中的作用越來越大。在器件級、芯片晶圓級和子系統級的設計、仿真、加工和驗證方面,需要一套完整的、EDA軟件支持的解決方案。同時,新器件的研發需要代工廠商配套開發相應的PDK文件。

4 總結

現代微系統技術正從二維集成到三維集成、從微電子/光電集成到異質集成、從結構/電氣一體化到多功能一體化集成等方向發展。異質集成技術作為超越摩爾定律發展的重要手段之一,已從多種不同材料芯片的二維/三維集成發展到同一襯底上集成多種不同材料、不同結構的器件,并實現了不同工藝器件的一體化互連。國外在單片異質集成方面的研究多集中在Si基CMOS器件與Ⅲ-Ⅴ族器件的異質集成,可以利用器件各自的優勢在單芯片上集成射頻、混合信號系統中的CMOS器件、MEMS/NEMS器件、光電/電光轉換器件等,實現片上子系統,但仍存在量產的良率較低、芯片散熱能力有限、可靠性較低等問題。

-

芯片

+關注

關注

460文章

52522瀏覽量

441242 -

mems

+關注

關注

129文章

4155瀏覽量

194256 -

微電子

+關注

關注

18文章

401瀏覽量

41911

原文標題:單片異質集成技術研究現狀與進展

文章出處:【微信號:MEMSensor,微信公眾號:MEMS】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

RISC-V 發展現狀及未來發展重點

工業電機行業現狀及未來發展趨勢分析

最新議程出爐! | 2025異質異構集成封裝產業大會(HIPC 2025)

2025年紅外傳感器發展現狀:科技創新與市場擴展的交匯點

先進陶瓷產業發展現狀剖析與發展建議

智能駕駛傳感器發展現狀及發展趨勢

共封裝光學器件的現狀與挑戰

淺談生物傳感技術的定義、發展現狀與未來

FWA產業的發展現狀和演進方向

醫療機器人發展現狀與趨勢

工控機廠家發展現狀及未來趨勢

國產光電耦合器:2024年的發展現狀與未來前景

單片異質集成的發展現狀

單片異質集成的發展現狀

評論