概述

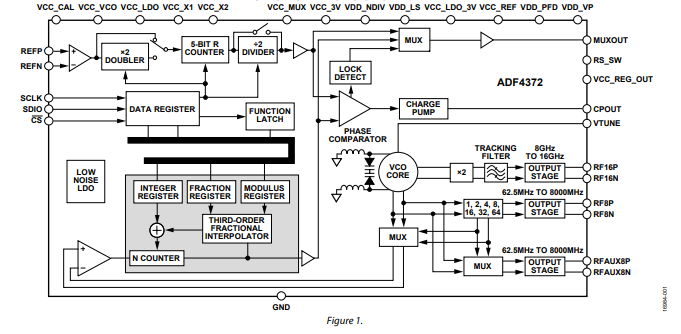

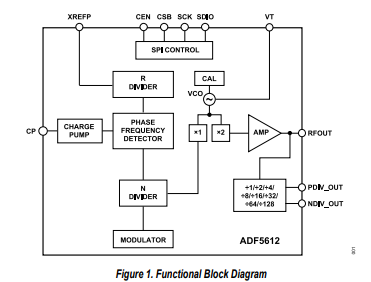

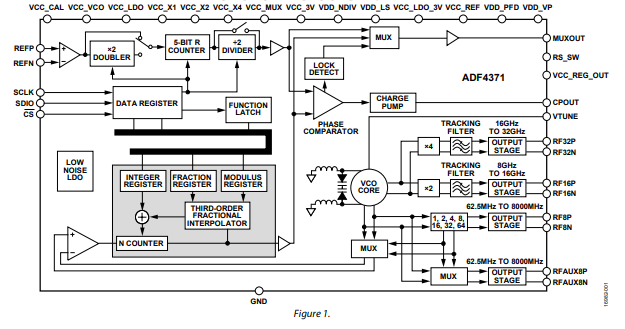

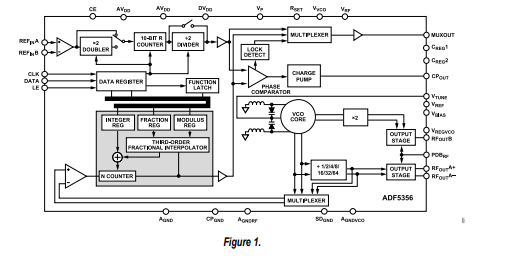

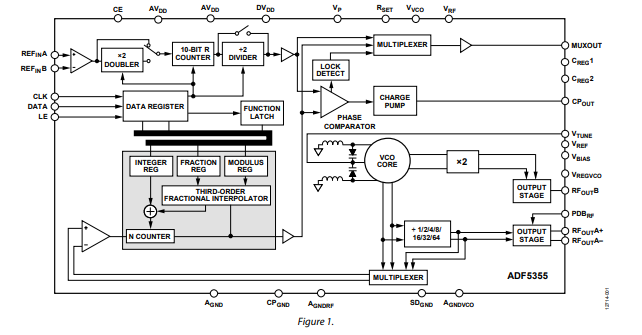

ADF4372 結合外部環路濾波器和外部基準頻率使用時,可實現小數 N 分頻或整數 N 分頻鎖相環 (PLL) 頻率合成器。寬帶微波壓控振蕩器 (VCO) 設計允許產生 62.5 MHz 至 16 GHz 的頻率。

ADF4372 具有一個集成 VCO,其基本輸出頻率范圍為 4000 MHz 至 8000 MHz。此外,VCO 頻率連接至 1、2、4、8、16、32 或 64 分頻電路,因此用戶可以在 RF8x 上生成低至 62.5 MHz 的射頻 (RF) 輸出頻率。RF16x 上的倍頻器可生成 8 GHz 至 16 GHz 的頻率。RFAUX8x 復制 RF8x 的頻率范圍,或允許直接訪問 VCO 輸出。為了抑制不需要的倍頻產物,在倍頻器和 RF16x 的輸出級之間使用了一個諧波濾波器。

片內寄存器均通過三線式接口進行控制。ADF4372 由 3.15 V 至 3.45 V 的模擬和數字電源供電,對于 VCO 電源為 5 V。ADF4372 還包含硬件和軟件關斷模式。

數據表:*附件:ADF4372帶集成VCO的微波寬帶頻率合成器技術手冊.pdf

應用

特性

- RF 輸出頻率范圍:62.5 MHz 至 16,000 MHz

- 小數 N 頻率合成器和整數 N 頻率合成器

- 高分辨率 39 位小數模數

- 典型雜散 fPFD~:?90 dBc~

- 集成 RMS 抖動:38 fs(1 kHz 至 100 MHz)

- 歸一化本底相位噪聲:?234 dBc/Hz

- f

PFD工作頻率達 250 MHz - 基準輸入頻率達 600 MHz

- 可編程的 1、2、4、8、16、32 或 64 分頻輸出

- RF8x 和 RFAUX8x 具有 62.5 MHz 至 8,000 MHz 的輸出

- RF16x 具有 8,000 MHz 至 16,000 MHz 的輸出

- 鎖定時間大約為 3 ms 并進行自動校準

- 鎖定時間 <30 μs 并繞過自動校準(典型值)

- 模擬和數字電源:3.3 V(典型值)

- VCO 電源電壓:3.3 V 和 5 V

- RF 輸出靜音功能

- 7 mm × 7 mm 48 端子 LGA 封裝

框圖

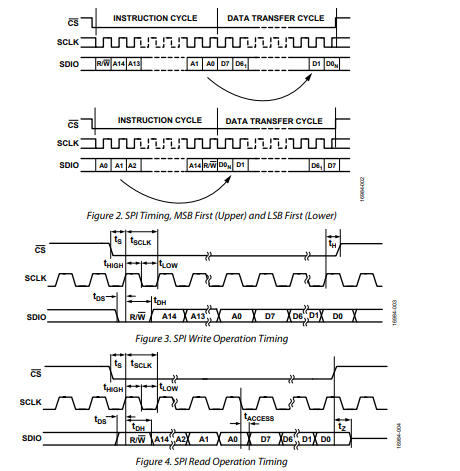

時序圖

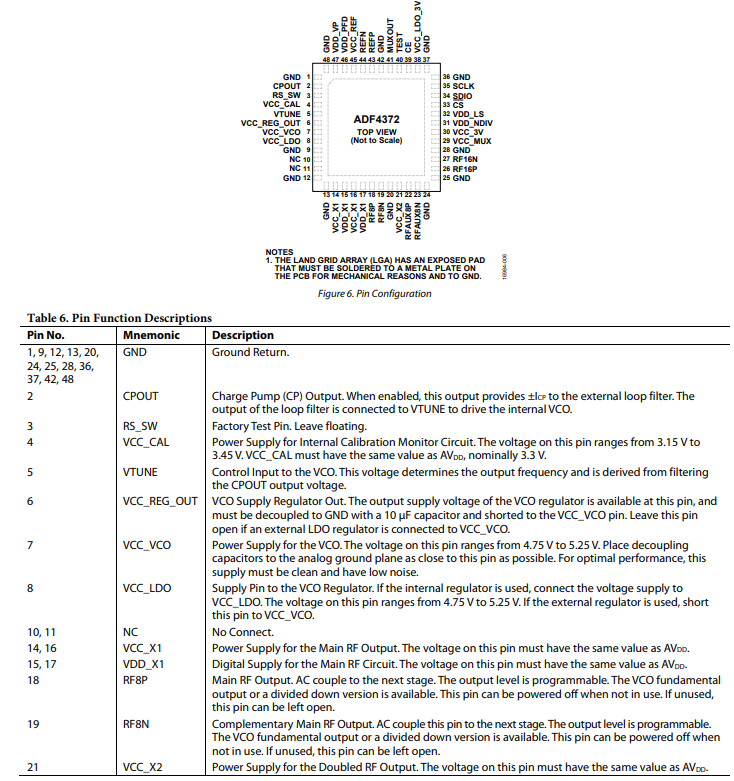

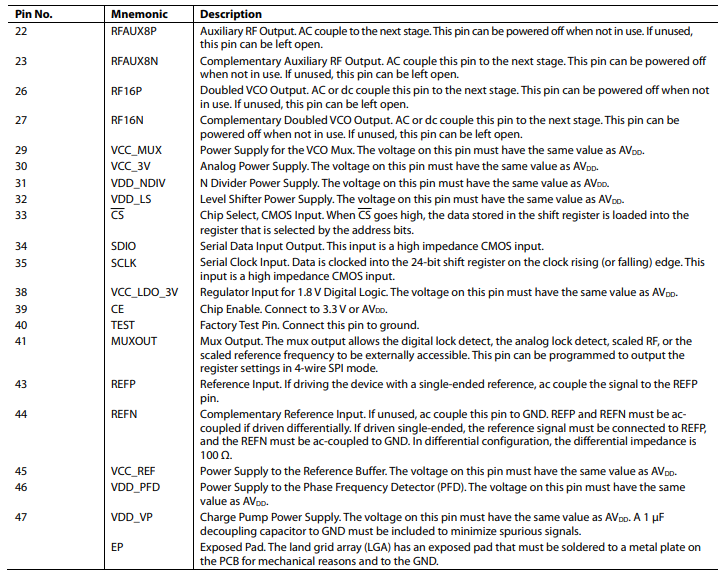

引腳配置描述

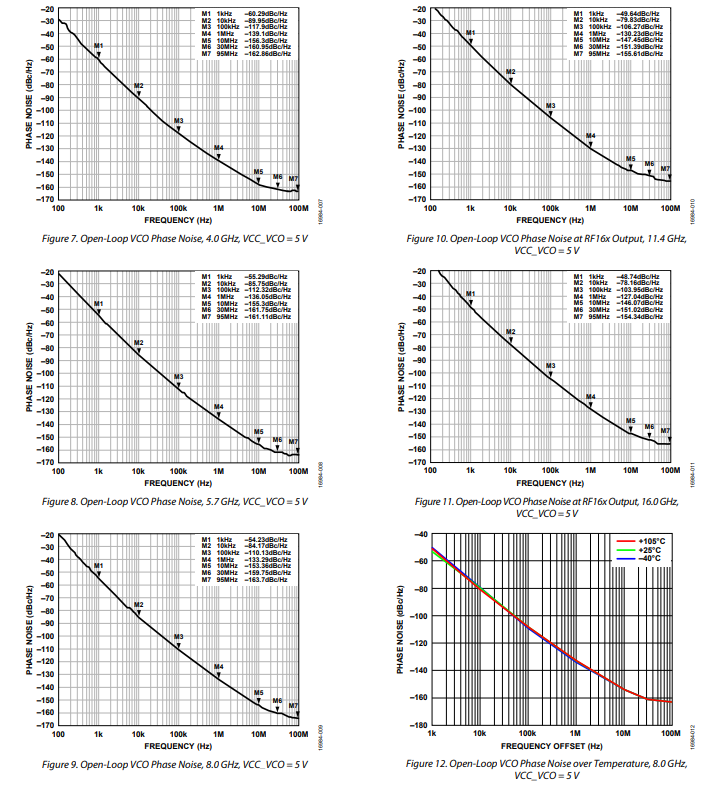

典型性能特征

電路描述

參考輸入

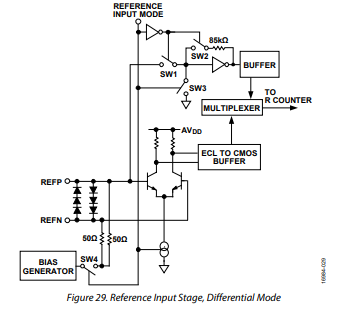

圖29展示了參考輸入級。該參考輸入可接收單端和差分信號。使用參考模式位(地址0x22中的第6位)來選擇信號路徑。若要將差分信號用作參考輸入,需將該位設為高電平。在這種情況下,SW1和SW2閉合,SW3和SW4斷開,電流源驅動差分對晶體管開關。差分信號經緩沖后,以發射極耦合邏輯(ECL)形式提供給CMOS緩沖器。

當單端信號用作參考信號時,將地址0x22中的第6位設為0。此時,SW1和SW2斷開,SW3和SW4閉合,電流源驅動的差分對晶體管開關關閉。

為實現最佳整數模式雜散和相位噪聲性能,對于高達500MHz的所有參考信號,使用單端設置(即使采用差分信號)。對于高于500MHz的參考頻率,使用差分設置。

圖29. 參考輸入級,差分模式

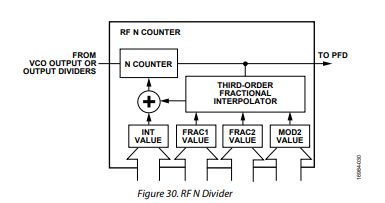

射頻N分頻器

射頻N分頻器在鎖相環(PLL)反饋路徑中實現分頻比。該分頻器的分頻比由INT、FRAC1、FRAC2、MOD1和MOD2這些值決定。

圖30. 射頻N分頻器

INT、FRAC、MOD和R計數器關系

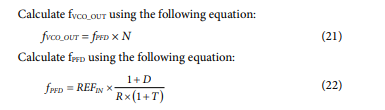

INT、FRAC1、FRAC2、MOD1和MOD2這些值,與R計數器配合,能夠生成間隔為**f_{PD}**分數倍的輸出頻率。更多信息請參見“射頻合成器,實例”部分。

其中:

- REF_{IN} 是參考頻率輸入。

- D 是**REF_{IN}**倍頻位。

- R 是5位二進制可編程參考預分頻器的預設分頻比。

- T 是**REF_{IN}**的2位除法值(0或1)。

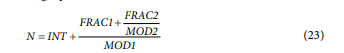

使用以下公式計算所需的反饋計數器N:

其中:

- INT是16位整數模式值。在整數模式下,對于4/5預分頻器,INT = 20至32,767;對于8/9預分頻器,INT = 64至65,535。在分數模式下,對于4/5預分頻器,INT = 23至32,767;對于8/9預分頻器,INT = 75至65,535。

- FRAC1是主模數(0至33,554,431)的分子。

- FRAC2是14位輔助模數(0至16,383)的分子。

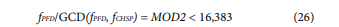

- MOD2是可編程的14位輔助分數模數(2至16,383)。

- MOD1是固定值為25的25位主模數。

- $2^{25}$ = 33,554,432。

這些計算可實現極低的頻率分辨率,且無殘留頻率誤差。要應用公式(23),請執行以下步驟:

- 用VCO_{OUT}除以f_{PFD}計算N。該數值的整數部分構成INT。

- 從完整的N值中減去INT。

- 將余數乘以$2^{25}$。該數值的整數部分構成FRAC1。

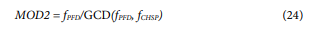

- 根據信道間隔(f_{CHSP}),使用以下公式計算MOD2:

其中:

GCD(f_{PFD}, f_{CHSP})是鑒頻鑒相器(PFD)頻率和信道間隔頻率的最大公約數。

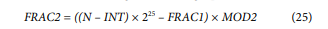

f_{CHSP}是所需的信道間隔頻率。 - 使用以下公式計算FRAC2(如果INT×$2^{25}$ + FRAC1×MOD2 < 16,383):

時實現零頻率誤差輸出。

如果不需要零頻率誤差,MOD1和MOD2分母共同作用,可創建一個39位分辨率的調制器。

整數N模式

當FRAC1和FRAC2都等于0時,合成器以整數N模式運行。建議將地址0x2B中的SD_EN_INTEGER位設為1,以禁用SDM,這可改善帶內相位噪聲,并減少任何額外的Σ-Δ噪聲。

R計數器

5位R計數器可對輸入參考頻率(輸入至REFP和REFN)進行分頻,以產生PFD的參考時鐘。允許的分頻比為1至32。

PFD和電荷泵

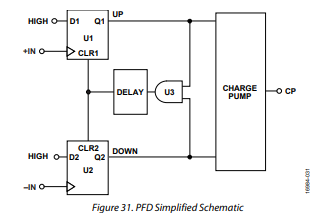

PFD對R計數器和N計數器進行計數,并輸出與兩個計數器之間的相位和頻率差成比例的信號。圖31是PFD的簡化示意圖。PFD包含一個固定延遲元件,用于設置反向脈沖的寬度。此脈沖可確保PFD轉換功能中不存在死區,并提供一致的參考雜散電平。將相位檢測器極性設為正,以消除VCO的負調諧方向。

圖31. PFD簡化示意圖

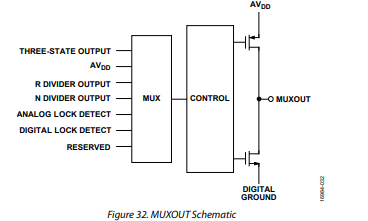

MUXOUT和鎖定檢測

ADF4372上的輸出多路復用器使用戶能夠訪問芯片上的各種內部節點。圖32以框圖形式展示了MUXOUT部分。

圖32. MUXOUT示意圖

雙緩沖

ADF4372中的主小數位(FRAC1)、輔助模數(MOD2)、輔助小數位(FRAC2)、參考倍頻器、參考二分頻器(RDIV2)、R計數器值和電荷泵電流設置均采用雙緩沖。有兩種情況會使雙緩沖使用新值。首先,新值必須鎖存到器件中,即寫入相應寄存器;其次,必須對地址0x10執行寫入操作。

例如,為確保模數正確加載,每次模數更新時都必須寫入地址0x10。

-

濾波器

+關注

關注

162文章

8003瀏覽量

180383 -

頻率合成器

+關注

關注

5文章

257瀏覽量

32648 -

pll

+關注

關注

6文章

863瀏覽量

135880 -

VCO

+關注

關注

13文章

241瀏覽量

69811

發布評論請先 登錄

相關推薦

貿澤電子發布Analog Devices ADF437x合成器

貿澤開售相位噪聲超低的Analog Devices ADF5610寬帶頻率合成器

CDF5356: 微波寬帶合成器和集成 VCO 數據表 ADI

ADF4372帶集成VCO的微波寬帶頻率合成器技術手冊

ADF4372帶集成VCO的微波寬帶頻率合成器技術手冊

評論