概述

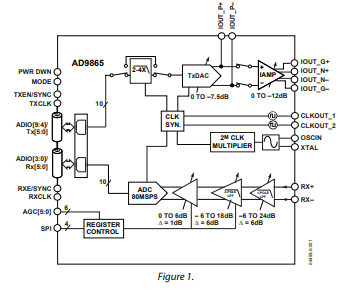

AD9865是一款混合信號前端(MxFE) IC,適合要求Tx和Rx路徑功能的收發器應用,數據速率最高可達80 MSPS。靈活的數字接口、省電模式和發射-接收高隔離度,使該器件特別適合半雙工和全雙工應用。該數字接口極為靈活,可與支持半雙工或全雙工數據傳輸的數字后端實現簡單接口,因此AD9865經常用來取代分立式ADC和DAC解決方案。省電模式能夠降低個別功能模塊的功耗,或者在半雙工應用中關斷未使用的模塊。串行端口接口(SPI?)允許對許多功能模塊進行軟件編程。片內PLL時鐘乘法器和頻率合成器提供所有需要的內部時鐘,以及單晶振或時鐘源的外部時鐘。

數據表:*附件:AD9865寬帶調制解調器混合信號前端技術手冊.pdf

Tx信號路徑由一個可旁路的2/4倍低通插值濾波器、一個10位TxDAC和一個線路驅動器組成。在輸入數據速率為80 MSPS時,發射路徑信號帶寬可以高達34 MHz。TxDAC提供差分電流輸出,可將該輸出直接導引至外部負載,或導引至內部低失真電流放大器。電流放大器(IAMP)可以配置為電流或電壓模式線路驅動器(采用兩個外部NPN晶體管),能夠提供23 dBm以上的峰值信號功率。Tx功率可以進行數字控制,范圍為19.5 dB,步進為0.5 dB。

接收路徑由可編程放大器(RxPGA)、可調諧低通濾波器(LPF)和10位ADC組成。低噪聲RxPGA具有?12 dB至+48 dB的可編程增益范圍,步進為1 dB。對于36 dB以上的增益設置,其折合到輸入端的噪聲低于3 nV/rtHz。接收路徑LPF截止頻率可以在15 MHz至35 MHz范圍內設置,或者簡單地予以旁路。10位ADC可以在5 MSPS至80 MSPS范圍內實現出色的動態性能。RxPGA和ADC均能提供可調整的功耗,以實現功耗/性能優化。

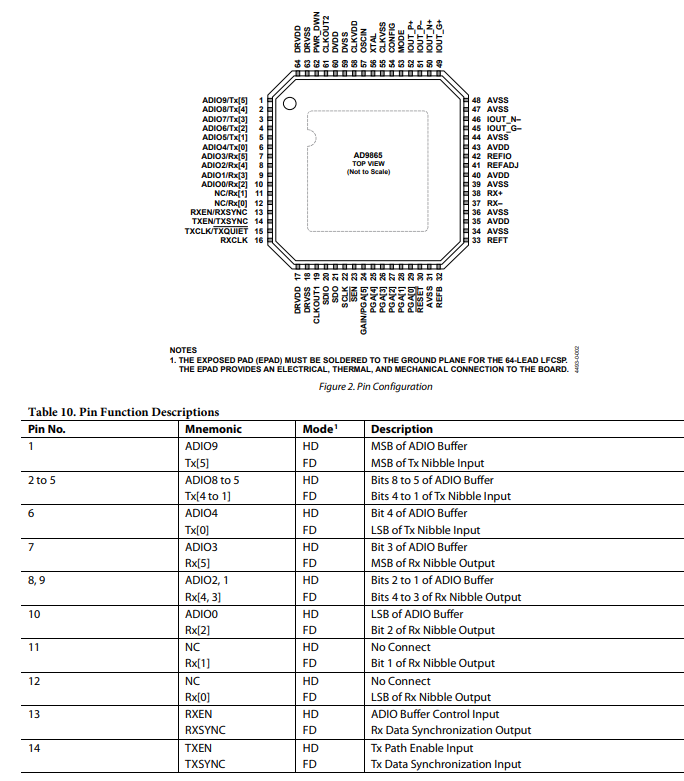

AD9865可以為許多寬帶調制解調器提供高度集成的解決方案。它采用節省空間的64引腳芯片級封裝,額定溫度范圍為?40°C至+85°C商用溫度范圍。

應用

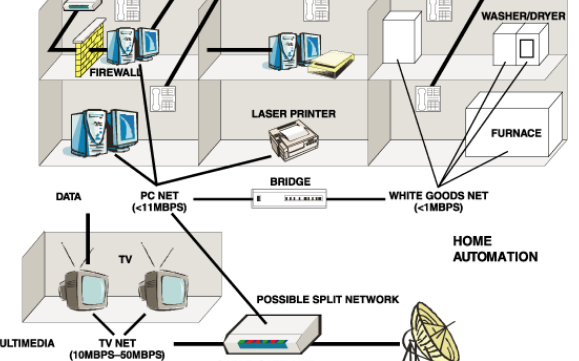

- 電力線網絡

- VDSL和HPNA

特性

- 低成本3.3 V CMOS MxFE?,適合寬帶調制解調器

- 10位數模轉換器

- 2/4倍插值濾波器

- DAC更新速率:200 MSPS

- 集成23 dBm線路驅動器,具有19.5 dB增益控制范圍

- 10位、80 MSPS模數轉換器

- ?12 dB至+48 dB低噪聲RxPGA (< 3.0="" />

- 三階可編程低通濾波器

- 靈活的數字數據路徑接口

- 半雙工和全雙工操作

- 與AD9975和AD9875向后兼容

- 多種關斷/省電模式

- 內部時鐘乘法器(PLL)

- 2路輔助可編程時鐘輸出

- 提供64引腳芯片級封裝或裸片

框圖

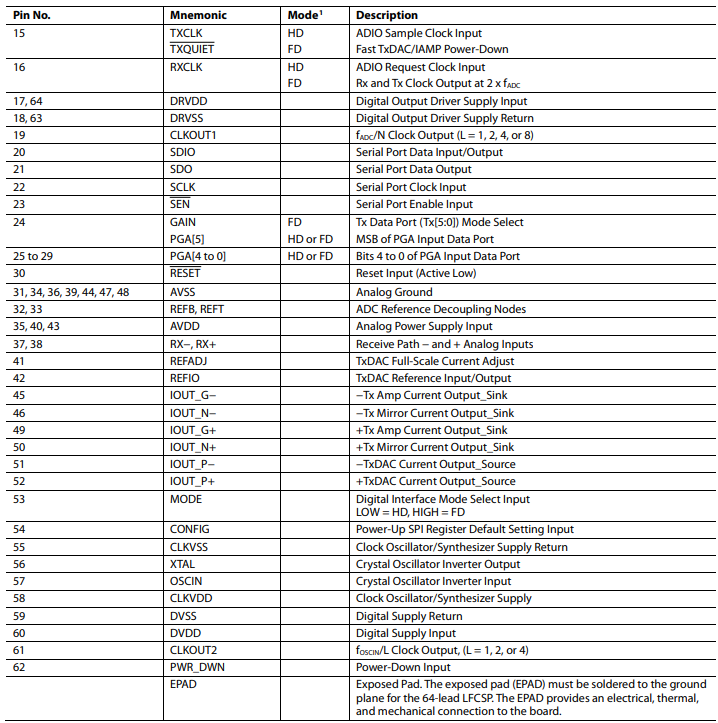

引腳配置描述

數字接口

數字接口端口可配置為半雙工或全雙工模式,通過將MODE引腳置低或高來實現。在半雙工模式下,發射路徑(Tx)和接收路徑(Rx)共享一個10位雙向總線,稱為ADIO端口。在全雙工模式下,數字接口分為兩個6位總線,即Tx(5:0)和Rx(5:0),用于同時進行Tx和Rx操作。在這種模式下,數據在AD9865 ASIC和AD9865外部的設備之間傳輸。AD9865還具有靈活的數字接口,可通過6位PGA端口更新RPGA和TxGA增益寄存器,或通過SPI端口進行較慢的更新。有關更多信息,請參閱RPGA控制部分。

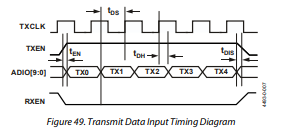

半雙工模式

當MODE引腳為低電平時,半雙工模式按以下方式工作。雙向ADIO端口通常在Tx數據路徑和Rx數據路徑之間交替共享。數字接口由AD9865 ASIC控制,通過使能ADIO端口的輸入并控制輸出驅動器來實現。兩個時鐘信號也會被使用:TXCLK用于鎖存Tx輸出數據,RXCLK用于鎖存Rx輸入數據。ADIO端口也可以通過將TXEN和RXEN設置為低電平(默認設置)來禁用,這樣可以與共享總線進行交互。

在內部,ADIO端口由一個輸入鎖存器和一個三態輸出緩沖器組成,用于將Tx路徑與Rx路徑并行連接。輸入鎖存器:RXEN用于將三態輸出設置為五樣本深度FIFO。輸入樣本在內部ADC時鐘(ADCLK)和外部采樣時鐘(TXCKS)之間對齊。當TXEN引腳為高電平時,ADIO總線會將Tx數據字傳輸到Tx路徑,并且在TXCLK引腳上有一個時鐘信號,如圖49所示。

在ADIO端口之后的抽取濾波器可以通過將RXEN引腳置低來與TXCLK解耦。這樣,抽取濾波器在TXEN為高電平的情況下,在33個時鐘周期內對數據進行濾波,然后在TXCLK上重新同步。

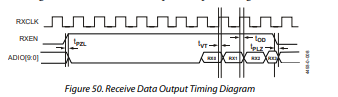

當RXEN引腳為高電平,且在RXCLK引腳上有一個時鐘信號時,輸出將來自接收路徑,并驅動ADIO總線。當輸出緩沖器使能時,數據將在RXCLK的六個時鐘周期延遲后從內部FIFO中輸出。

如果在此期間TXEN為高電平且TXCLK存在,ADIO將變為三態。一旦RXEN引腳變回低電平,ADIO將變為三態。圖50展示了接收路徑輸出時序。

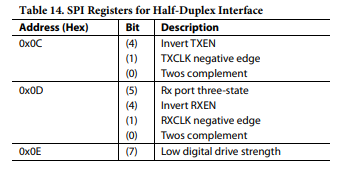

為了給數字接口端口增加靈活性,SPI寄存器中提供了幾個編程選項。默認情況下,Tx和Rx數據格式為直達二進制,但可以更改以實現補碼、偏移二進制或格雷碼。輸出驅動器可以設置為開漏極,以允許它們共享同一控制端。在這種情況下,ADIO端口仍可被置于共享總線,其輸入鎖存器可以通過SPI寄存器控制信號進行使能和禁用,并且輸出驅動器可以獨立調整。接收時鐘可以通過選擇時鐘的上升沿或下降沿來驗證/采樣接收路徑數據。最后,對于低數據速率應用,可以降低輸出驅動器的強度。

表14列出了半雙工模式下的SPI寄存器。

-

收發器

+關注

關注

10文章

3660瀏覽量

107596 -

混合信號

+關注

關注

0文章

506瀏覽量

65288 -

ad9865

+關注

關注

0文章

3瀏覽量

1245

發布評論請先 登錄

通信和電信>xDSL 調制解調器/DSLAM

GMSK基帶調制解調器的設計與實現

AD9969: 單電源電纜調制解調器/機頂盒混合信號前端

調制解調器(Modem),調制解調器(Modem)是什么意思

AD9969: 單電源電纜調制解調器/機頂盒混合信號前端

ad9865寬帶調制解調器混合信號前端數據表

AD9865 寬帶調制解調器混合信號前端

AD9865寬帶調制解調器混合信號前端技術手冊

AD9865寬帶調制解調器混合信號前端技術手冊

評論