概述

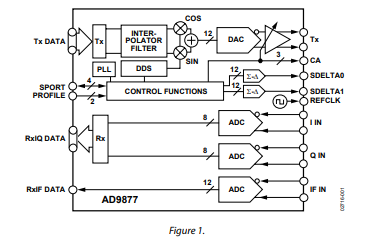

AD9877是一款單電源電纜調制解調器/機頂盒混合信號前端,內置發射路徑插值濾波器、完整正交數字上變頻器和發射DAC。接收路徑內置12位ADC和雙通道8位ADC。內部需要的所有時鐘和輸出系統時鐘均由PLL從單晶體或時鐘輸入產生。

數據表:*附件:AD9877單電源電纜調制解調器 機頂盒混合信號前端技術手冊.pdf

發射路徑插值濾波器提供12或16倍的升采樣系數,輸出信號帶寬高達8.4 MHz。直接數字頻率合成器(DDS)可以產生最高65 MHz的載波頻率,頻率調諧分辨率為26位。發射DAC的分辨率為12位,能以高達232 MSPS的采樣速率工作。模擬輸出可以在0 dB至7.5 dB范圍內調整,步進為0.5 dB,以便在輸出電平需要降低時保持發射路徑信噪比(SNR)性能。

12位ADC具有出色的欠采樣性能,使其可提供10個以上的有效位數(ENOB),中頻輸入最高可達75 MHz。12位中頻ADC的采樣速率最高達33MHz,使其可以處理寬帶信號輸入。

提供兩個可編程Σ-Δ型DAC,可用來控制可變增益放大器(VGA)或電壓控制調諧器等外部元件。

該器件集成有CA端口,使主機處理器能通過MxFE串行端口(SPORT)控制AD8321/AD8323或AD8322/AD8327可編程增益放大器(PGA)電纜驅動器。

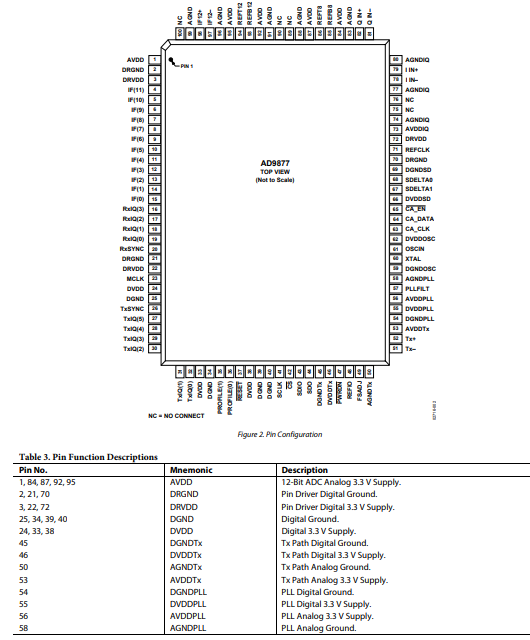

AD9877采用100引腳MQFP封裝。與引腳兼容產品AD9873相比,其接收路徑欠采樣性能更佳,成本更低。額定溫度范圍為-40oC至+85oC工業溫度范圍。

特性

- 低成本3.3 V CMOS MxFE ^?^ ,用于MCNS-DOCSIS、DVB、DAVIC兼容機頂盒和電纜調制解調器應用

- 232 MHz正交數字上變頻器

- 12位直接中頻DAC (TxDAC+ ^?^ )

- 最高65 MHz載波頻率DDS

- 可編程采樣時鐘速率

- 可選插值濾波器

- 模擬發射輸出電平可調

- 12位、33 MSPS直接中頻ADC

- 雙通道、8位、16.5 MSPS采樣IQ ADC

- 兩個12位Σ-Δ型輔助DAC

- 與AD8321/AD8325或AD8322/AD8327直接接口

- PGA電纜驅動器

框圖

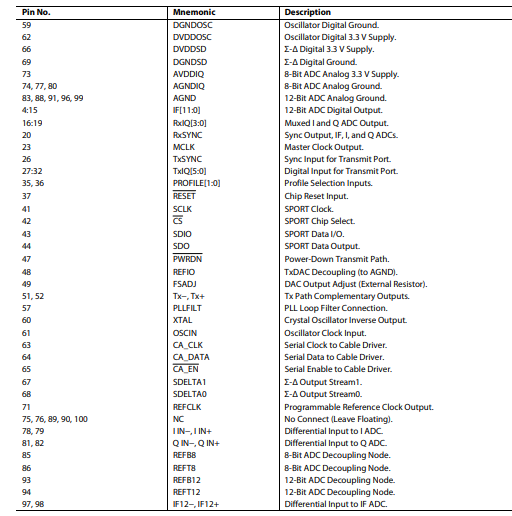

引腳配置描述

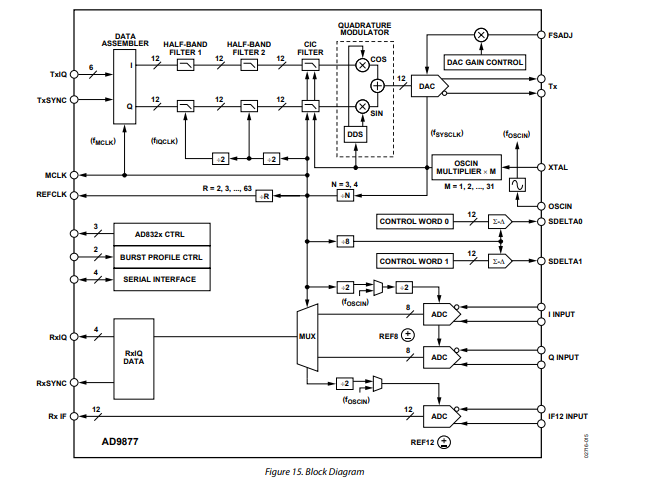

若要對AD9877有一個總體了解,請參考圖15中的器件架構框圖。以下是對該器件功能的一般性描述。后續部分將詳細介紹數據路徑的各個模塊。

發射部分

調制模式操作

AD9877接收兩個6位字,這些字與主時鐘(MCLK)同步選通進入數據匯編器。MCLK上的高電平啟動一個傳輸符號。兩個連續的6位字組成一個12位復數符號。傳入的數據被格式化為12位復數,其中交替的12位字分別被視為同相(I)和正交(Q)分量。一個符號的I和Q分量假定為二進制補碼格式。傳輸I/Q數據的速率將被稱為符號速率(fsymb),它是主時鐘速率(fMCLK)的四分之一。

數據匯編器接收多路復用的I/Q數據,并創建兩個并行的12位路徑,分別包含I和Q數據對,它們構成一個復數符號。數據匯編器輸出端出現的I和Q數據字對被稱為I/Q樣本(fsamp)。由于每個復數符號需要四個24位讀取操作,因此fsymb是I/Q樣本速率(fsamp)的四分之一(fsymb = fsamp × 4)。

一旦通過數據匯編器,I/Q數據流將被送入兩個半帶濾波器(半帶濾波器1和2)。這兩個濾波器的組合使樣本速率提高4倍。因此,在半帶濾波器的輸出端,樣本速率為4 × fsymb,即fMCLK。除了提高樣本速率外,半帶濾波器還提供必要的低通濾波特性,以抑制頻譜鏡像。

-

混合信號

+關注

關注

0文章

508瀏覽量

65368 -

調制解調器

+關注

關注

3文章

874瀏覽量

39616 -

前端

+關注

關注

1文章

214瀏覽量

18283

發布評論請先 登錄

通信和電信>xDSL 調制解調器/DSLAM

ST推出業界首款16x4通道DOCSIS 3.0線纜調制解調器芯片

AD9877 單電源電纜調制解調器/機頂盒混合信號前端(MxFE?)

用于寬帶數字機頂盒混合信號中的AD9873芯片介紹

AD9873用于寬帶數字機頂盒的混合信號前端

AD9877單電源電纜調制解調器/機頂盒混合信號前端技術手冊

AD9877單電源電纜調制解調器/機頂盒混合信號前端技術手冊

評論