概述

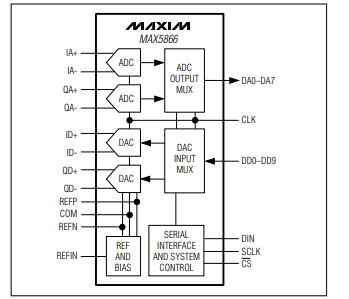

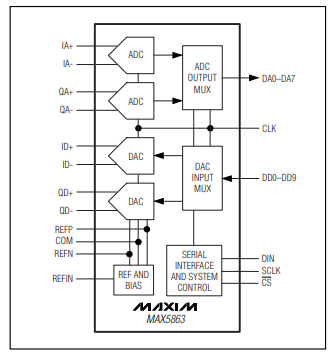

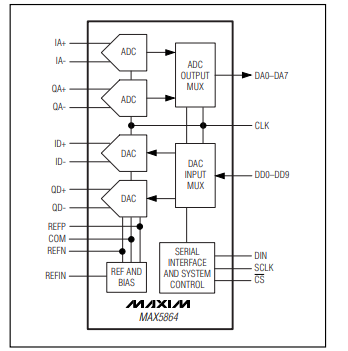

MAX5865超低功耗、高度集成的模擬前端適用于便攜式通信設備,如手機、PDA、WLAN以及3G無線終端。MAX5865集成了雙路8位接收ADC和雙路10位發送DAC,以極低的功耗提供更高的動態性能。ADC的模擬I-Q輸入放大器為全差分模式,可以接受1VP-P滿量程信號。I-Q通道相位匹配典型值為±0.2°,幅度匹配典型值為±0.05dB。fIN = 5.5MHz和fCLK = 40MHz時,ADC的SINAD為48.4dB,無雜散動態范圍(SFDR)為70dBc。DAC的模擬I-Q輸出為全差分模式,滿量程輸出為±400mV,共模電壓為1.4V。I-Q通道的相位匹配為±0.15°,增益匹配為±0.05dB。fOUT = 2.2MHz和fCLK = 40MHz時,DAC也具有雙路10位分辨率,SFDR為72dBc、SNR為57dB。

針對頻分雙工(FDD)與時分雙工(TDD)模式,ADC與DAC可以同時工作或獨立工作。3線串行接口控制關端和收發器的工作模式。收發模式下ADC與DAC同時工作、fCLK = 40Msps時,功耗典型值為75.6mW。MAX5865具有內部1.024V電壓基準,在整個電源供電范圍與工作溫度范圍內保持穩定。MAX5865工作在+2.7V至+3.3V模擬電源,為保證邏輯兼容性帶有一個+1.8V至+3.3V數字I/O電源輸入。空閑模式下靜態電流為8.5mA,關斷模式下為1μA。MAX5865工作溫度范圍為-40°C至+85°C,采用48引腳薄型QFN封裝。

數據表:*附件:MAX5865超低功耗、高動態性能、40Msps模擬前端技術手冊.pdf

應用

- 3G無線終端

- 固定/移動寬帶無線調制解調器

- 窄帶/寬帶CDMA手機

- PDA

特性

- 集成的雙路8位ADC與雙路10位DAC

- 超低功耗

- f

CLK= 40MHz時75.6mW (收發器模式) - f

CLK= 22MHz時64mW (收發器模式) - 低電流空閑與關斷模式

- f

- 優越的動態性能

- f

IN= 5.5MHz時SINAD為48.4dB (ADC) - f

OUT= 2.2MHz時SFDR為70dB (DAC)

- f

- 優越的增益/相位匹配

- f

IN= 5.5MHz時±0.2°相位匹配,±0.05dB增益(ADC)匹配

- f

- 內部/外部基準選擇

- +1.8V至+3.3V數字輸出電壓(TTL/CMOS兼容)

- 為ADC/DAC提供多路復用并行數字輸入/輸出

- 微型48引腳薄型QFN封裝(7mm x 7mm)

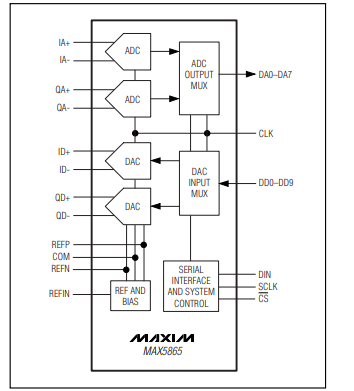

框圖

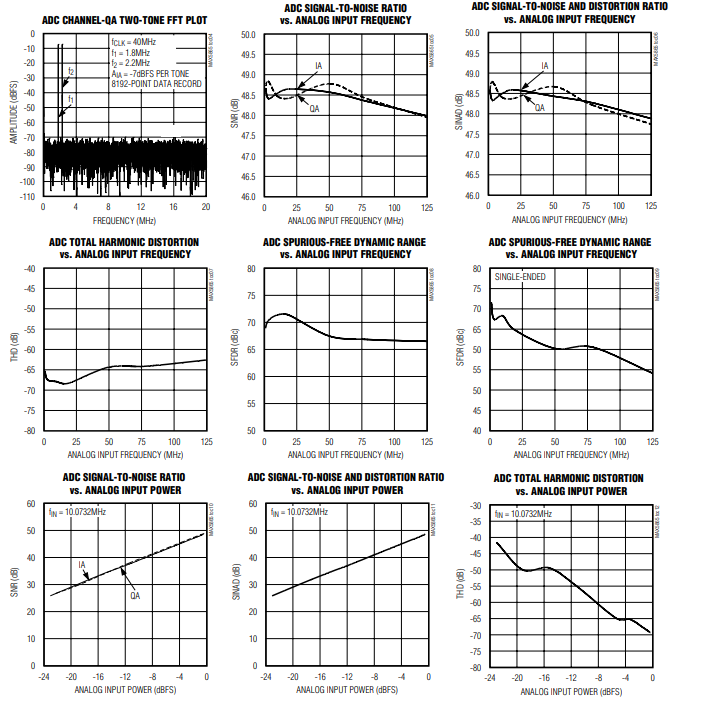

典型操作特性

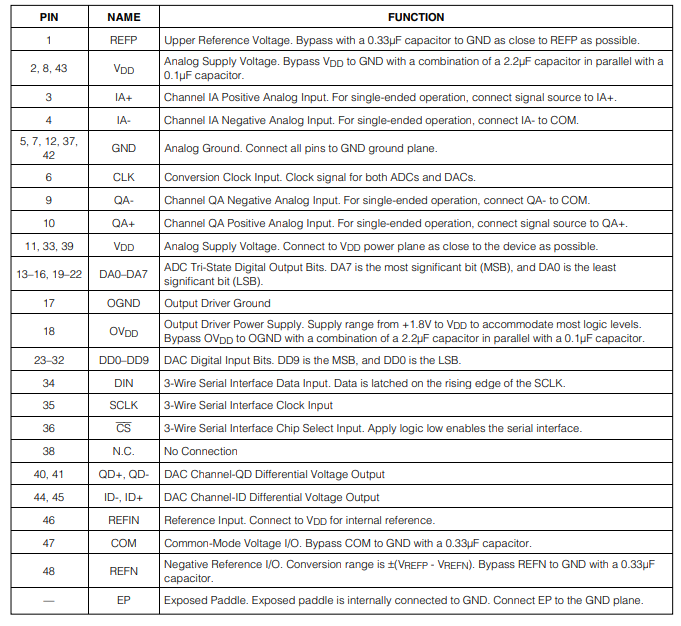

引腳描述

應用信息

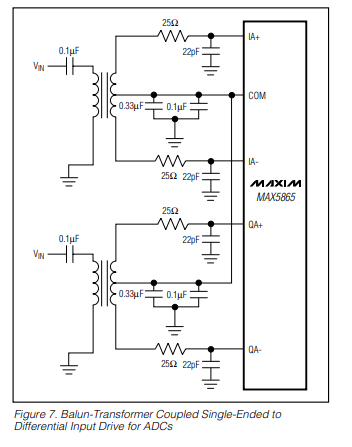

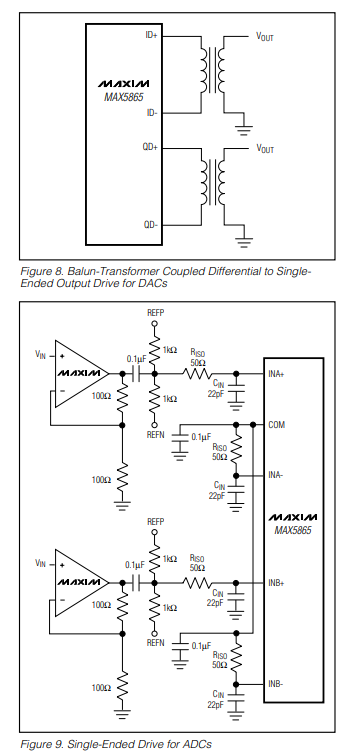

使用平衡 - 不平衡變壓器交流耦合

射頻變壓器(圖7)為將單端信號源轉換為全差分信號提供了極佳方案,有助于實現ADC的最佳性能。將變壓器的中心抽頭連接到COM引腳,可使輸入獲得VDD/2的直流電平偏移。可以選擇1:1變壓器,也可選用升壓變壓器來降低驅動要求。一般來說,MAX5865在處理全差分輸入信號方面優于SPDR和THD信號,尤其是在較高輸入頻率下。在差分模式中,由于兩個輸入端(IA+、IA - 、QA+、QA - )相互平衡,偶次諧波更低,并且每個ADC輸入所需的信號擺幅僅為單端模式下的一半。圖8展示了一個使用射頻變壓器將MAX5865 DAC的差分模擬輸出轉換為單端輸出的示例。

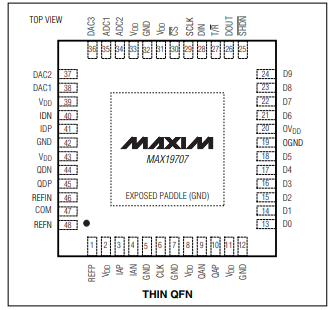

使用運算放大器耦合

當沒有平衡 - 不平衡變壓器可用時,可用運算放大器驅動MAX5865的模數轉換器(ADC)。圖9和圖10展示了在交流耦合單端和直流耦合差分應用中,用運算放大器驅動ADC的情況。像MAX4354、MAX4454這類放大器具備高速、高帶寬、低噪聲和低失真特性,可維持輸入信號完整性。圖10中的電路也可用于數模轉換器(DAC)差分模擬輸出的接口,以提供增益或緩沖。DAC差分模擬輸出不能用于單端模式,因為其內部產生的共模電平為1.4 VDC 。此外,DAC模擬輸出設計要求采用差分輸入級,且輸入阻抗需≥70 kΩ。若需要單端輸出,可使用一個放大器來實現差分轉單端轉換,并選擇具有合適輸入共模電壓范圍的放大器。

頻分雙工(FDD)和時分雙工(TDD)模式

MAX5865可用于多種工作在FDD或TDD模式下的應用。在FDD模式下,MAX5865可用于Xcvr模式的應用,如WCDMA 3GPP(FDD)和4G技術。此外,MAX5865還能在Tx和Rx模式間切換,適用于TD - SCDMA、WCDMA - 3GPP(TDD)、IEEE 802.11a/b/g和IEEE 802.16等TDD應用。

在FDD模式下,ADC和DAC同時工作。ADC總線和DAC總線相互隔離,且必須分別連接到18位并行總線(8位ADC和10位DAC)的數字基帶處理器。通過三線串行接口選擇Xcvr模式,并使用轉換時鐘來鎖存數據。在FDD模式下,當fCLK = 40MHz時,MAX5865的功耗為7.6mW 。這是ADC和DAC同時工作時的總功耗。

在TDD模式下,ADC和DAC獨立工作。ADC和DAC總線可連接在一起,形成一個10位并行總線,連接到數字基帶處理器。通過三線串行接口,在Rx模式下使能ADC,在Tx模式下使能DAC。在Rx模式下工作時,DAC不傳輸數據,其內核被禁用,ADC總線處于三態,這樣可消除任何不需要的寄生發射,防止總線競爭。在TDD模式下,當fCLK = 40MHz時,MAX5865在Rx模式下的功耗為6.3mW ,Tx模式下DAC的功耗為3.4mW。

-

dac

+關注

關注

43文章

2353瀏覽量

192735 -

模擬前端

+關注

關注

3文章

207瀏覽量

30208 -

ADC

+關注

關注

0文章

188瀏覽量

16845

發布評論請先 登錄

相關推薦

低功耗模擬前端芯片MAX586的工作原理是什么?

超低功耗高度集成的模擬前端MAX5865電子資料

超低功耗模擬前端集成電路MAX19705相關資料分享

MAX5865中文資料pdf

LTC2192/LTC2191/LTC2190:16位、65Msps/40Msps/25Msps低功耗雙ADC產品手冊

LTC2182/LTC2181/LTC2180:16位、65Msps/40Msps/25Msps低功耗雙ADC產品手冊

MAX5865超低功耗、高動態性能、40Msps模擬前端技術手冊

MAX5865超低功耗、高動態性能、40Msps模擬前端技術手冊

評論