概述

MAX1005是一款組合式數(shù)字化儀和重建集成電路,可用于通信信號解調(diào)和調(diào)制系統(tǒng)。它將IF欠采樣和信號合成功能集成到單個(gè)低功耗電路中。其模數(shù)轉(zhuǎn)換器(ADC)用于直接采樣或欠采樣下變頻的RF信號,而其數(shù)模轉(zhuǎn)換器(DAC)則重新創(chuàng)建IF子載波和傳輸數(shù)據(jù)。由于模擬輸入放大器具有(15MHz)寬帶寬,MAX1005的ADC非常適合欠采樣應(yīng)用。DAC的毛刺能量非常低,從而充分減少了干擾雜散信號的傳輸。片上基準(zhǔn)電壓源提供低噪聲ADC和DAC轉(zhuǎn)換。

MAX1005以低功耗預(yù)算提供高水平的信號完整性。它采用單電源供電,或者采用獨(dú)立的模擬和數(shù)字電源供電,各自電壓范圍為+2.7V至+5.5V。MAX1005可以采用5.5V的非穩(wěn)壓模擬電源和低至2.7V的穩(wěn)壓數(shù)字電源供電。這種靈活的電源操作可以在復(fù)雜的數(shù)字系統(tǒng)中進(jìn)一步省電。

MAX1005具有三種工作模式:發(fā)射(DAC有效)、接收(ADC有效)和關(guān)斷(ADC和DAC無效)。在關(guān)斷模式下,總電源電流降至1μA以下。該器件只需2.4μs即可從關(guān)斷模式中喚醒。MAX1005非常適合手持式以及基站應(yīng)用。它采用小型16引腳QSOP封裝,額定工作溫度范圍為商業(yè)和擴(kuò)展溫度范圍。

數(shù)據(jù)表:*附件:MAX1005 IF欠采樣量化器技術(shù)手冊.pdf

應(yīng)用

- PCS/N

- PHS/P

- PWT1900

- 無線環(huán)路

特性

- 差分輸入5位ADC

- 差分輸出7位DAC

- 15Msps最小轉(zhuǎn)換速率

- -1dB全功率帶寬:25MHz

- ADC的SFDR為44dB

- DAC在10.7MHz時(shí)的SFDR(成像)為39dB

- 內(nèi)部基準(zhǔn)電壓源

- 并行邏輯接口

- 單電源供電(+2.7V至+5.5V)

- 低功耗關(guān)斷模式:0.1μA

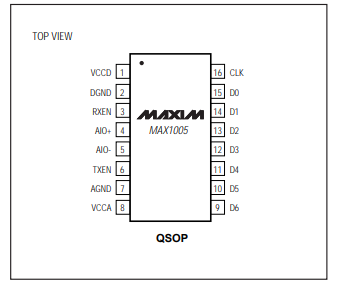

引腳配置

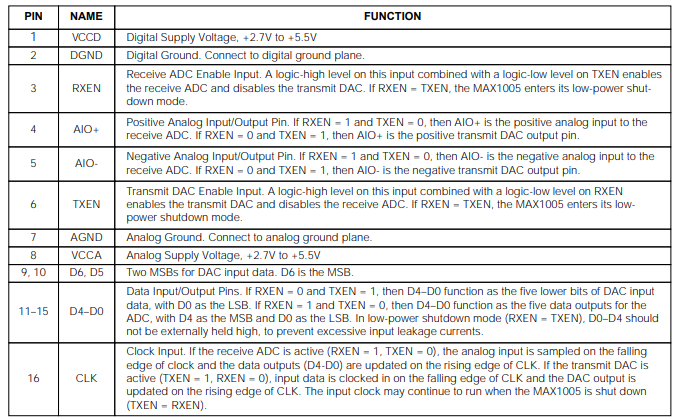

典型操作特性

電源去耦與接地

MAX1005設(shè)有獨(dú)立的模擬電源引腳(VCCA)和數(shù)字電源引腳(VCCD),同時(shí)也有獨(dú)立的模擬地引腳和數(shù)字地引腳,目的是將電路中模擬信號與數(shù)字信號間的串?dāng)_降至最低。該器件可在2.7V至5.5V之間的任一電源電壓下工作。這一特性使得數(shù)字電路能從經(jīng)調(diào)節(jié)的邏輯電源供電,從而降低功耗,同時(shí)保持與外部邏輯的兼容性,并且允許模擬電路在未經(jīng)過調(diào)節(jié)的電源下運(yùn)行。

模擬地(AGND)和數(shù)字地(DGND)應(yīng)在靠近器件處相連。任何時(shí)候,AGND與DGND之間的電壓差都不應(yīng)超過0.3V。

整個(gè)電路板的模擬電源和數(shù)字電源都需要良好的直流去耦。在電源引腳上放置電源去耦電容,使電流路徑盡可能短地回流到電源。建議使用等效串聯(lián)電阻(ESR)較低的10μF電解電容。為實(shí)現(xiàn)最佳的比特性能,盡量減少電容負(fù)載,使數(shù)字輸出走線盡可能短。分別在每個(gè)VCC電源引腳旁,放置盡可能靠近器件封裝的高品質(zhì)陶瓷電容進(jìn)行去耦。

-

集成電路

+關(guān)注

關(guān)注

5420文章

11991瀏覽量

367586 -

通信

+關(guān)注

關(guān)注

18文章

6184瀏覽量

137499 -

ADC

+關(guān)注

關(guān)注

0文章

208瀏覽量

16845

發(fā)布評論請先 登錄

合理選擇高速ADC實(shí)現(xiàn)欠采樣

基于欠采樣的單頻率估計(jì)的設(shè)計(jì)與實(shí)現(xiàn)

欠采樣超寬帶LFM信號參數(shù)估計(jì)

高速、高精度頻率采樣中的量化誤差分析

欠采樣中頻收發(fā)器體系結(jié)構(gòu)研究

三種用于垃圾網(wǎng)頁檢測的隨機(jī)欠采樣集成分類器

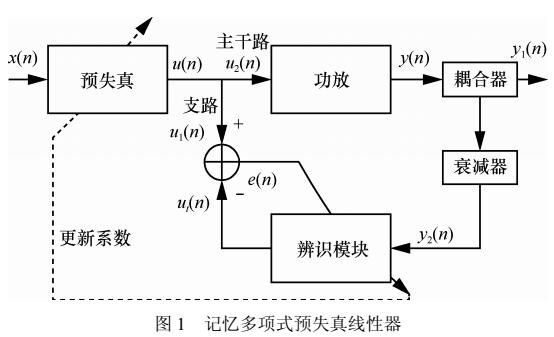

壓縮感知的欠采樣預(yù)失真技術(shù)

MAX1005EEE+ RF 其它 IC 和模塊

MAX1005CEE+T RF 其它 IC 和模塊

MAX1005EEE+T RF 其它 IC 和模塊

MAX1005CEE+ RF 其它 IC 和模塊

奈奎斯特準(zhǔn)則如何運(yùn)用于基帶采樣、欠采樣和過采樣應(yīng)用

MAX1005 IF欠采樣量化器技術(shù)手冊

MAX1005 IF欠采樣量化器技術(shù)手冊

評論