一、測量背景與意義

在高速電路系統設計中,共模電壓作為影響信號完整性和EMI性能的關鍵參數,其精準測量已成為電子工程師的重要課題。傳統單探頭測量法存在共模抑制比不足的缺陷,本文提出基于雙差分探頭的創新測量方案,通過理論推導與實驗驗證相結合的方式,系統闡述該方法的實施要點。

二、差分測量系統的核心要素

- 差分信號特征體系

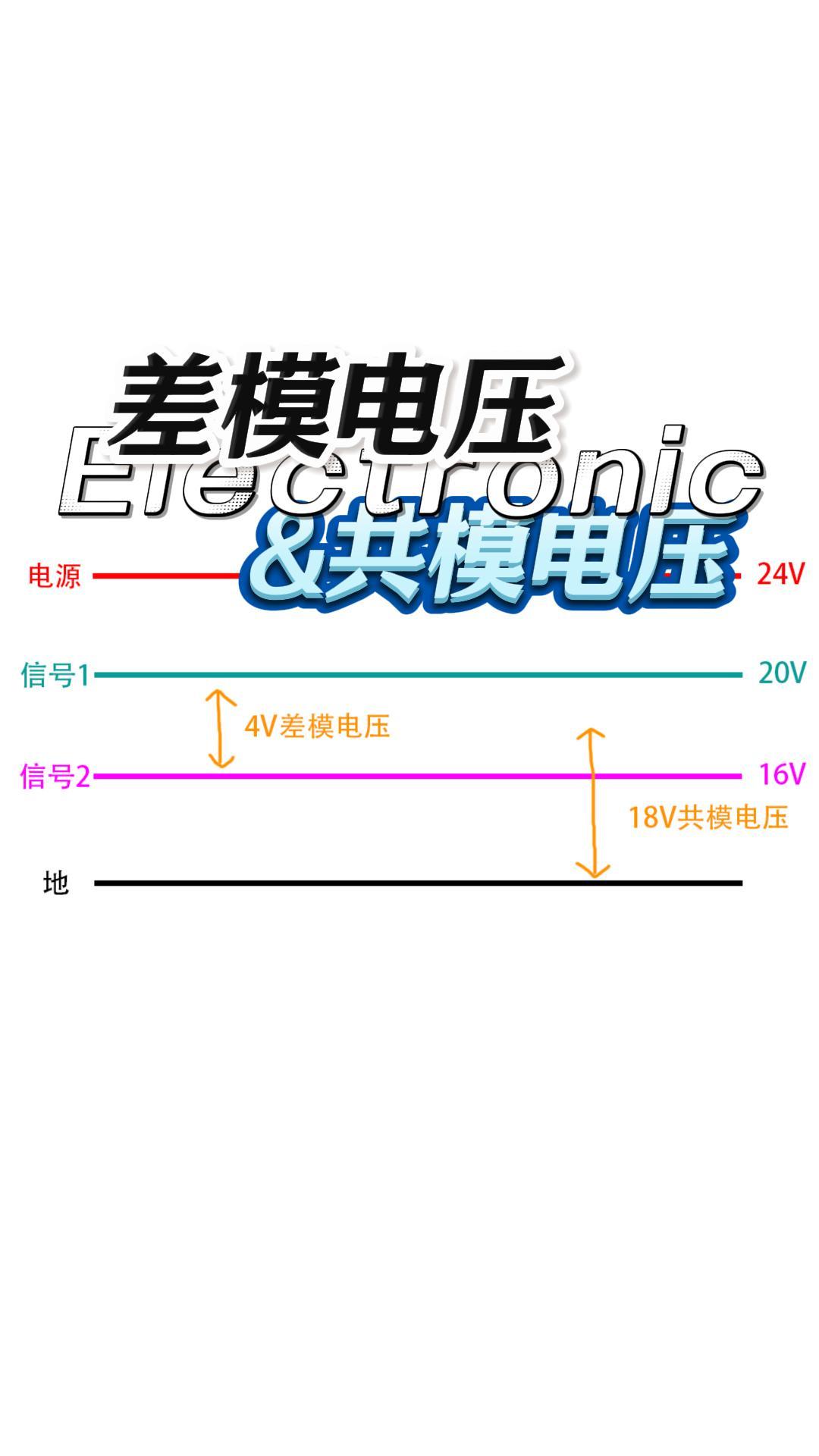

- 理想差分模型:Vdiff = (V+ - V-)/2

- 實際共模干擾:Vcm = (V+ + V-)/2

- 信號傳輸矩陣:建立包含線路阻抗和寄生參數的數學模型

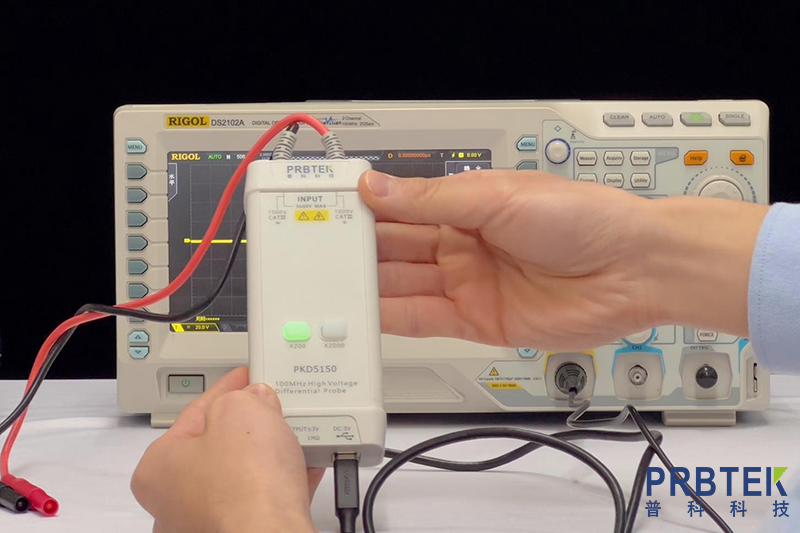

- 差分探頭的技術規范

- 共模抑制比(CMRR)與帶寬的匹配準則

- 輸入阻抗匹配原則(推薦>100kΩ)

- 動態范圍與衰減比的選擇依據

三、雙探頭測量法的實施流程

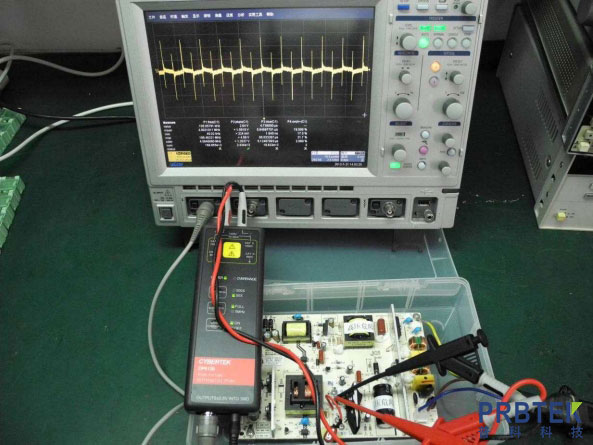

系統配置方案

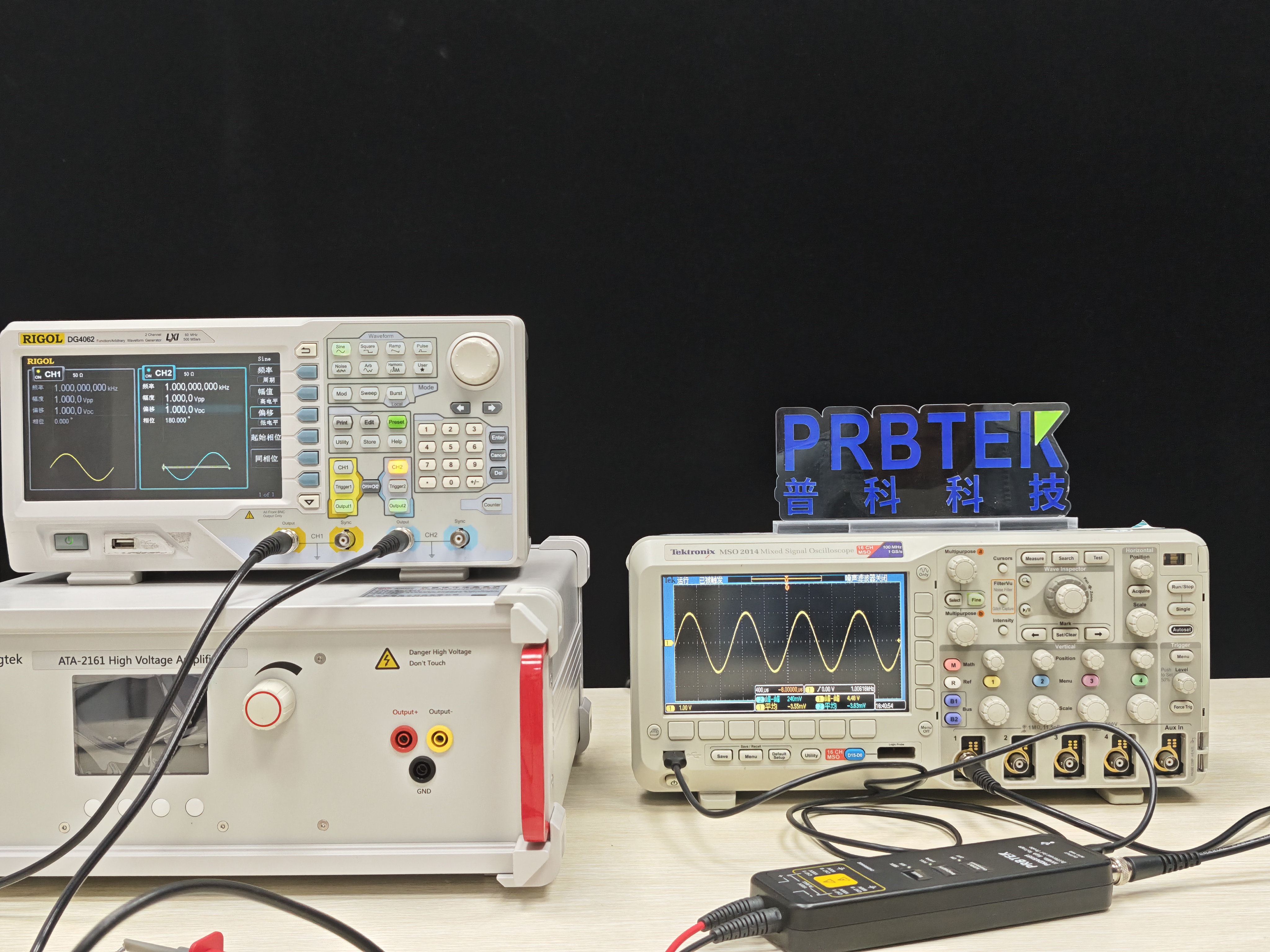

采用Tektronix THDP系列差分探頭搭建雙通道測量平臺,具體配置:

① 探頭A/B分別接入待測點P1/P2

② 共地連接采用星型拓撲結構

③ 示波器選用高精度數字存儲示波器(建議分辨率≥12bit)

信號采集與處理

- 同步觸發設置:確保雙通道采樣時鐘同步誤差<10ps

- 數字濾波處理:應用FIR濾波器消除高頻噪聲

- 數據補償算法:通過公式Vcm_corrected=(V1+V2)/2 - ΔVoffset實現系統誤差補償

四、誤差分析與優化策略

- 主要誤差來源

- 探頭增益偏差(典型值±1.5%)

- 通道間延遲失配(ns級時延導致相位誤差)

- 溫度漂移效應(0.05%/℃的增益溫漂)

-

校準技術方案

開發基于標準信號源的自動校準程序:

① 注入已知共模電壓進行基線校準

② 掃頻測試獲取頻率響應曲線

③ 建立誤差查找表(LUT)實現動態補償

五、工程驗證與數據分析

在某高速SerDes接口測試中,使用本方法獲得:

- 共模電壓測量精度:±2mV(@1Vpp)

- 噪聲抑制能力:60dB@100MHz

- 測量重復性誤差:<0.3%

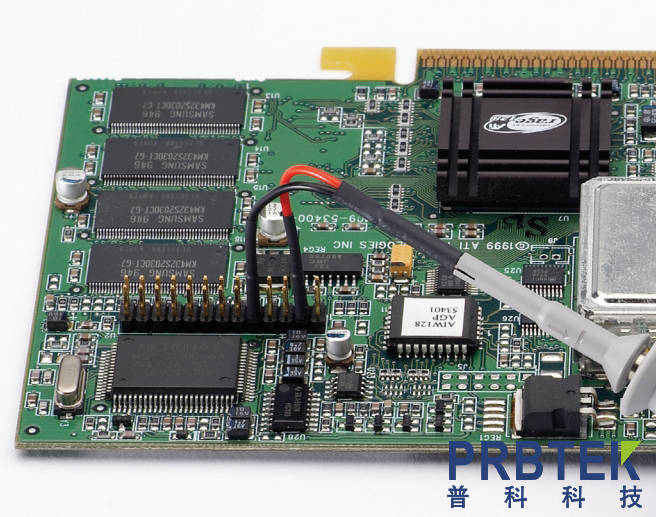

實驗數據表明,相較傳統方法,本方案將測量不確定度降低了72%,特別適用于PCIe 5.0、DDR5等高速接口的共模噪聲分析。

六、技術拓展與應用前景

本測量方法已成功應用于:

隨著5G通信和人工智能芯片的發展,該方法在28Gbps以上高速信號檢測領域展現出獨特優勢。未來研究將聚焦于集成化測量系統的開發,實現自動CMRR校準和實時數據分析功能。

以上內容由普科科技/PRBTEK整理分享, 西安普科電子科技有限公司致力于打造儀器配附件一站式供應平臺。主營范圍:示波器測試附件配件的研發、生產、銷售。涵蓋產品包含電流探頭、差分探頭、高壓探頭、無源探頭、柔性電流探頭、近場探頭、電流互感器、射頻測試線纜、各類儀器測試附件等。更多信息,歡迎登陸官方網站進行咨詢,在此期待您的到訪。

審核編輯 黃宇

-

共模電壓

+關注

關注

2文章

108瀏覽量

13012 -

差分探頭

+關注

關注

0文章

223瀏覽量

10298

發布評論請先 登錄

什么是共模信號和差模信號,光隔離探頭的高共模抑制比有什么用?

雙差分探頭法精準測量共模電壓的技術解析

雙差分探頭法精準測量共模電壓的技術解析

評論