概述

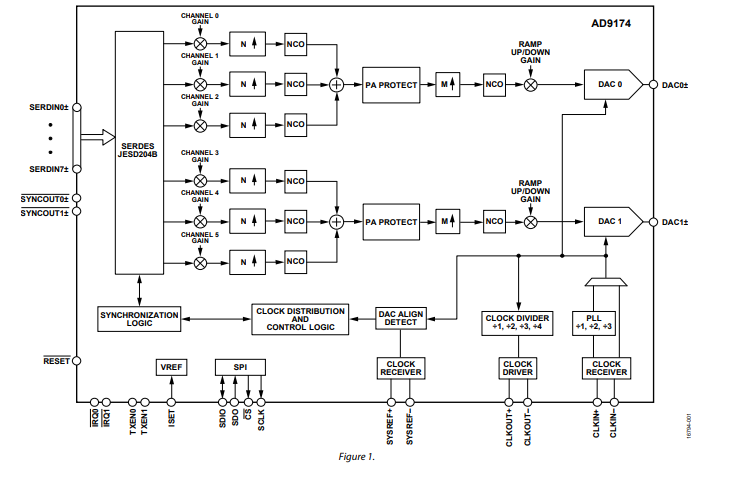

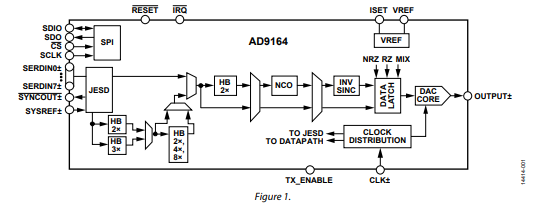

AD9174是一款高性能、雙通道、16位數(shù)模轉(zhuǎn)換器(DAC),支持高達12.6 GSPS的DAC采樣速率。該器件具有8通道、15.4 Gbps JESD204B數(shù)據(jù)輸入端口、高性能片內(nèi)DAC時鐘倍頻器和數(shù)字信號處理功能,適合單頻段和多頻段直接至射頻(RF)無線應(yīng)用。

數(shù)據(jù)表:*附件:AD9174雙路、16位、12.6 GSPS RF DAC和直接數(shù)字頻率合成器技術(shù)手冊.pdf

AD9174的每個RF DAC數(shù)據(jù)路徑具有三個復(fù)數(shù)數(shù)據(jù)輸入通道。每個輸入通道完全可旁路。每個數(shù)據(jù)輸入通道(或通道選擇器)包括可配置增益級、插值濾波器和通道數(shù)控振蕩器(NCO),方便靈活的多頻段頻率規(guī)劃。AD9174支持高達3.08 GSPS復(fù)數(shù)(同相/正交(I/Q))或高達6.16 GSPS非復(fù)數(shù)(實數(shù))的輸入數(shù)據(jù)速率,能夠?qū)⒍鄠€復(fù)數(shù)輸入數(shù)據(jù)流分配至指定通道進行單獨處理。每組三個通道選擇器增加到各自的主數(shù)據(jù)路徑中,以便在需要時進行額外處理。每個主數(shù)據(jù)路徑包括一個插值濾波器和一個位于RF DAC內(nèi)核之前的48位主NCO。通過使用調(diào)制器開關(guān),主數(shù)據(jù)路徑輸出可單獨連接到DAC0以便用作單一DAC,或連接到DAC0和DAC1以便用作雙通道、中頻DAC (IF DAC)。

AD9174還支持超寬數(shù)據(jù)速率模式,以便旁路通道選擇器和主數(shù)據(jù)路徑,從而作為單通道16位DAC提供高達6.16 GSPS的數(shù)據(jù)速率,或作為雙通道16位DAC提供高達3.08 GSPS的數(shù)據(jù)速率,或作為雙通道12位置DAC提供高達4.1 GSPS的數(shù)據(jù)速率。

此外,AD9174中的主要NCO模塊包含一組31個32位NCO,每個都有獨立的相位累加器。此組與用于NCO編程的80 MHz串行外設(shè)接口(SPI)相結(jié)合,可實現(xiàn)相位相干快速跳頻(FFH),適合在工作期間連續(xù)調(diào)整NCO頻率的應(yīng)用。

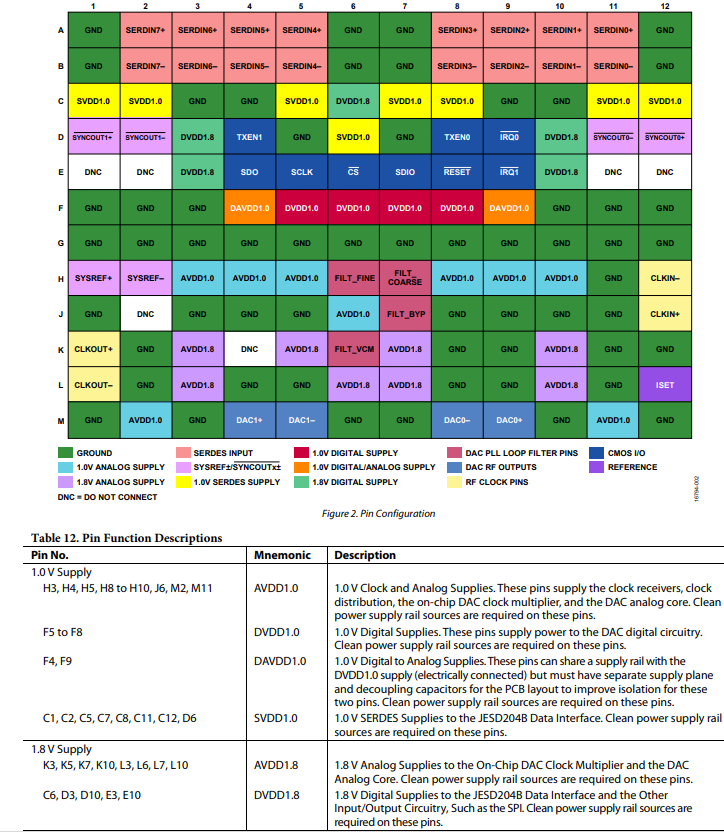

AD9174采用144引腳BGA_ED封裝。

應(yīng)用

特性

- 支持多頻段無線應(yīng)用

- 每個 RF DAC 具有 3 個可旁路復(fù)用數(shù)據(jù)輸入通道

- 每個輸入通道的最大復(fù)用輸入數(shù)據(jù)速率

達 3.08 GSPS - 每個輸入通道具有 1 個獨立的 NCO

- 專用的低雜散和失真設(shè)計

- 雙信號音 IMD3 = 1.84 GHz 時為 ?83 dBc,?7 dBFS/音調(diào) RF 輸出

- 1.84 GHz 時 SFDR

- 靈活的 8 線、15.4 Gbps JESD204B 接口

- 支持單頻段和多頻段使用案例

- 支持 12 位高密度模式,用于增加的數(shù)據(jù)吞吐量

- 多芯片同步

- 支持 JESD204B 子類 1

- 可選擇內(nèi)插濾波器,適用于全套輸入數(shù)據(jù)速率

- 1×、2×、3×、4×、6× 和 8× 可配置數(shù)據(jù)通道插值

- 1×、2×、4×、6×、8× 和 12× 可配置最終插值

- 最終的 48 位 NCO,以 DAC 速率運行,可支持高達 6 GHz 的頻率合成

- 發(fā)射使能功能可實現(xiàn)額外省電和下游電路保護

- 高性能、低噪聲 PLL 時鐘倍頻器

- 低功耗

- 2.54 W,12 GSPS 時為 2 DAC,10 mm × 10 mm 上的 DAC PLL,具有金屬增強隔熱蓋的 144 球 BGA_ED 封裝,間距為 0.80 mm

框圖

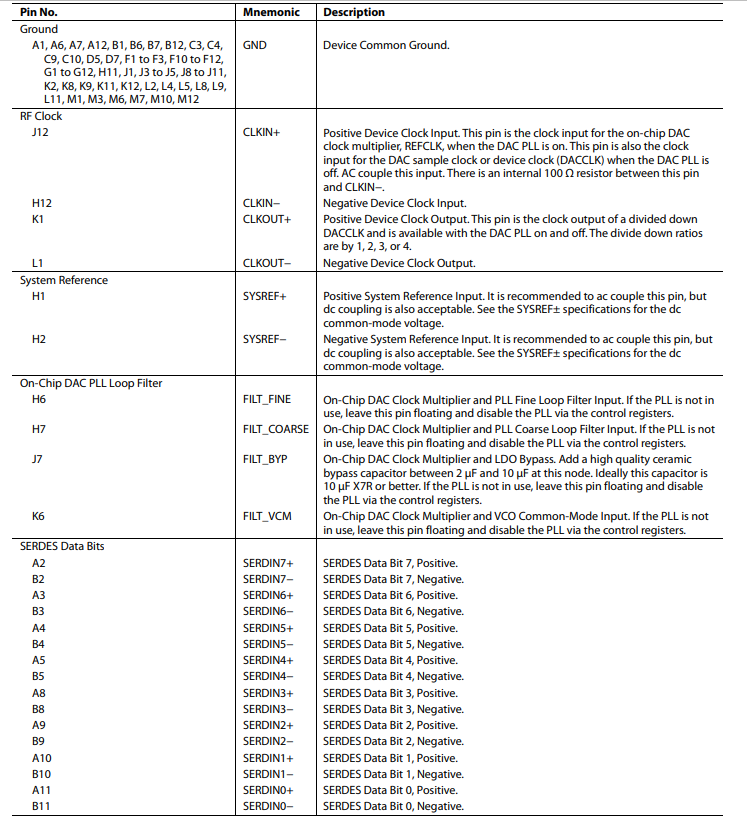

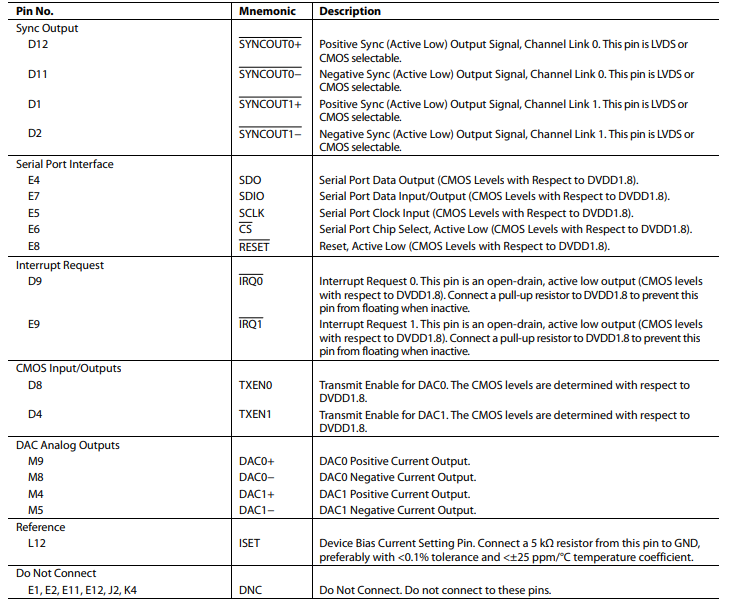

引腳配置和功能描述

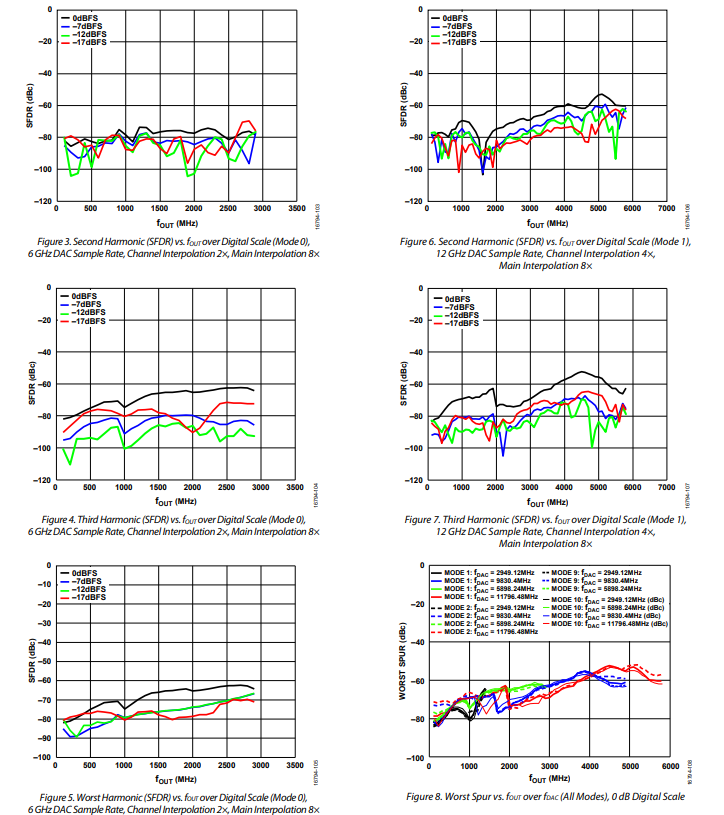

典型性能特征

模擬接口

數(shù)模轉(zhuǎn)換器(DAC)輸入時鐘配置

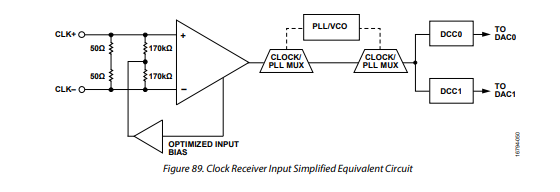

AD9174的數(shù)模轉(zhuǎn)換器采樣時鐘或設(shè)備時鐘(DACCLK)可以通過CLKIN±引腳(引腳H12和J12)直接接收,也可以通過集成在芯片上的鎖相環(huán)/壓控振蕩器(PLL/VCO)產(chǎn)生,該PLL/VCO由同一CLKIN±差分輸入引腳提供的參考時鐘驅(qū)動。DACCLK為AD9174內(nèi)的所有時鐘域提供參考。

AD9174使用一個低抖動差分時鐘接收器,能夠直接連接到差分或單端時鐘源。由于輸入是自偏置的,標稱阻抗為100Ω,建議時鐘源通過CLKIN±引腳交流耦合。通過更高的時鐘輸入電平(更大的擺幅)可以改善相位噪聲性能,但要在推薦的最大限制范圍內(nèi)。因為DACCLK是模擬內(nèi)核(DACx)內(nèi)數(shù)據(jù)的采樣時鐘,所以AD9174模擬輸入引腳上信號的質(zhì)量直接影響DAC的模擬性能。選擇一個具有與目標應(yīng)用要求相符的相位噪聲和雜散特性的時鐘源至關(guān)重要。一般來說,使用PLL/VCO或其他時鐘倍頻器(內(nèi)部或外部)對DAC進行操作,也會使相位噪聲成倍增加。要獲得最佳的相位噪聲性能,通常是使用外部時鐘以所需的DAC時鐘速率運行,并繞過PLL/VCO。

在低相位噪聲不是關(guān)鍵要求的情況下,PLL/VCO為AD9174提供了一種便捷的方式,使其能夠在高達12.4 GHz的DAC時鐘速率下運行,而無需復(fù)雜的多千兆赫茲時鐘解決方案。PLL參考頻率(通常在CLKIN±處)的量級可以比所需的DACCLK速率低幾個數(shù)量級。PLL為下游的VCO生成一個控制電壓,實際上是將參考時鐘倍頻到所需的DACCLK頻率。

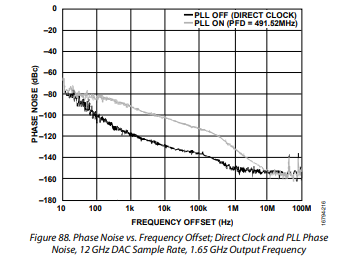

圖88展示了AD9174由直接時鐘驅(qū)動時的典型相位噪聲性能(默認啟用校正),并與片上PLL/VCO產(chǎn)生的相位噪聲進行了對比。

-

頻率合成器

+關(guān)注

關(guān)注

5文章

297瀏覽量

32880 -

dac

+關(guān)注

關(guān)注

44文章

2415瀏覽量

194152 -

數(shù)模轉(zhuǎn)換器

+關(guān)注

關(guān)注

14文章

1070瀏覽量

84262

發(fā)布評論請先 登錄

3.5 GSPS直接數(shù)字頻率合成器AD9914的優(yōu)勢特性

采用AD9914 3.5 GSPS直接數(shù)字頻率合成器的AD9914/PCBZ評估板

AD9914BCPZ直接數(shù)字頻率合成器

AD9914BCPZ直接數(shù)字頻率合成器

AD9914BCPZ直接數(shù)字頻率合成器

基于FPGA的直接數(shù)字頻率合成器的設(shè)計

AD9915: 2.5 GSPS直接數(shù)字頻率合成器,內(nèi)置12位數(shù)模轉(zhuǎn)換器數(shù)據(jù)手冊

AD9914:3.5 GSPS直接數(shù)字頻率合成器,內(nèi)置12位數(shù)模轉(zhuǎn)換器數(shù)據(jù)手冊

AD9910: 1 GSPS、14位、3.3 V CMOS直接數(shù)字頻率合成器

AD9164:16位、12 GSPS、RF DAC和直接數(shù)字合成器數(shù)據(jù)表

AD9174:雙16位12.6 GSPS RF DAC和直接數(shù)字合成器數(shù)據(jù)表

UG-475:評估采用14位DAC的AD9912 1 GSPS直接數(shù)字頻率合成器

1 GSPS直接數(shù)字頻率合成器AD9858概述

AD9164 16位、12 GSPS、RF DAC和直接數(shù)字頻率合成器技術(shù)手冊

AD9174雙路、16位、12.6 GSPS RF DAC和直接數(shù)字頻率合成器技術(shù)手冊

AD9174雙路、16位、12.6 GSPS RF DAC和直接數(shù)字頻率合成器技術(shù)手冊

評論