01概 述

8051 IP調試器是一種對基于8051指令系統的IP核進行調試的軟硬件結合工具,需要與集成開發環境(IDE)結合使用。

調試器可加速開發者查找和修復程序錯誤,允許開發者單步執行代碼、設置斷點、查看變量和寄存器的值,以及修改內存內容,分析程序執行流程,提高MCU程序開發效率。

晶華微8051 IP核芯片,是基于S8051XC3 IP核進行設計的,因此本技術文章基于S8051XC3 IP核進行調試器原理講解。

下圖是晶華微基于8051指令系統的IP核,設計的SD8Link調試器實物圖,后續將以SD8Link調試器展開講解8051 IP調試器設計方案。

圖1 SD8Link調試器實物圖

02SD8Link調試器原理

首先調試器接收IDE編譯生成的可執行文件(例如:HEX文件),通過JTAG和OneWire接口,將程序燒錄到8051IP核的Flash空間內或是RAM空間。待IDE進入DEBUG模式后,可進行復位、全速、單步、停止、設置斷點、查看變量和寄存器的值,進而調試程序,分析程序執行流程,查找和修改程序錯誤。

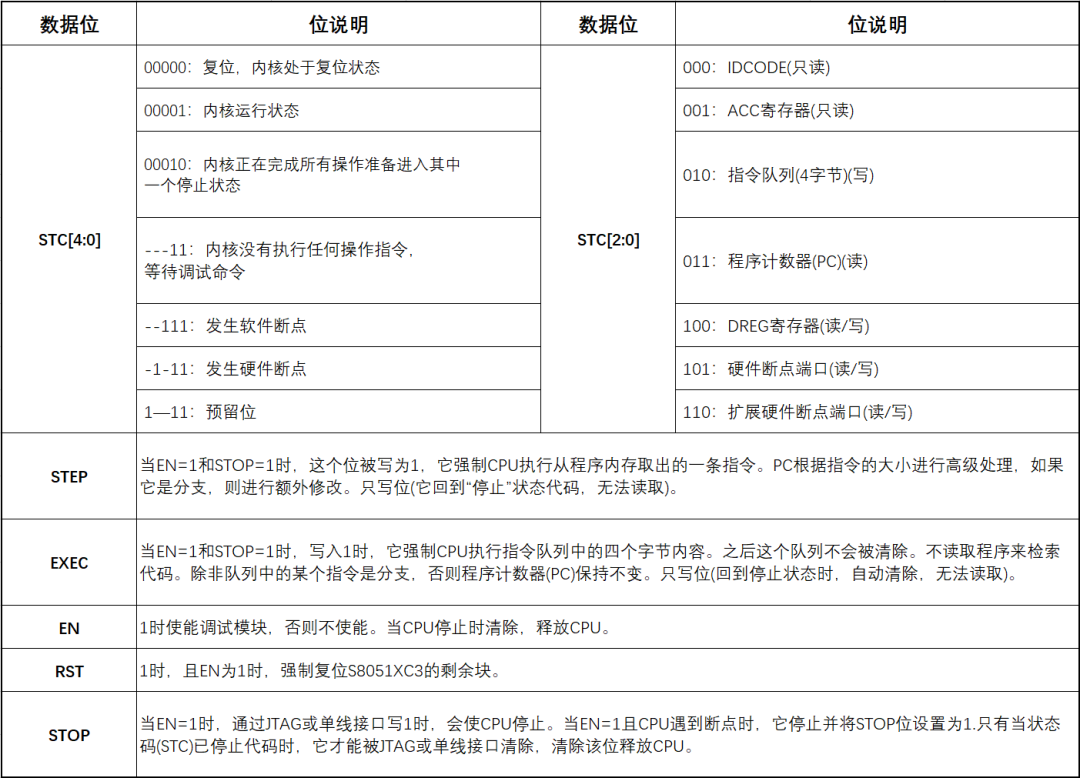

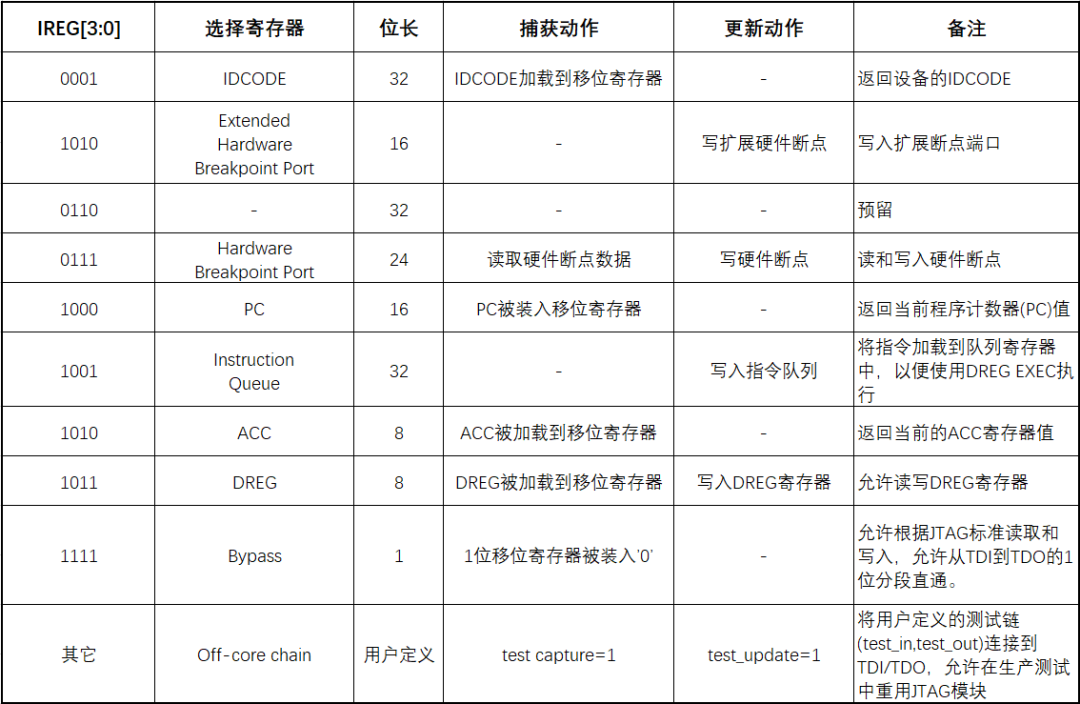

調試模塊的功能由數據寄存器(DREG)、指令寄存器(IREG)、硬件斷點寄存器(HWBP)等寄存器控制,這些寄存器可以通過JTAG或OneWire接口進行讀寫。

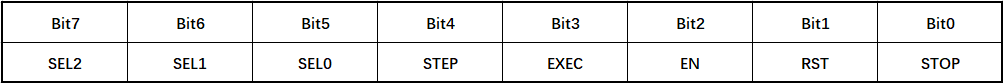

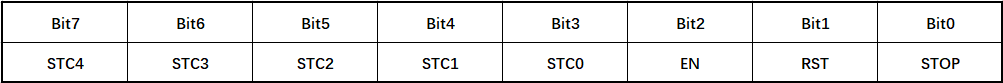

數據寄存器(DREG),由讀寫2個寄存器組成,對CPU狀態進行讀寫控制

寫

讀

數據寄存器(DREG)數據位說明

表1 DREG數據位說明

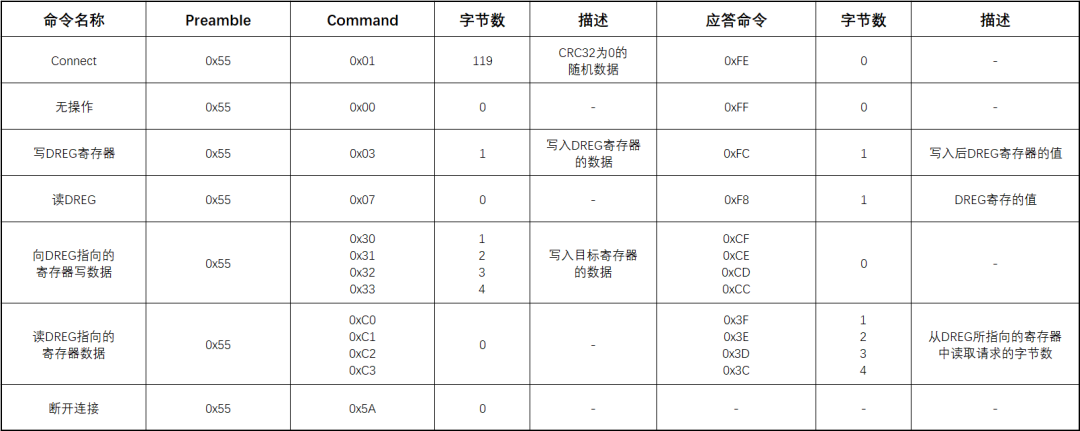

指令寄存器(IREG),JTAG和OneWire接口對應不同的指令

表2 JTAG指令寄存器

表3 OneWire接口命令

SD8Link采用JTAG與芯片通訊說明

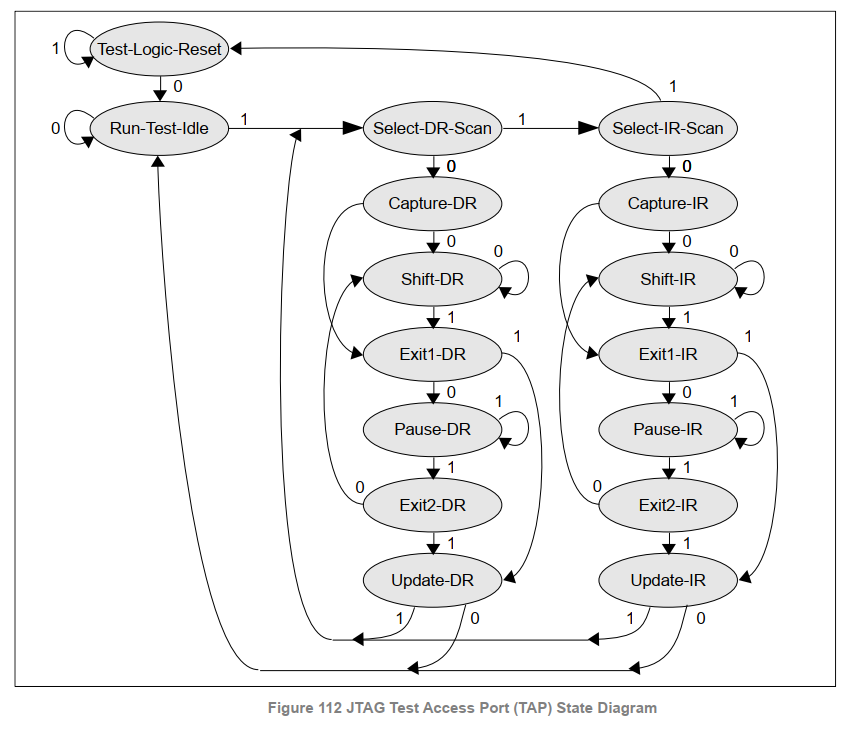

芯片JTAG采用TMS/TCK/TDI/TDO四線進行通訊,TAP狀態機控制流程如下圖所示,以“TMS”信號作為輸入控制。

圖2 JTAG狀態機控制流程

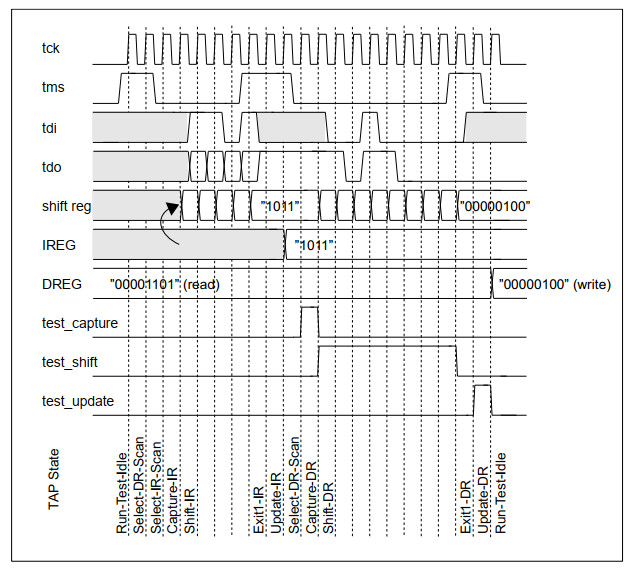

上圖2右半部分流程用于選擇“表1 JTAG指令寄存器”的寄存器,作為左半部分流程操作的寄存器,例如下圖是寫DREG寄存器時的完整時序圖。

圖3 JTAG寫DREG寄存器時序圖

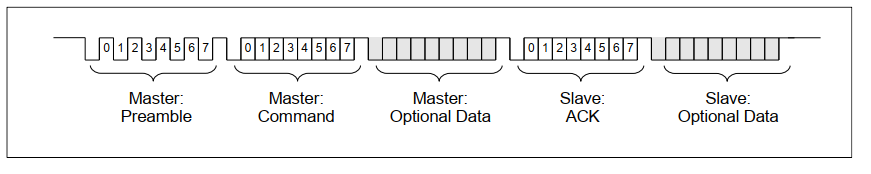

SD8Link采用OneWire與芯片通訊說明

根據“表2 OneWire接口命令”,按照下圖傳輸一幀數據的一般數據格式進行讀寫操作,對于主機數據或從機應答數據字節長度為0的操作,對應數據格式中不存在Data數據。

圖4 OneWire數據格式

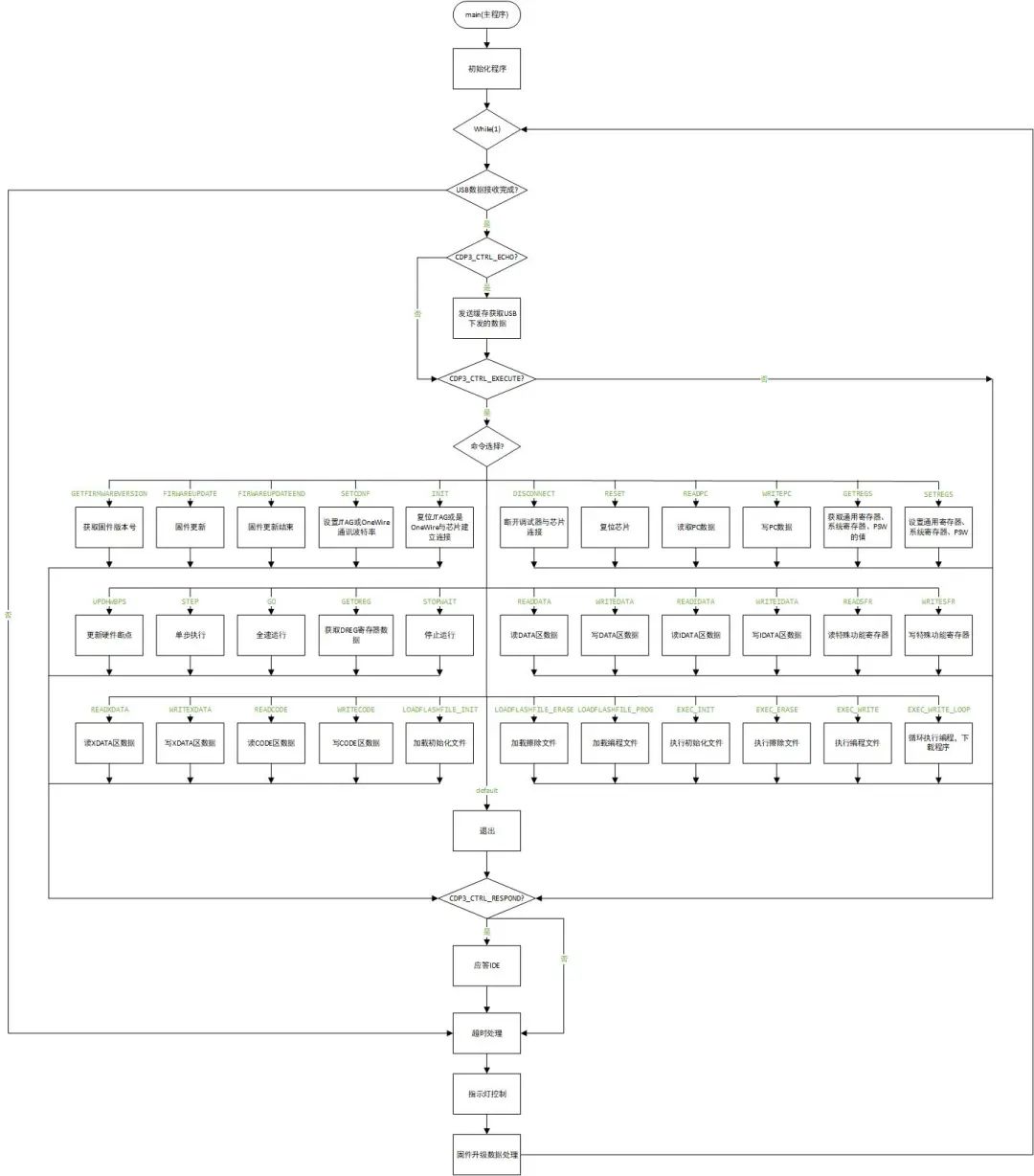

03SD8Link調試器程序流程圖

圖5 調試器程序流程圖

04SD8Link調試器性能特點

支持多種芯片調試,例如SD81F233、SD82F354、SD82F466、SD82P253等等;

支持使用Keil實現固件在線升級功能,可擴展兼容更多8051 IP設計的IC;

支持JTAG和OneWire(單線異步)兩種接口模式,方便客戶設計選擇使用;

支持設置斷點、單步執行、變量查看、存儲器讀寫等多種調試功能;

支持調試器提供3.3V電源輸出,500mA帶負載能力。

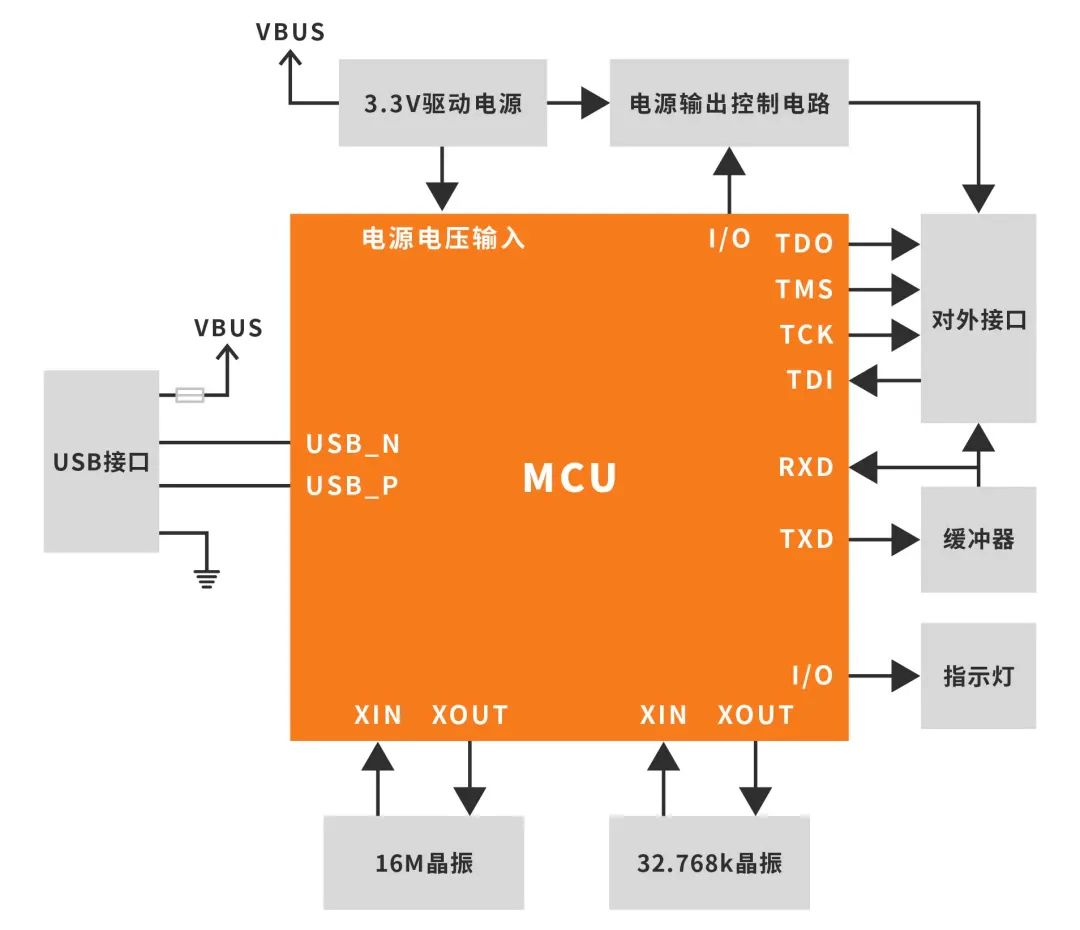

05SD8Link調試器電路框圖

圖6 調試器電路框圖

-

寄存器

+關注

關注

31文章

5434瀏覽量

124583 -

指令系統

+關注

關注

1文章

82瀏覽量

15941 -

IP核

+關注

關注

4文章

338瀏覽量

50830 -

調試器

+關注

關注

1文章

313瀏覽量

24331 -

8051指令

+關注

關注

0文章

2瀏覽量

5989

原文標題:技術分享 | 基于8051 IP調試器設計方案

文章出處:【微信號:杭州晶華微,微信公眾號:杭州晶華微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于SoPC的通用在線調試器設計

基于DCC和JTAG的ARM硬件仿真調試器的研究與實現

基于CodeWarrior集成開發環境的調試器原理

基于SOPC的M8051嵌入式調試器設計

gdb調試器解析

基于SOPC的M8051調試器設計及系統測試

Microchip調試器(MDB)用戶指南

邏輯調試器link-logic

Microchip調試器(MDB)用戶指南

應用單片機開發的ST LINK調試器設計制作

基于8051 IP調試器設計方案

基于8051 IP調試器設計方案

評論