高層數(shù) PCB 的布線策略豐富多樣,具體取決于 PCB 的功能。這類電路板可能涉及多種不同類型的信號,從低速數(shù)字接口到具有不同信號完整性要求的多個高速數(shù)字接口。從布線規(guī)劃和為各接口分配信號層的角度來看,這無疑是一項極具挑戰(zhàn)性的任務(wù)。

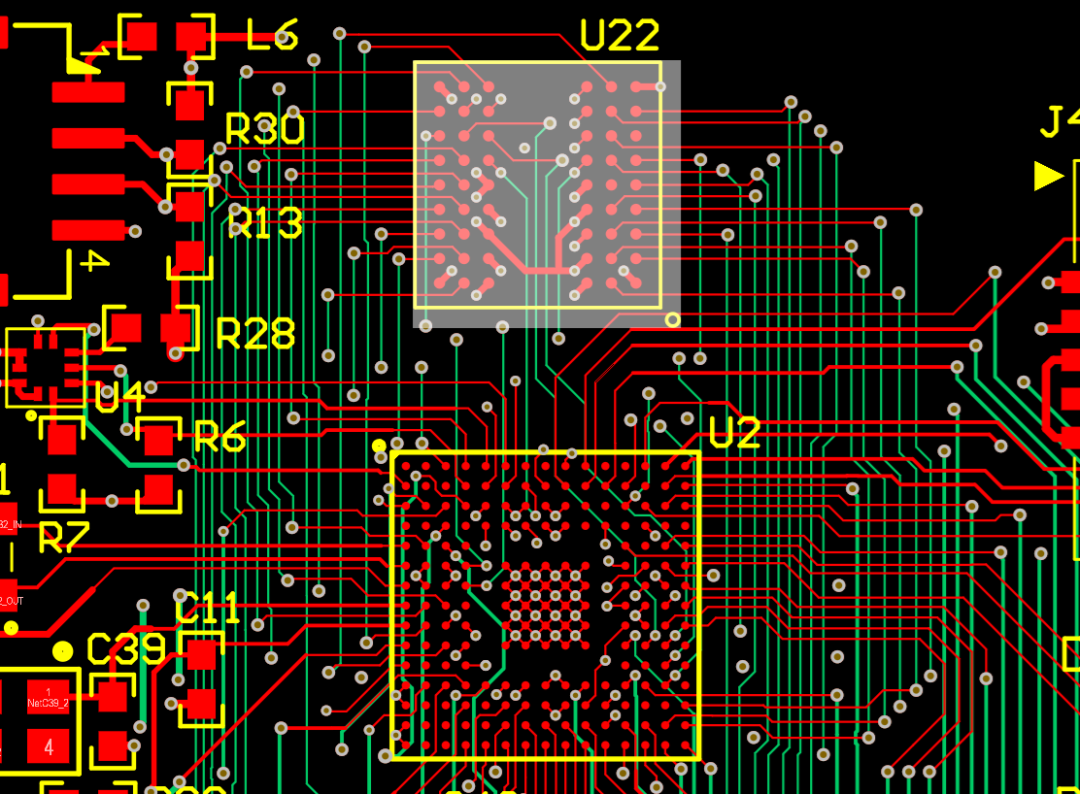

提及高層數(shù) PCB 的布線策略,就不得不談到眾多BGA封裝的引腳布局設(shè)計。高引腳數(shù) BGA 通常包含多種不同的數(shù)字接口,尤其是當(dāng)元件為典型的微處理器或FPGA時。這是導(dǎo)致 PCB 層數(shù)增加的最常見因素之一。

由于高層數(shù)設(shè)計中往往同時面臨多個挑戰(zhàn),本文將逐一解析這些挑戰(zhàn),并分享能夠成功實現(xiàn)高層數(shù) PCB 布線的實用策略。

是什么導(dǎo)致 PCB 層數(shù)增加?

如引言所述,導(dǎo)致 PCB 層數(shù)變高的最常見因素是大型BGA元件的存在。這類元件在器件底部具有高密度引腳,為使信號到達(dá)每個引腳,需要更多的線路層。由于這些元件多為專用ASIC、微處理器或FPGA,它們還集成了大量對信號完整性和布線要求各異的數(shù)字接口,以及眾多電源和接地引腳。

許多設(shè)計師都能熟悉估算 BGA 引腳全連接所需層數(shù)的簡單公式。當(dāng) BGA 的焊球間距足夠大(允許在引腳間布線)時,每層信號層可容納兩行 BGA 引腳:

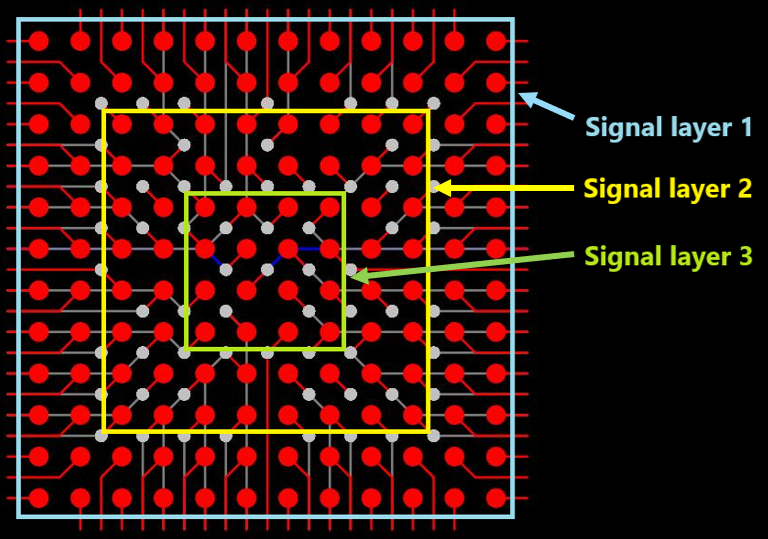

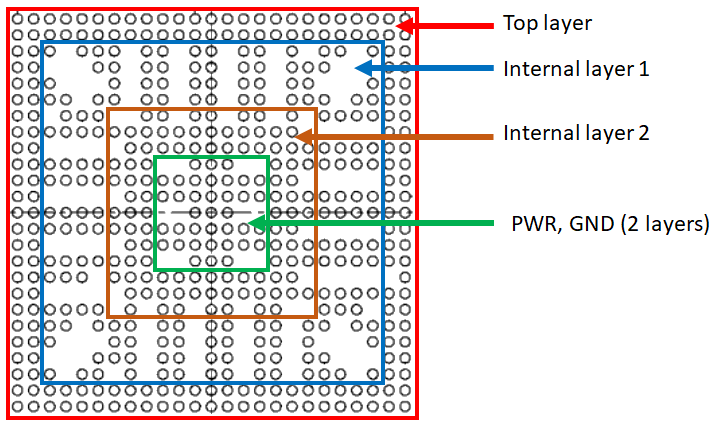

對于粗間距 BGA 封裝(焊球間可布置走線),每層可布線 2 行 / 列信號。 部分 BGA 封裝的焊盤布局較為復(fù)雜,內(nèi)層行可能存在缺失的焊球(如下圖示例),此類 BGA 的層數(shù)計算通常不同于上述標(biāo)準(zhǔn) BGA。

當(dāng)元件引腳間距極細(xì)(BGA 焊盤間無法布線)時,所需層數(shù)需翻倍;若大量引腳為電源和接地引腳,層數(shù)則會減少。此外,大量四方扁平封裝(Quad 封裝)也可能導(dǎo)致高層數(shù)需求,但其引腳數(shù)通常遠(yuǎn)低于中等尺寸 BGA(高端 Quad 封裝約有幾百個引腳,而中等 BGA 引腳數(shù)更高)。

四大核心布線策略

策略 1:“無策略”

“無策略” 策略是迄今為止最簡單的方法,其核心是在確保可布線性的同時盡量減少層數(shù)。具體實施方式包括:選擇所需層數(shù)并通過標(biāo)準(zhǔn)扇出方法從 BGA 布線、采用固定層數(shù)緊湊排布所有走線,或自由布線并根據(jù)需求添加新信號層。該策略適用于以下場景:

無需按阻抗規(guī)格將不同信號分隔到不同層

所有接口均無阻抗要求(如串行外設(shè)接口 SPI)

所有接口的阻抗要求一致

有阻抗規(guī)格要求的接口數(shù)量極少(如 1-2 個)

盡管采用這種策略的布線可能顯得不夠規(guī)整,但通過弱化信號完整性要求以換取可布線性,能有效控制層數(shù),避免其層數(shù)高于其他策略。

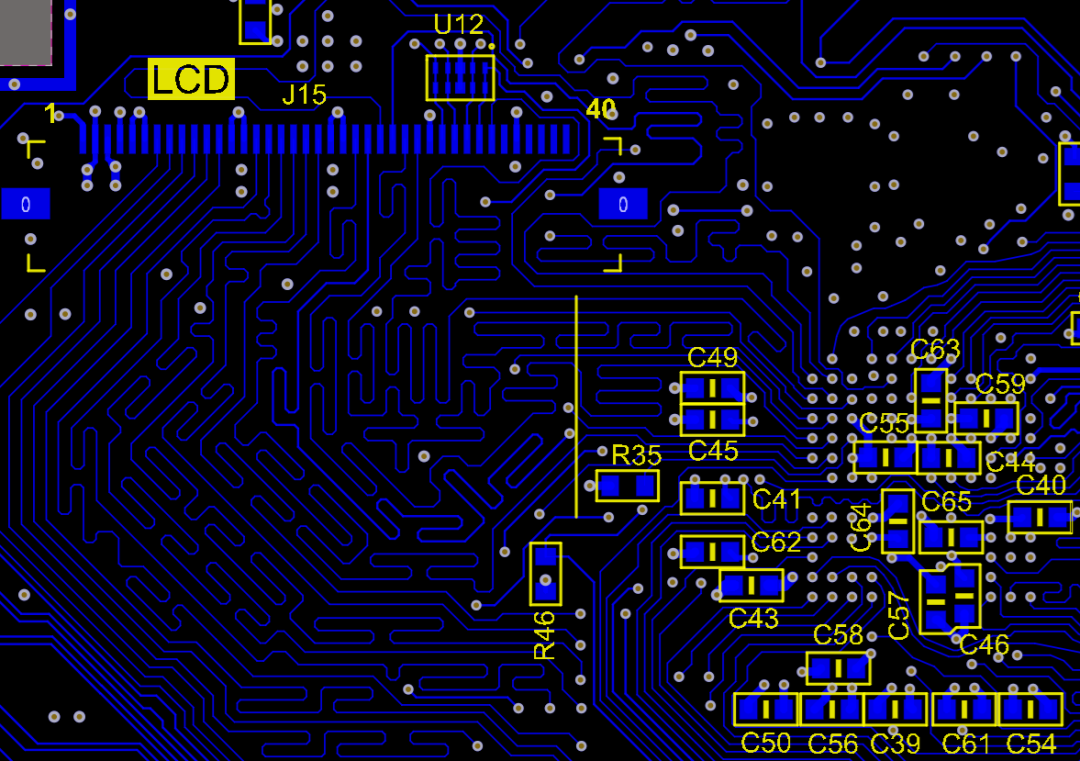

示例:該并行接口從 BGA(右下角)起始布線,連接至外接 LCD 模塊(左上角)。

策略 2:按接口優(yōu)先級分配層

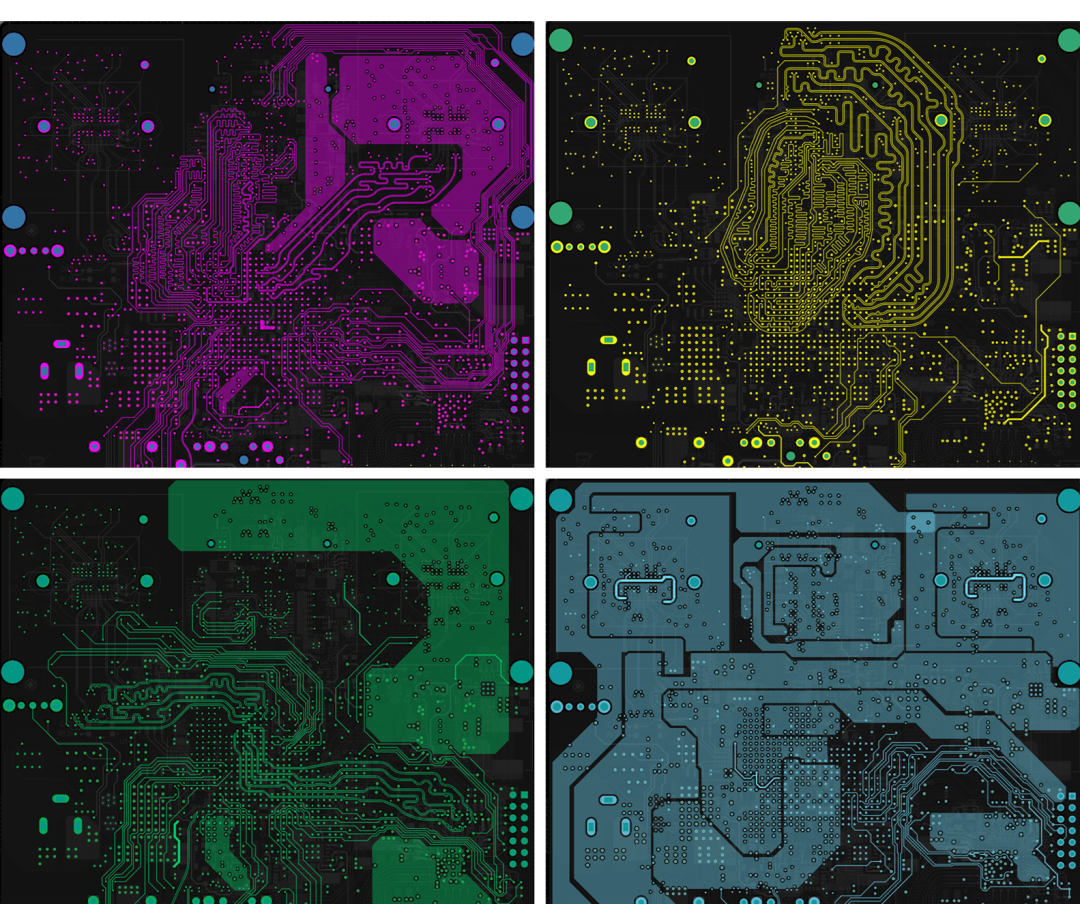

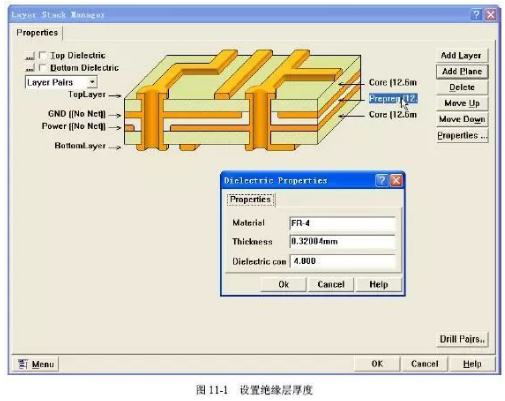

在此策略中,特定的阻抗受控接口會被分配專屬的信號層,并且主要在這些層內(nèi)進(jìn)行布線。制造商隨后采用阻抗控制方法,確定構(gòu)建電路板層疊結(jié)構(gòu)時使用的電氣特性。當(dāng)存在多個需要阻抗控制且可能具有不同目標(biāo)阻抗值的高速接口時,可采用這種策略。對于部分差分接口,盡管其標(biāo)稱阻抗目標(biāo)相同,但帶寬需求可能不同,這就需要為不同接口設(shè)置不同的線寬和間距。 在下方示例圖中,展示了 16 層疊結(jié)構(gòu)中多個數(shù)字接口的分層分配情況,涉及的接口包括:

DDR4

CSI-2

1 Gbps LVDS

10 Gbps 以太網(wǎng)

具體可見下方圖表中這些接口如何被分配到不同層中。

高層數(shù) PCB 中多數(shù)字接口的高速布線示例 您會注意到這些層上存在一些空白區(qū)域。需要明確的是,這種分層策略的主要目標(biāo)是讓制造商更容易實現(xiàn)阻抗規(guī)格定義。當(dāng)每層僅對應(yīng)一種阻抗規(guī)格時,制造商就能更便捷地生產(chǎn)出滿足每個接口阻抗目標(biāo)的層疊結(jié)構(gòu)。 該策略的缺點在于可能會導(dǎo)致層數(shù)增加,且部分層會出現(xiàn)未利用的空白區(qū)域。若有需要,您可以用額外的地線或銅電源鋪銅來填充一些空白區(qū)域。在某些設(shè)計中,我傾向于將這些區(qū)域用于布置電源鋪銅,這甚至可能讓我省去一個專用電源層。此外,您仍然可以使用這些阻抗控制層來傳輸?shù)退倩蚺渲眯盘枺灰鼈儾灰獢D得太靠近高速走線即可。

策略 3:高速層與低速層分離

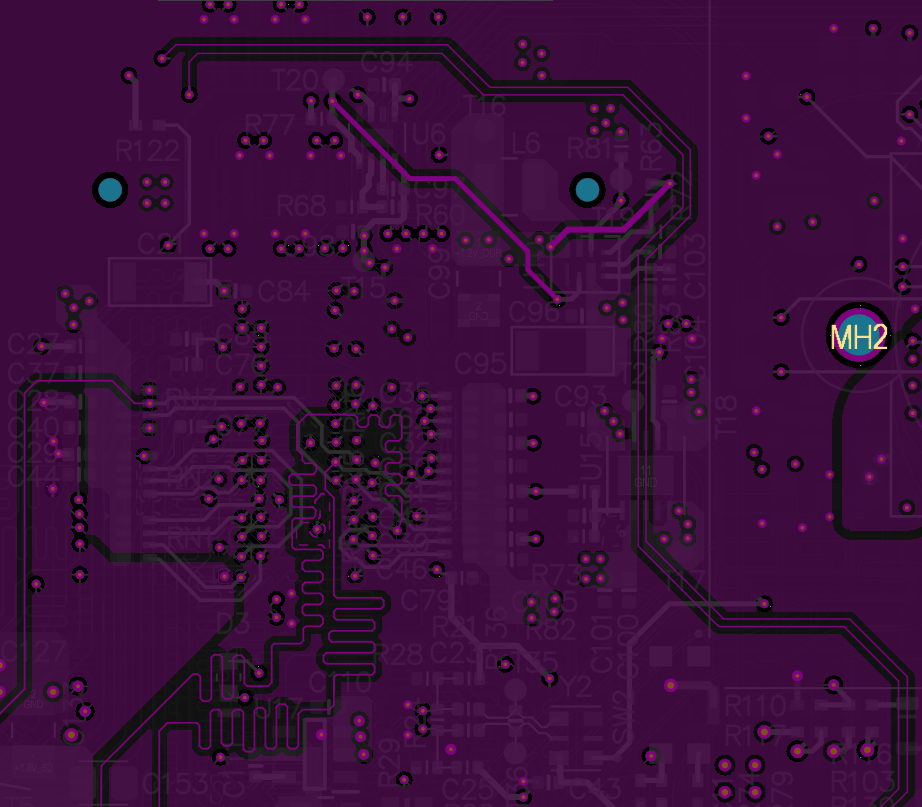

此策略適用于需要阻抗控制的接口數(shù)量較少,或所有阻抗受控接口具有相同阻抗要求的場景。通過將信號分隔到專用的高速層和低速層,可實現(xiàn)更清晰的分層設(shè)計。這類似于在六層板中設(shè)置四個信號層,將低速信號層相鄰放置的做法。 這種策略適合采用正交布線(相鄰層信號走向垂直),尤其當(dāng)?shù)退傩盘柗植荚谙噜弻訒r效果更佳。例如,下方示例中的布線在兩個不同層上的元件之間采用正交走向:

這些輸入 / 輸出(I/O)屬于同步SDRAM接口,通過正交布線方法可輕松連接至存儲芯片。 由于低速信號占比比較高,此策略面臨的信號完整性挑戰(zhàn)較少,有助于維持合理的層數(shù),避免因過度分層導(dǎo)致設(shè)計復(fù)雜。

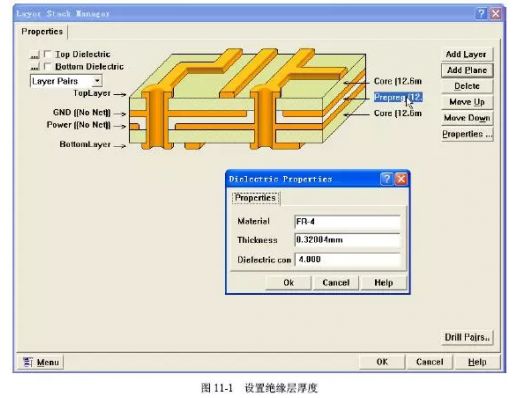

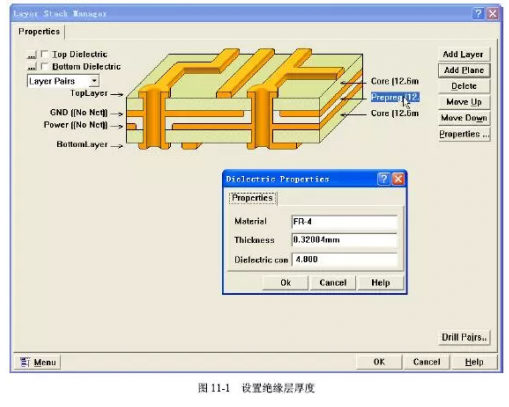

策略 4:電源與信號共層設(shè)計

在高層數(shù)電路板設(shè)計中,我經(jīng)常采用的另一種布線策略是將部分信號與電源鋪銅整合到同一層。 層數(shù)增加的常見原因不僅是需要布線的信號或接口數(shù)量龐大,多個電源通路和電源供應(yīng)也會導(dǎo)致層數(shù)上升。新手設(shè)計師可能認(rèn)為每個電源通路都需要一個專用電源層,但這會導(dǎo)致創(chuàng)建過多層數(shù),使用不必要的銅箔。更優(yōu)的策略是將電源通路以多邊形鋪銅形式繪制在層上。 在繪制了電源鋪銅的層中,允許布置信號走線,尤其是低速信號或配置信號。如下圖所示的示例布線:

只要保持足夠間距,在電源層布線是可行的。 這種方法可與策略 2 結(jié)合使用,利用未分配給接地層的剩余層來布置低速信號,而高速信號仍可根據(jù)需要在策略 2 下?lián)碛袑賹印Mㄟ^省去專用電源層和低速信號層,有效避免層數(shù)過高。 此外,含電源鋪銅的層仍可布置阻抗受控走線,但需執(zhí)行間距規(guī)則以防止過大電容影響走線阻抗。這與在共面接地層布線的原理一致:避免使用全局電氣間距規(guī)則,而是創(chuàng)建網(wǎng)絡(luò)和層專屬的間距規(guī)則。在 Altium Designer 中,可通過自定義查詢(利用 InNet/InNetClass 和 InLayer 條件)設(shè)置此類規(guī)則。

無論是制造電力電子設(shè)備,還是應(yīng)對跨領(lǐng)域協(xié)作挑戰(zhàn),Altium Designer 的全套 PCB 設(shè)計功能與 Altium 365 平臺都能輕松滿足需求,支持設(shè)計數(shù)據(jù)無縫共享與生產(chǎn)流程高效推進(jìn)。這僅僅是 Altium 解決方案的一小部分,立即免費試用 Altium Designer + Altium 365,探索高層數(shù) PCB 設(shè)計的無限可能!

關(guān)于Altium

Altium有限公司隸屬于瑞薩集團(tuán),總部位于美國加利福尼亞州圣迭戈,是一家致力于加速電子創(chuàng)新的全球軟件公司。Altium提供數(shù)字解決方案,以最大限度提高電子設(shè)計的生產(chǎn)力,連接整個設(shè)計過程中的所有利益相關(guān)者,提供對元器件資源和信息的無縫訪問,并管理整個電子產(chǎn)品生命周期。Altium生態(tài)系統(tǒng)加速了各行業(yè)及各規(guī)模企業(yè)的電子產(chǎn)品實現(xiàn)進(jìn)程。

-

pcb

+關(guān)注

關(guān)注

4368文章

23489瀏覽量

409675 -

電路板

+關(guān)注

關(guān)注

140文章

5133瀏覽量

102623 -

altium

+關(guān)注

關(guān)注

48文章

979瀏覽量

120209 -

BGA

+關(guān)注

關(guān)注

5文章

572瀏覽量

48649 -

Designer

+關(guān)注

關(guān)注

0文章

134瀏覽量

36586

原文標(biāo)題:【技術(shù)博客】高層數(shù)層疊結(jié)構(gòu) PCB 的布線策略

文章出處:【微信號:AltiumChina,微信公眾號:Altium】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

PCB疊層設(shè)計層的排布原則和常用層疊結(jié)構(gòu)

多層PCB板的層疊結(jié)構(gòu)規(guī)則

層PCB板的層疊結(jié)構(gòu)

轉(zhuǎn): PCB疊層設(shè)計層的排布原則和常用層疊結(jié)構(gòu)

PCB疊層設(shè)計層的排布原則和常用層疊結(jié)構(gòu)

PCB原創(chuàng)|高速PCB設(shè)計軟件層疊結(jié)構(gòu)設(shè)計的建議

原創(chuàng)|高速PCB設(shè)計中層疊設(shè)計的考慮因素

PCB疊層設(shè)計層的排布原則和常用層疊結(jié)構(gòu)

PCB層疊結(jié)構(gòu)設(shè)計的PCB層數(shù)預(yù)估和可生產(chǎn)性

多層PCB板的層疊結(jié)構(gòu)以及疊加原則解析

PCB板層疊結(jié)構(gòu)的選擇以及疊加原則解析

多層PCB板的層疊的設(shè)計步驟解析

高層數(shù)層疊結(jié)構(gòu)PCB的布線策略

高層數(shù)層疊結(jié)構(gòu)PCB的布線策略

評論