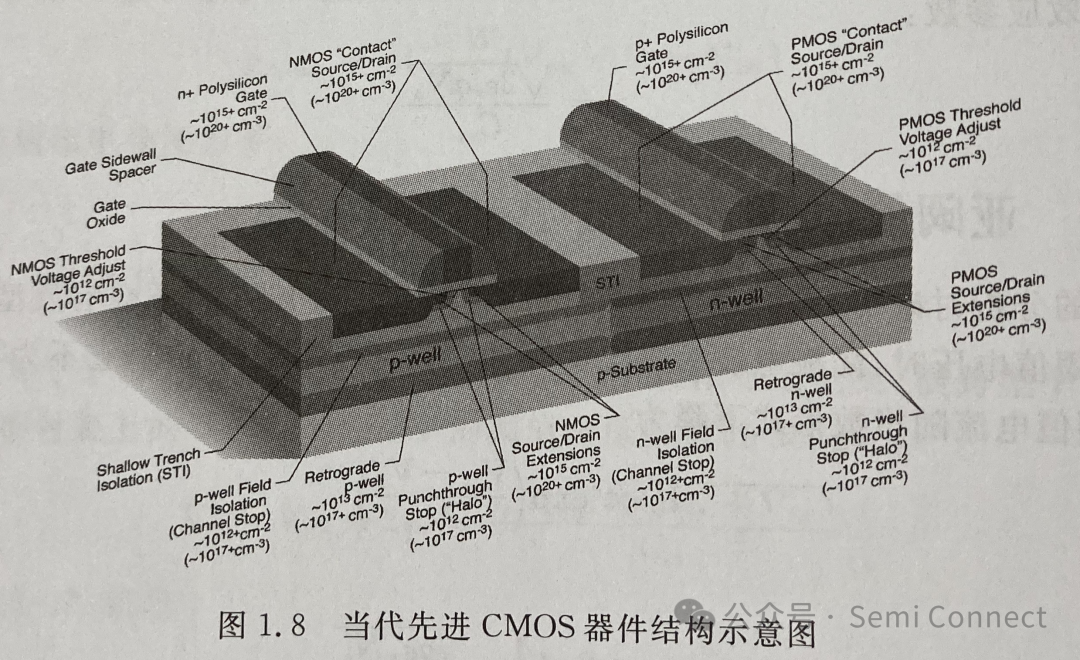

一對N溝道和P溝道 MOS 管以推挽形式工作,構成互補的金屬氧化物半導體器件(Complementary Metal-Oxide-Semiconductor, CMOS)。其組成的反相器基本電路單元所實現一定邏輯功能的集成電路稱為CMOS 電路。其特點是:①靜態功耗低,每門功耗為納瓦級;②邏輯擺幅大,近似等于電源電壓;③抗干擾能力強,直流噪聲容限達邏輯擺幅的35%左右;④可在較廣泛的電源電壓范圍內工作,便于與其他電路接口;⑤速度快,門延遲時間達納秒級;⑥在模擬電路中應用,其性能比 NMOS 電路好;⑦與 NMOS 電路相比,集成度稍低;⑧有“自鎖效應”,影響電路正常工作。圖1.8為當代先進CMOS 器件結構示意圖。

MOS 器件不斷地按比例縮小,通常伴隨柵極氧化層的厚度的減薄,發生強反型時,溝道中的電阻將進一步降低,MOS器件速度將進一步提升。理論上MOSFET 的柵極應該盡可能選擇導電性良好的導體,重摻雜多晶硅普遍用于制作MOSFET 的柵極,但這并非完美的選擇。采用多晶硅柵極的理由如下:MOSFET 的閾值電壓主要由柵極與溝道材料的功函數之間的差異來決定,因為多晶硅本質上是半導體,所以可以通過摻雜不同極性及濃度的雜質來改變其功函數。更重要的是,因為多晶硅和其底下作為溝道的硅之間禁帶寬度相同,因此在降低 PMOS或NMOS的閾值電壓時,可以通過直接調整多晶硅的功函數來達成需求。反過來說,金屬材料的功函數并不像半導體那么易于改變,如此一來要降低 MOSFET的閾值電壓就變得比較困難。而且如果想要同時降低PMOS 和 NMOS 的閾值電壓,將需要兩種不同的金屬分別做其柵極材料,增加了工藝的復雜性;經過多年的研究,已經證實硅-二氧化硅界面兩種材料之間的缺陷相對而言比較少。反之,金屬-絕緣體界面的缺陷多,容易在兩者之間形成很多表面能階,大幅影響器件的性能;多晶硅的熔點比大多數的金屬高,而在現代的半導體工藝中,習慣在高溫下沉積柵極材料以增進器件性能。金屬的熔點較低,將會影響工藝所能使用的溫度上限。

不過雖然多晶硅在過去的二十多年里已成為制造MOSFET 柵極的標準,但也有若干缺點使得工業界在先進CMOS 器件產品中使用高介電常數的介質和金屬柵極(High-kMetal Gate,HKMG),這些缺點如下:多晶硅導電性不如金屬,限制了信號傳遞的速度。雖然可以利用摻雜的方式改善其導電性,但效果仍然有限。有些熔點比較高的金屬材料如:鎢(Tungsten)、鈦(Titanium)、鈷(Cobalt)或鎳(Nickel)被用來和多晶硅制成合金。這類混合材料通常稱為金屬硅化物(silicide)。加上了金屬硅化物的多晶硅柵極導電特性顯著提高,而且又能夠耐受高溫工藝。此外因為金屬硅化物的位置是在柵極表面,離溝道區較遠,所以也不會對MOSFET的閾值電壓造成太大影響。在柵極、源極與漏極都鍍上金屬硅化物的工藝稱為“自我對準金屬硅化物工藝”(Self-Aligned Silicide),通常簡稱 salicide 工藝。當 MOSFET 的器件尺寸縮得非常小、柵極氧化層也變得非常薄時,例如,最新工藝可以把氧化層厚度縮小到1nm 左右,一種過去沒有發現的稱之“多晶硅耗盡”現象也隨之產生。當MOSFET 的反型層形成時,有多晶硅耗盡現象的MOSFET柵極多晶硅靠近氧化層處,會出現一個耗盡層,無形中增加了柵氧化層厚度,影響 MOSFET 器件性能。要解決這種問題,一種解決方案是將多晶硅完全的合金化,稱為 FUSI(FUlly-Sllicide Polysilicon Gate)工藝。金屬柵極是另一種最好的方案,可行的材料包括鉭(Tantalum)、鎢、氮化鈕(TantalumNitride),或是氮化鈦(Titalium Nitride)再加上鋁或鎢。這些金屬柵極通常和高介電常數物質形成的氧化層一起構成 MOS電容。

在過去的半個多世紀中,以CMOS 技術為基礎的集成電路技術一直遵循“摩爾定律”,即通過縮小器件的特征尺寸來提高芯片的工作速度、增加集成度以及降低成本,取得了巨大的經濟效益與科學技術的重大發展,推動了人類文明的進步,被譽人類歷史上發展最快的技術之一。伴隨 MOS器件特征尺寸按比例不斷縮小,源與漏之間的距離也越來越短,溝道不僅受柵極電場,同時也受到漏極電場的影響,這樣一來柵極對溝道的控制能力變差,柵極電壓夾斷溝道的難度也越來越大,如此便容易發生亞閥值漏電(Sub-threshold leakage)現象,形成短溝道效應(Short-Channel Effects,SCE)。這樣會導致晶體管性能的嚴重退化,影響其開關效率以及速度。如果短溝道效應得不到有效控制,傳統的平面體硅MOSFET 的尺寸持續按比例縮小將變得越來越困難。集成電路技術發展到當今20nm 技術節點及以下時,在速度、功耗、集成度、可靠性等方面將受到一系列基本物理和工藝技術問題的限制。

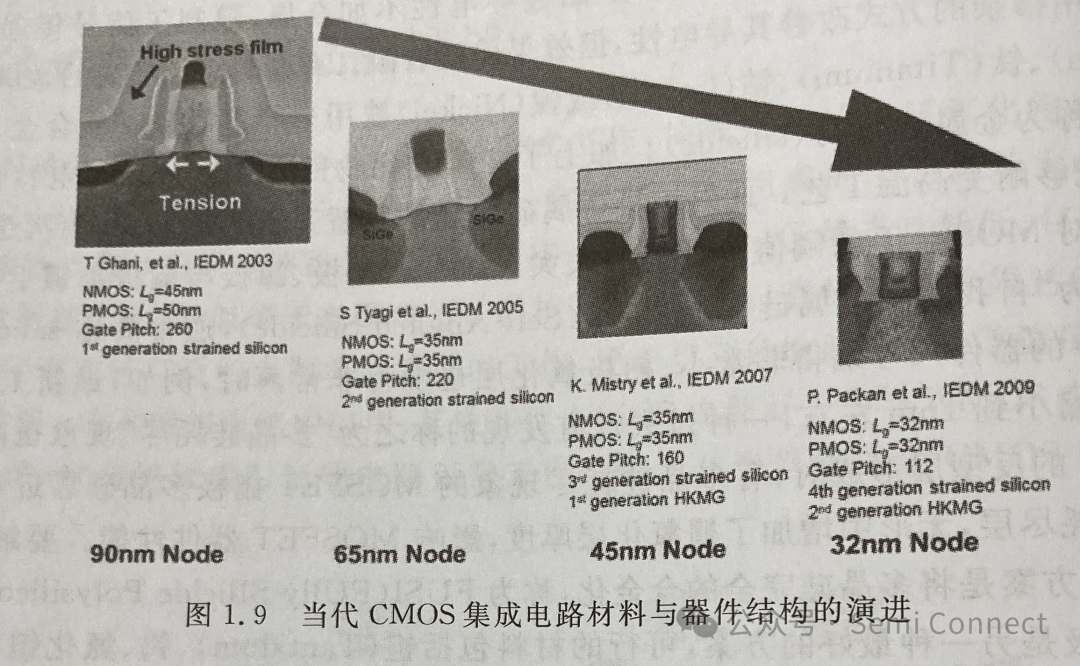

為了克服這些挑戰,人們致力于兩方面的研究:一方面積極研發全新的信息處理技術,以便在CMOS技術的能力范圍之外繼續實現或超越摩爾定律;另一方面積極研究器件新結構、新材料,以便充分挖掘CMOS 技術的潛力,實現CMOS技術沿摩爾定律進一步按比例縮小。比如,在傳統晶體管的工藝設計中采用新的材料,如高k電介質,金屬柵材料以及隱埋應變硅源漏,或者發展替代傳統平面結構的晶體管器件結構。圖1.9給出當代CMOS 集成電路材料與器件結構的演進。

1949年肖克菜(W. B. Shockley)提出少子(少數載流子)在半導體中的注入和遷移的PN 結理論以及基于 PN 結的雙極型晶體管器件結構。1960年,貝爾實驗室的D.Kahng和M. Atalla 發明并首次制作成功金屬-氧化物-半導體場效應晶體管(MOSFET)。MOSFET 的發明也是基于PN 結理論。

在發展替代傳統平面結構的晶體管器件結構方面,一種特器件結構即所謂的鰭式場效應晶體管 FinFET吸引了人們的廣泛關注。這個詞最初被加利福尼亞大學伯克利分校的胡正明教授用來描述一個基于絕緣層上硅(Silicon On Insulator, SOI)襯底的非平面雙柵晶體管器件。由于晶體管的溝道很像魚的鰭,由此稱之為鰭型場效應晶體管。它的發展基礎是 Hitachi 公司的年輕工程師 Hisamoto 于1989年提出的基于體硅襯底,采用局域化絕緣體隔離襯底技術(local SOI)制成的首個三維器件 Delta FET。在傳統晶體管結構中,柵極只能從溝道的一側控制器件的導通與關閉,屬于平面結構。FinFET 器件采用三維立體結構,由其中一個設置于源漏之間的薄鰭狀溝道和類似魚鰭的叉狀柵極組成。柵電極能夠從鰭形硅的兩側及頂部控制溝道,且與鰭形硅溝道垂直,兩個側邊柵電極能夠互相自對準,有效地縮小了有源區在平面上的占有面積,并且很大程度上增加了溝道的有效寬度,使得柵極對溝道電勢控制更加完美,具有非常高的靜電完整性,從而增加了器件的電流驅動能力和器件抑制短溝道效應的能力,并增加了器件的跨導,減小了漏極感應勢壘降低(DrainInduced Barrier Lowering,DIBL)效應和閾值電壓隨溝道長度的變化量等。FinFET 因其優異的性能以及與傳統 CMOS工藝的兼容性,被認為是很有前途的新穎器件,可以使摩爾定律得以延續。

在14nm 節點,由于 FinFET鰭的寬度只有5nm 左右,溝道寬度的變化可能會導致不良的V.以及驅動電流的變化等。采用全包圍柵(Gate-Al-Around Rectangular,GAAR)器件結構是 FinFET器件的自然延伸D4.15。在這種結構中,柵極結構將鰭形溝道全部包裹起來,進一步改善了器件對短溝道效應的控制。然而由于工藝的限制,這些 GAAR型器件的溝道多為長方體形狀,不可避免的銳角效應使得矩形溝道截面中的電場仍然不均勻。更進一步的是采用圓柱體全包圍柵(Gate-All-Around Cylindrical, GAAC)器件結構。在這種結構中,柵極結構將圓柱體溝道全部包裹起來,克服了銳角效應,進一步改善了器件對短溝道效應的控制。由于具備近乎完美的靜電完整性,圓柱體全包圍柵器件備受關注。圖1.10給出CMOS 器件由二維平面結構向三維非平面結構的演進。

2011年初,Intel 公司在其22nm 工藝技術節點上首次推出了商品化的 FinFET 產品Ivy-Bridge。其器件結構與早期 Hisamoto 的Delta FET及其相似,如圖1.10所示,只是省略了局域化襯底絕緣隔離工藝,依舊采用阱隔離技術將溝道與體硅襯底隔離開來。環柵納米線器件因其更優異的靜電完整性和彈道輸運特性,有望取代 FinFET 并應用在10nm以下節點。但由于PN結漏電問題,也將面臨一些挑戰。

-

集成電路

+關注

關注

5423文章

12038瀏覽量

368286 -

CMOS

+關注

關注

58文章

6012瀏覽量

238764 -

半導體

+關注

關注

335文章

28871瀏覽量

237195 -

晶體管

+關注

關注

77文章

10015瀏覽量

141533

原文標題:CMOS 器件面臨的挑戰

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

CMOS器件面臨的挑戰

CMOS器件面臨的挑戰

評論