來源:半導體魚塘

1.10 量子阱場效應晶體管

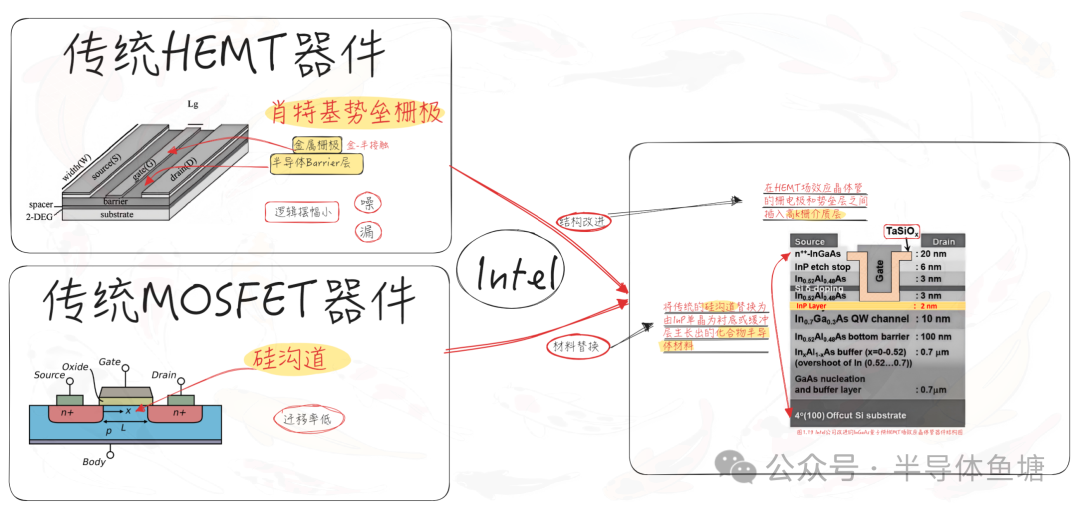

前面的1.8節介紹了HEMT器件,但傳統的HEMT器件雖然具有高遷移率、高頻率等諸多優點,但其命門在于結構中的肖特基勢壘柵極,這種結構的器件很難改善柵極漏電嚴重的問題,存在著邏輯擺幅較小、抗噪聲能力差等問題。

對于傳統的MOSFET器件,雖然因為柵極絕緣層的采用大大抑制了柵極漏流,但是硅溝道較低的電子遷移率也限制了其在超高頻、超高速等領域的應用。

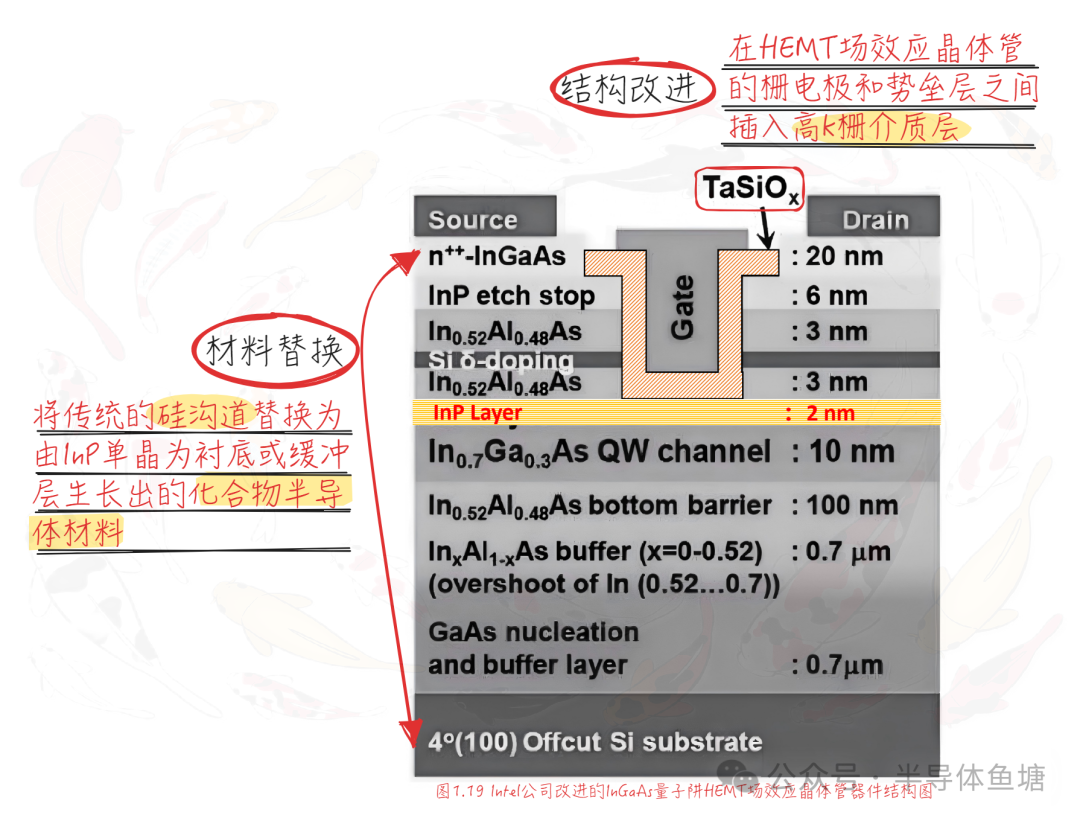

2009年Intel公司在砷化銦鎵(InGaAs)HEMT場效應晶體管的柵電極和勢壘層之間插入了一個高k柵介質層,并給其取名為量子阱場效應晶體管(Quantum Well FET,QW FET)。

如下圖所示,這種量子阱場效應晶體管主要的特點是采用了InP基半導體和具有高k的柵介質層。這里可以看出,Intel采用的襯底還是硅晶圓,然后在上面外延生長不同的化合物材料。

InP基半導體材料是以InP單晶為襯底或緩沖層而生長出的化合物半導體材料, 包括InGaAs、InAlAs、InGaAsP以及GaAsSb等材料。

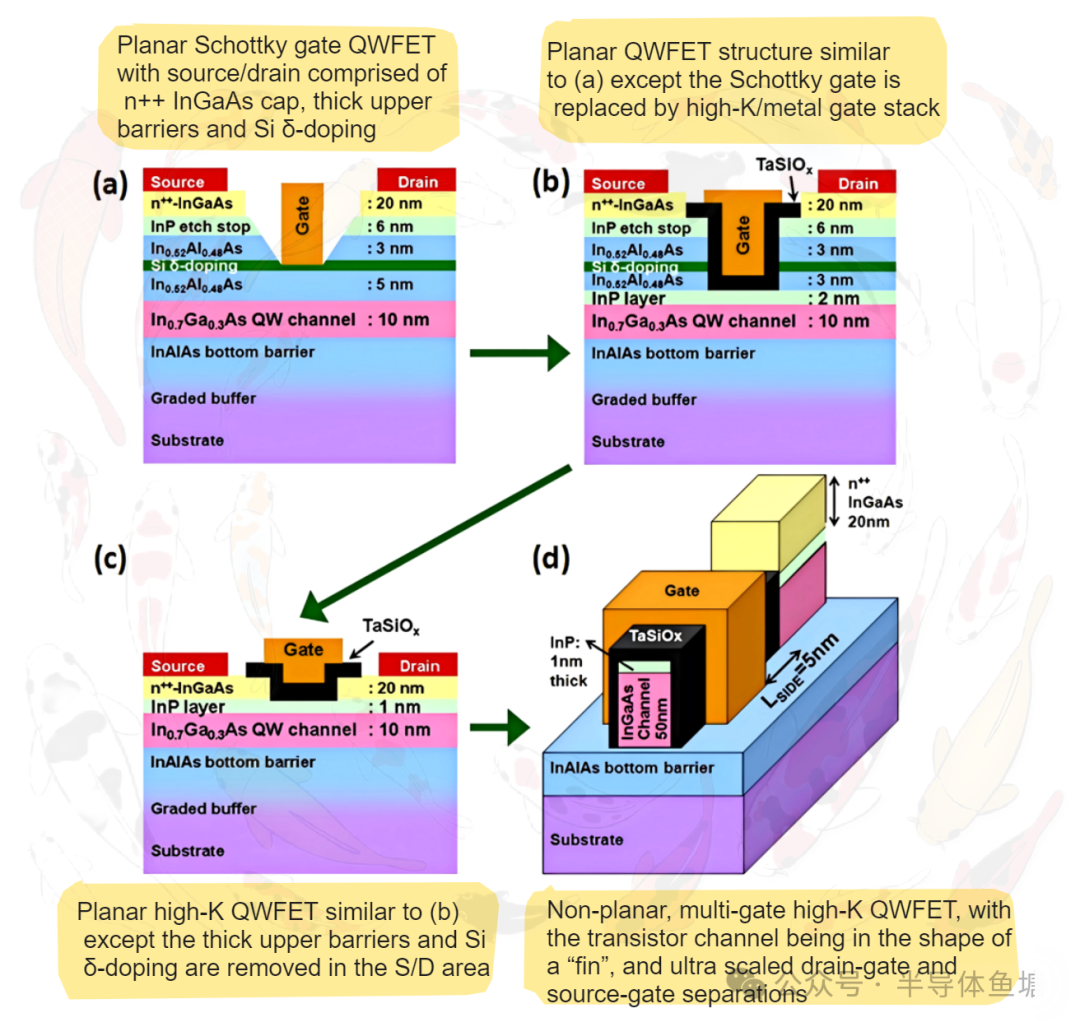

如下為Intel公司研究量子阱場效應晶體管的技術演進圖。[Non-Planar, Multi-Gate InGaAs Quantum Well Field Effect Transistors with High-K Gate Dielectric and Ultra-Scaled Gate-to-Drain/Gate-to-Source Separation for Low Power Logic Applications]

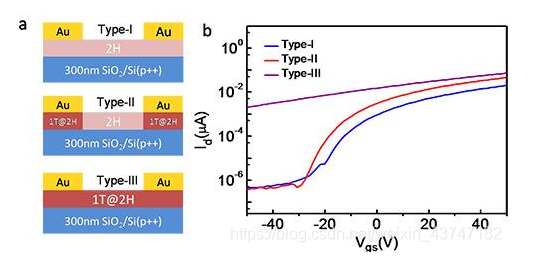

從上圖可以看出InGaAs量子阱場效應晶體管(QWFET)從平面到非平面多柵極架構的演變:

(a)平面肖特基柵QWFET,其源/漏區由n++型InGaAs cap層構成,采用厚上勢壘層和硅δ摻雜;

(b) 平面QWFET結構(與a類似),但將肖特基柵替換為high-K/金屬柵疊層結構;

(c) 平面high-K QWFET(與b類似),但在源/漏區移除了厚上勢壘層和硅δ摻雜;

(d)非平面多柵極高K QWFET,其溝道呈“鰭”形,并采用超縮小的漏極-柵極和源極-柵極間距。

通過消除(c)和(d)中的厚上勢壘層及硅δ摻雜,同時利用n++型InGaAs cap層作為載流子供給層,實現了源/漏接觸面積的縮放并保持低電阻特性。

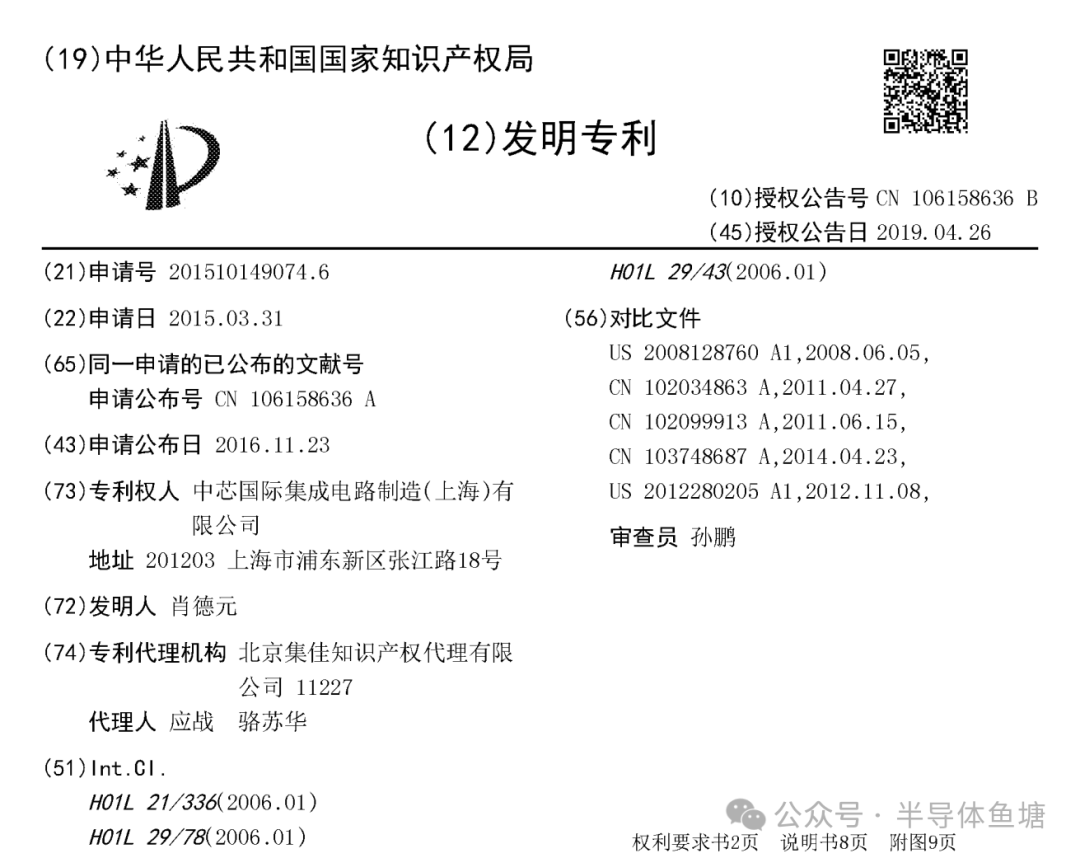

為進一步提高量子阱場效應晶體管的性能,相比于Fin結構的三面柵壓控制,科學家和工程師們再一次將眼光放在全包圍柵結構晶體管上。如下面的專利所描述,肖德元老師提出了一種圓柱體全包圍柵量子阱場效應晶體管,通過其全包圍柵結構來加強器件柵控能力、增強驅動電流以及提高器件集成密度。

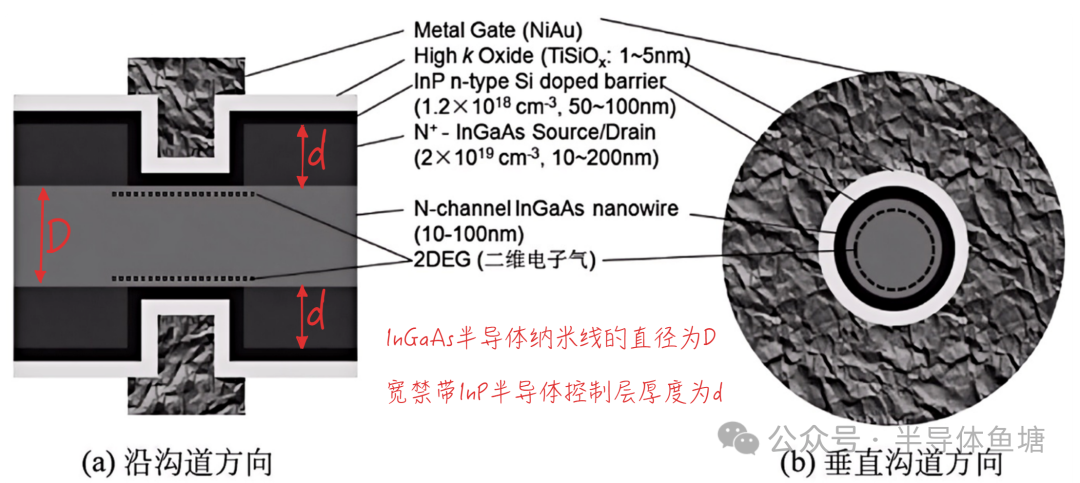

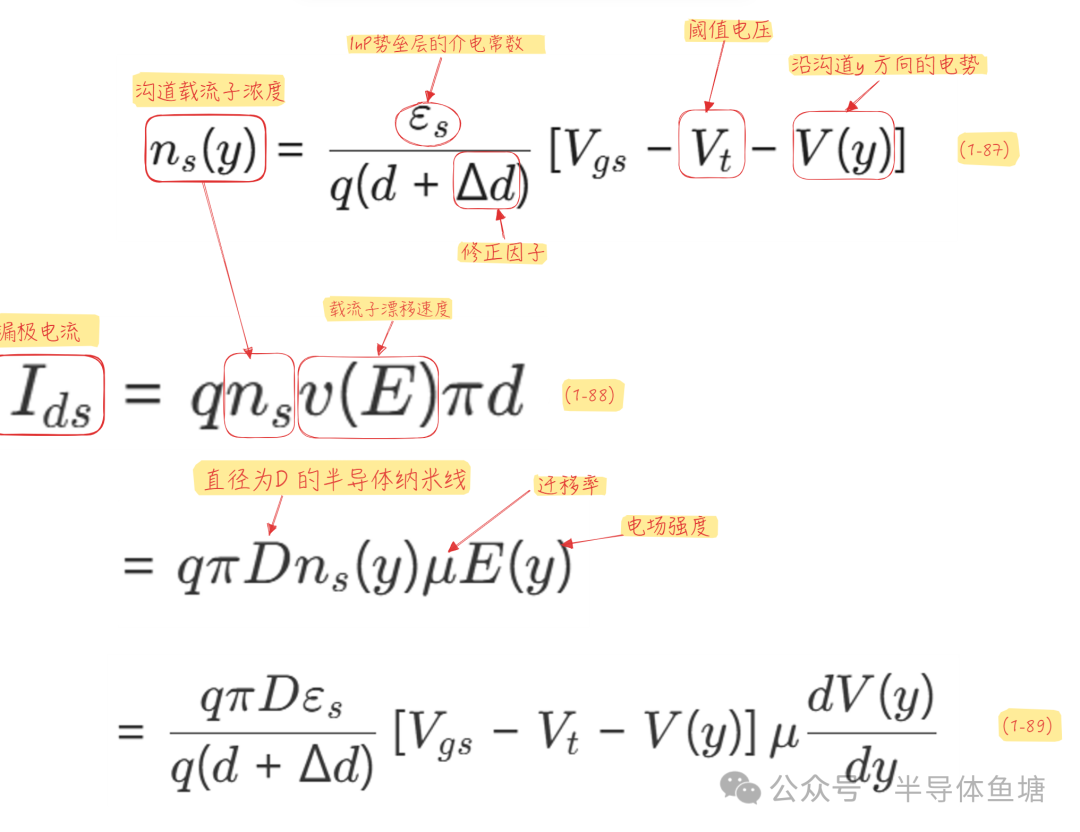

這種圓柱體全包圍柵量子阱場效應晶體管的結構如下圖所示。這里假設InGaAs半導體納米線的直徑為D,寬禁帶InP半導體控制層厚度為d,可以通過電荷控制模型以及逐級溝道近似得到圓柱體全包圍柵量子阱場效應晶體管的I-V關系。

首先求得溝道載流子濃度與Vgs的表達式,然后可以得到漏極電流的表達式。

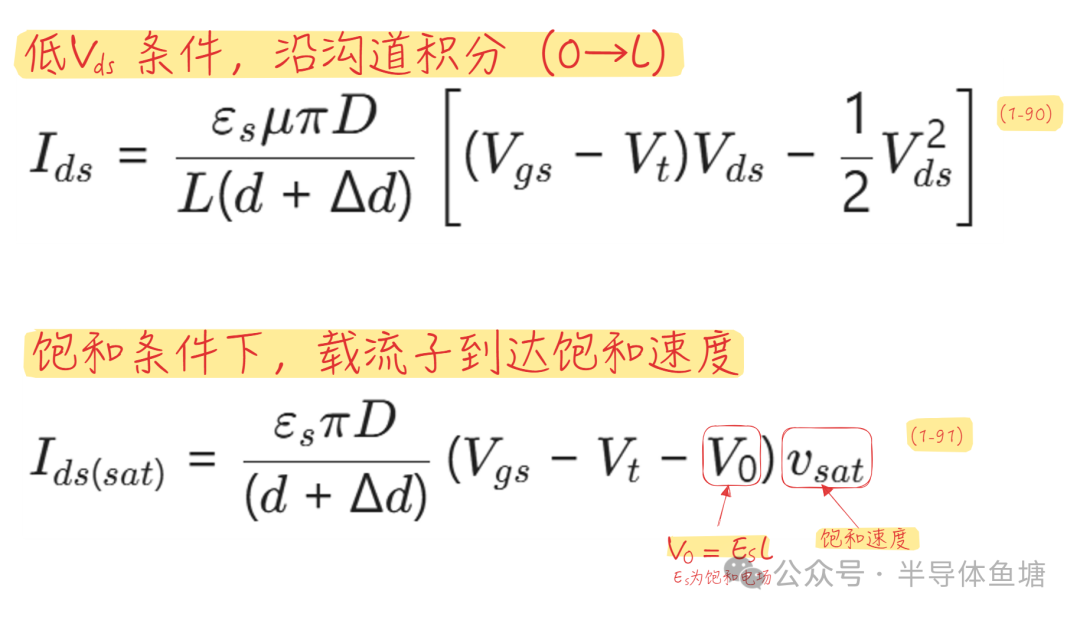

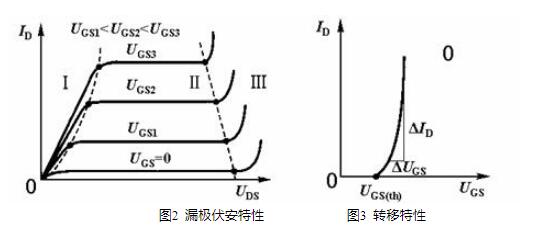

假定載流子遷移率為常數,在低Vds條件下,溝道電流未達到飽和,通過沿溝道方向對電壓積分可以得到圓柱體全包圍柵量子阱場效應晶體管的I-V 特性。

當Vds值增加,載流子達到飽和速度Vsat,I-V特性可以寫作1-91式。

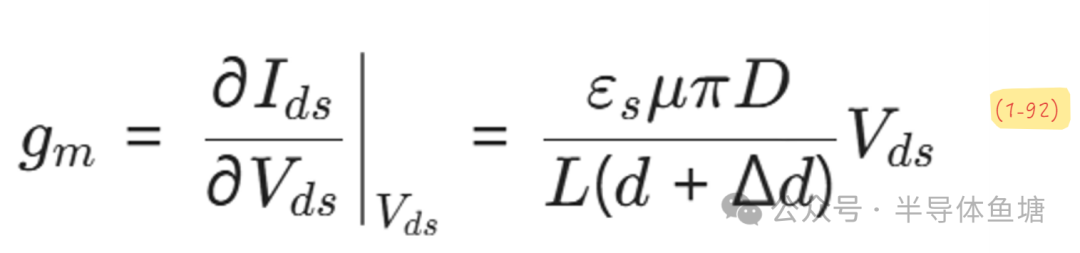

跨導為描述輸入電壓變化對輸出電流的控制能力的參數,根據其定義可以直接得到跨導的表達式。

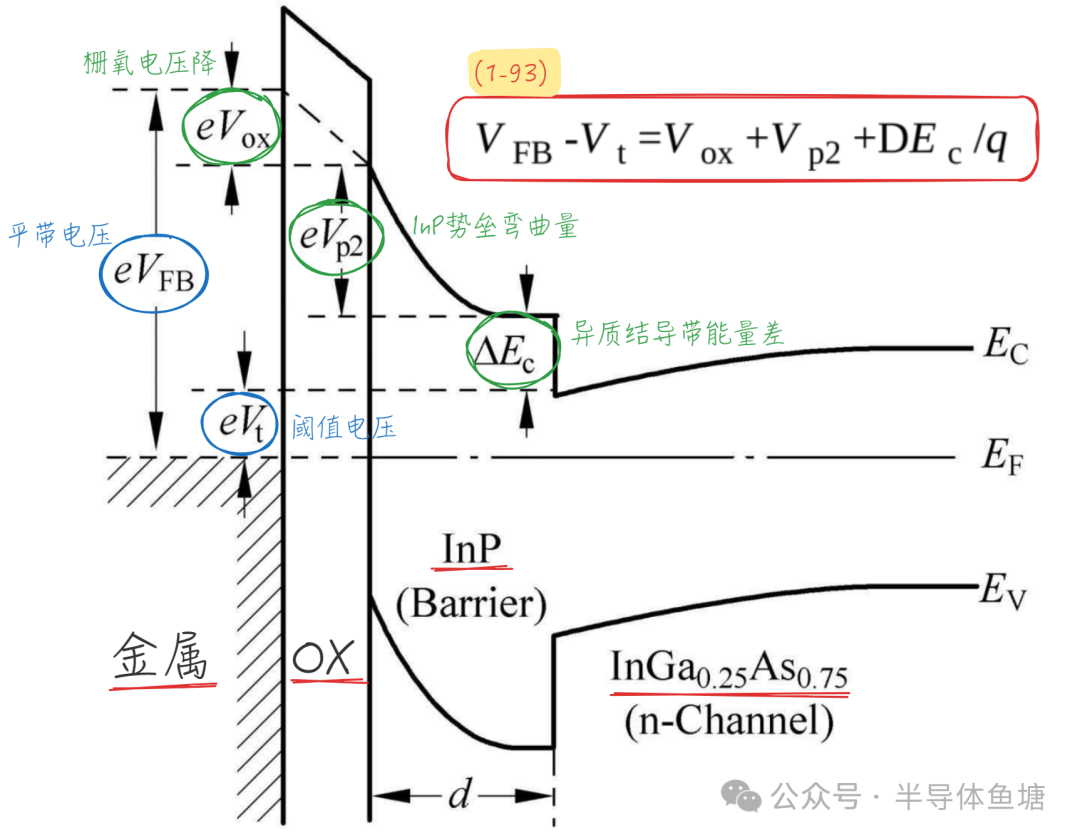

參照插入了一個高k柵介質層的量子阱HEMT器件能帶圖,可以得到1-93的表達式。

柵氧電壓可以通過1-94、1-95和1-96來表示,InP寬禁帶半導體控制層勢壘彎曲量Vp2可以通過1-97式得到,這里的過程比較簡明,不詳細說明。

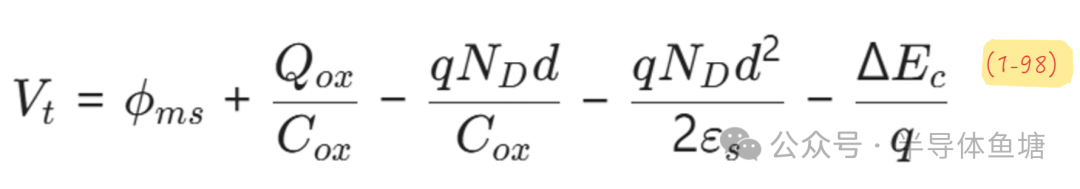

最后可以得到閾值電壓的表達式1-98,其中Qox為柵氧化層中的固定電荷面密度,φms為金屬柵電極與InP寬禁帶半導體控制層之間的功函數差。

1.11 小結

無結場效應晶體管(JFET)通過消除源漏PN結、抑制短溝道效應及提升載流子遷移率,展現出優于傳統MOSFET的潛力,結合高遷移率III-V族材料(如InGaAs)與三維FinFET/GAA結構創新,為突破硅基CMOS性能極限、實現高頻低功耗芯片提供了關鍵技術路徑,推動微電子器件向異質集成與后摩爾時代演進。

-

MOSFET

+關注

關注

150文章

8541瀏覽量

220117 -

半導體

+關注

關注

335文章

28856瀏覽量

236863 -

晶體管

+關注

關注

77文章

10013瀏覽量

141465

原文標題:納米集成電路制造工藝-第1章 半導體器件(1.10/1.11)

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何判斷場效應晶體管方向,學會這幾步輕松搞定

MOS管與場效應晶體管背后的聯系,看完后就全明白了

場效應晶體管在電路中的特別應用,你未必全都清楚

場效應晶體管的分類及作用

場效應晶體管的選用經驗分享

什么是鰭式場效應晶體管?鰭式場效應晶體管有哪些優缺點?

場效應晶體管的分類及使用

什么是場效應晶體管

功率場效應晶體管的工作特性

如何進行場效應晶體管的分類和使用

場效應晶體管的分類說明

場效應晶體管的作用

量子阱場效應晶體管介紹

量子阱場效應晶體管介紹

評論