在高帶寬、高頻率、高同步精度的電子系統中,傳統單端晶體振蕩器已難以滿足系統對信號完整性與誤碼率控制的嚴苛要求。差分振蕩器憑借其抗干擾能力強、信號穩定性高、驅動能力優異的特性,逐步取代傳統晶振,成為數據中心、通信基站、高速接口控制平臺的主力時鐘源。特別是具備0.15ps超低相位抖動性能的差分輸出晶振,其在SerDes、ADC、光通信等系統中發揮著至關重要的作用。

什么是差分振蕩器?

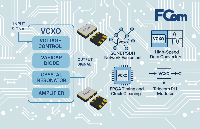

差分振蕩器是一類采用雙信號輸出(正負對稱)的高性能晶體時鐘器件,常見輸出接口包括LVDS、LVPECL與HCSL。與單端CMOS輸出不同,差分信號在布線中可以相互抵消干擾,提高時鐘線上的抗EMI能力,同時大幅減少抖動對系統造成的誤差放大。其輸出上升沿陡峭、信號擺幅穩定、對稱性強,可直接驅動高速SerDes鏈路、FPGA時鐘樹或多路同步ADC等應用。作為現代高速通信與數據處理平臺的重要組成部分,差分晶振廣泛用于數據中心交換設備、5G通信模塊、高速網絡存儲、工業級數據采集等領域。

0.15ps RMS抖動意味著什么?

0.15ps RMS相位抖動代表著極為純凈的時鐘信號輸出,是衡量時鐘源質量的核心指標之一。對于PCIe Gen4/Gen5、40G/100G光模塊、SerDes鏈路或高速DAC輸入等應用而言,時鐘抖動越低,系統誤碼率越小,數據恢復與同步越穩定。通過精準控制晶片振蕩頻率、驅動級電路優化與內部抑噪技術,部分差分振蕩器可將抖動壓縮至0.1ps以下,支撐多通道、高帶寬的數據系統運行。相比普通晶振的3~5ps抖動水平,0.15ps級差分振蕩器具備更高的通信完整性與更寬的帶寬容忍度。

常見差分輸出類型及應用匹配

差分振蕩器常采用三類主流接口輸出:LVPECL、LVDS與HCSL。LVPECL具有高驅動能力,適用于超高速接口如10G SFP+、25G/40G SerDes鏈路;LVDS功耗低、線性好,常用于FPGA/SoC時鐘輸入、視頻同步信號等;HCSL則廣泛應用于PCIe時鐘網絡,兼容主板與服務器時鐘架構。根據不同系統平臺與終端芯片接口標準選擇合適輸出方式,不僅能提升傳輸效率,也能降低布線復雜度與干擾容忍風險。

典型應用場景與芯片/頻率推薦

1)數據中心高速互連:支持頻點 100~156.25MHz,推薦搭配芯片:Intel Stratix 10、Broadcom BCM82391;

2)光通信模塊:支持頻點 19.44MHz、125MHz、155.52MHz,推薦芯片:MACOM MAOM-002313、Semtech GN2117;

3)PCIe系統:支持頻點 25MHz、100MHz,搭配Intel Xeon、AMD EPYC平臺用于服務器主板、交換芯片;

4)同步ADC/DAC:推薦頻點 40MHz~100MHz,適配芯片:Analog Devices AD9689、Texas Instruments DAC38RFxx系列。

趨勢展望:更低抖動、更小封裝、更智能接口

未來的差分振蕩器將進一步在三個方向持續優化:一是抖動性能將邁入0.1ps甚至0.05ps RMS級別,服務于112G PAM4、CXL等高速互連技術;二是尺寸將向更小封裝(如2520、3225)過渡,便于部署在高密度PCB與多模平臺中;三是智能接口功能將加入I2C調頻、故障檢測、遠程控制等能力,使振蕩器不僅是時鐘源,更是系統運行的時序“感知中心”。這將極大推動差分晶振在AI服務器、邊緣計算、光電混合模塊等前沿系統中的普及與進化。

總結

差分振蕩器正成為高速通信與高精度同步系統中不可或缺的核心部件,尤其是在對信號完整性與抖動控制提出極高要求的應用中,其0.15ps級超低抖動性能為系統提供了堅實的時鐘保障。隨著SoC頻率提升與數據鏈路高速化趨勢加劇,這類振蕩器將在數據中心、工業平臺、通信骨干與智能終端中持續拓展其應用邊界,成為未來時鐘解決方案演進中的關鍵節點。

-

振蕩器

+關注

關注

28文章

3998瀏覽量

140793 -

低抖動

+關注

關注

0文章

39瀏覽量

5800 -

差分晶振

+關注

關注

0文章

146瀏覽量

722

發布評論請先 登錄

差分TCXO:新一代高精度、低抖動時鐘振蕩器解析

從SFP到OSFP:FCom差分晶振覆蓋全類型光模塊的時鐘設計方案

差分輸出VCXO振蕩器 | FCom富士晶振 - 低抖動時鐘解決方案

中型數據中心應用平臺與差分晶體振蕩器參數對照中型數據中心應用平臺與差分晶體振蕩器參數對照

MG7050VAN 基于聲表的差分多輸出 晶體振蕩器(LVDS)

MG7050HAN 基于聲表的差分多輸出 晶體振蕩器(HCSL)

FCom富士差分振蕩器-高性能交換機中的應用及性能要求

低抖動VCXO振蕩器:SONET時鐘與高速通信的核心時序方案

差分振蕩器:支持0.15ps超低抖動的高速時鐘核心

差分振蕩器:支持0.15ps超低抖動的高速時鐘核心

評論