在高速數據鏈路、網絡交換平臺與先進通信系統中,時鐘源的靈活性與抖動性能直接影響系統信號完整性與可靠性。傳統定制晶振在交期與頻點靈活性方面難以滿足多變的設計需求。而可編程差分振蕩器以其支持多種輸出接口、0.6ps級別低抖動和短交期交付的能力,逐漸成為下一代高速時鐘解決方案的優選。

什么是可編程差分振蕩器?

可編程差分振蕩器是一類具備工廠預設或現場可調輸出頻率的高性能時鐘源,其輸出支持LVPECL、LVDS、HCSL等差分信號格式,適用于多種高速接口和主控平臺。相比傳統固定頻率晶振,可編程版本可實現10MHz~250MHz范圍內任意頻點配置,最大限度提升了系統設計靈活性與兼容性。同時,廠家可提供快速燒錄與頻率對碼服務,常見交期僅為1~3工作日,適合樣品開發、緊急替代、批量切換等多種場景。

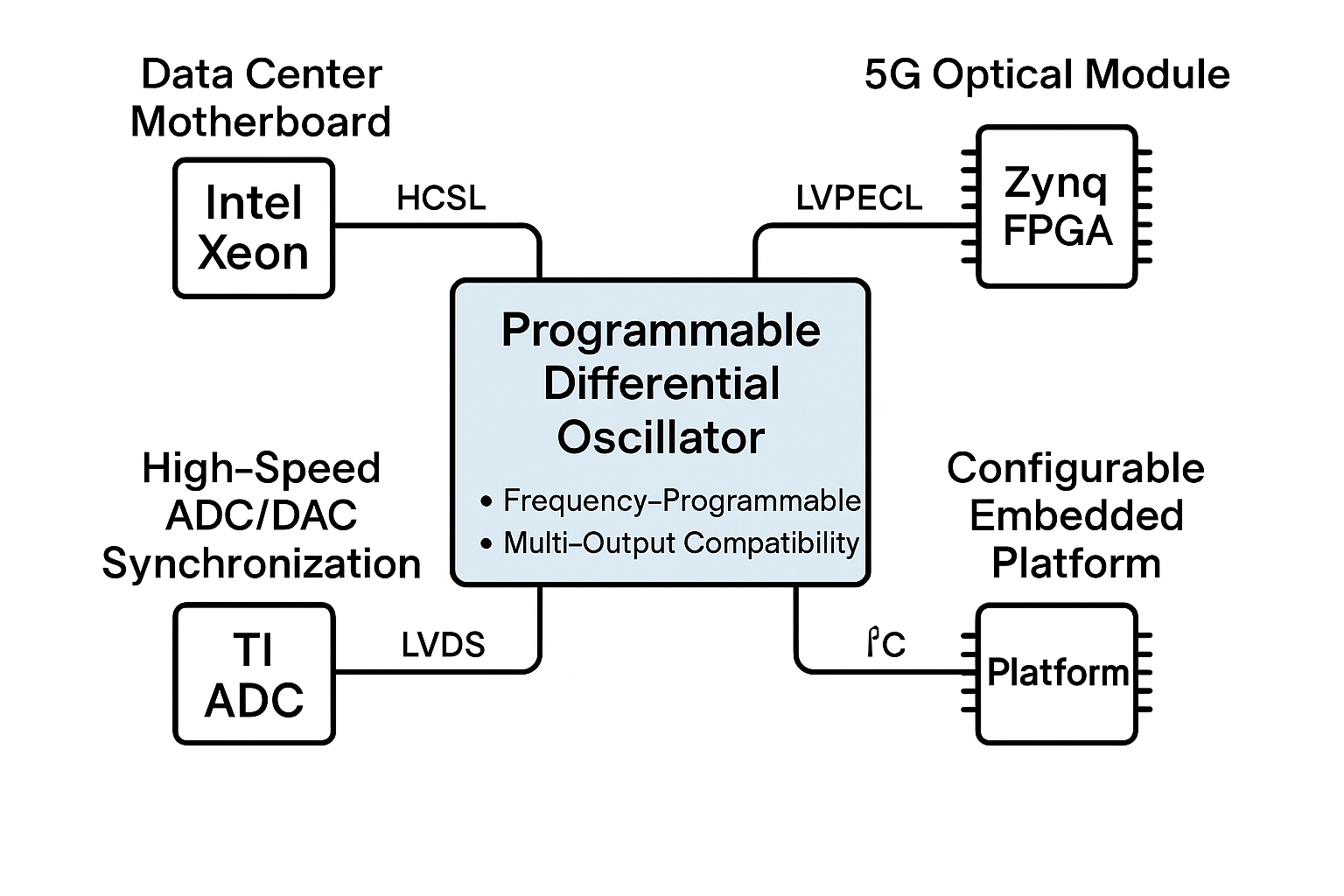

可編程差分振蕩器在數據中心、5G通信、ADC/DAC系統中的典型應用場景圖

可編程差分振蕩器在數據中心、5G通信、ADC/DAC系統中的典型應用場景圖0.6ps RMS抖動對系統意味著什么?

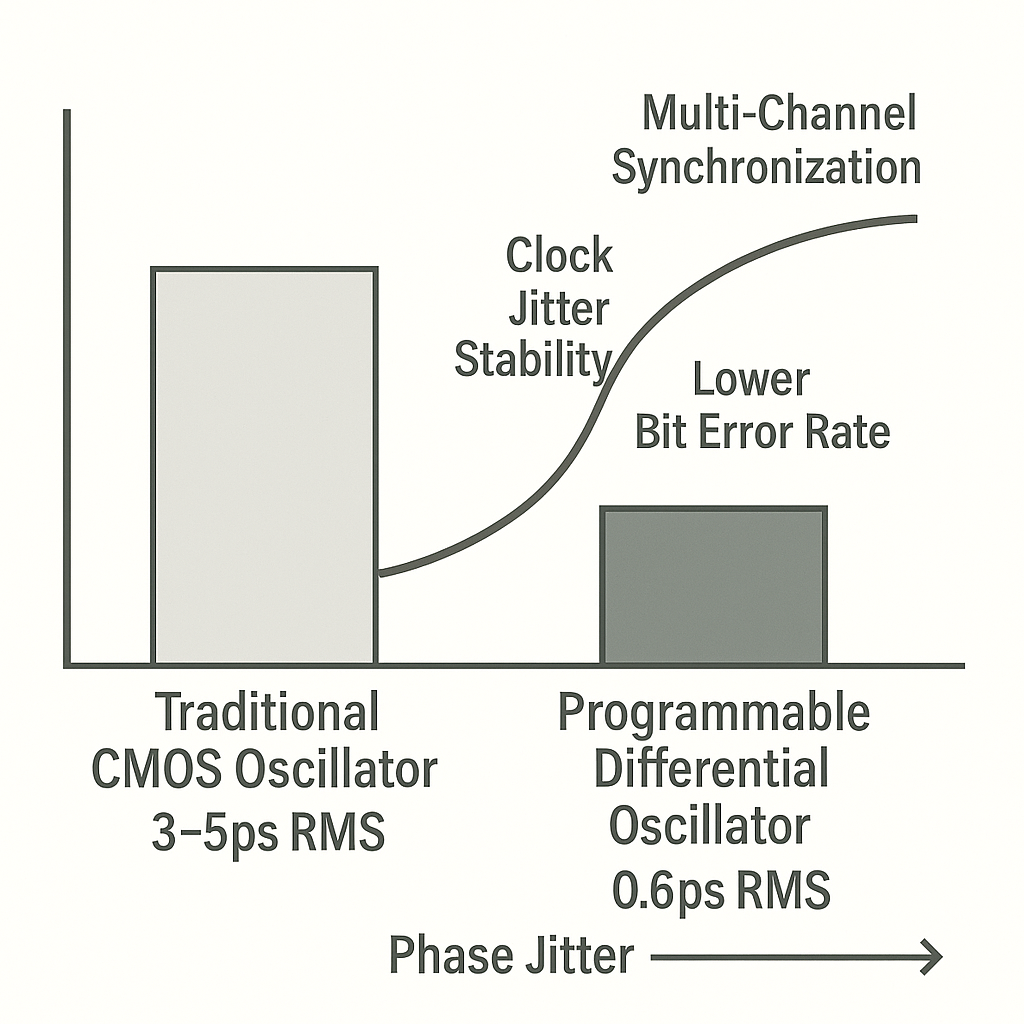

0.6ps RMS抖動已達高速通信與數據轉換系統的基本門檻,能夠有效保障系統誤碼率(BER)與鏈路鎖定精度。在10G/25G以太網、PCIe Gen4/Gen5、SerDes鏈路、ADC采樣或FPGA同步場合中,抖動指標直接決定系統是否穩定可靠。與一般3ps~5ps的CMOS晶振相比,0.6ps級差分振蕩器可顯著減少系統時鐘相位漂移,提升接口一致性,特別適合頻率敏感、高帶寬、高并發任務中的時鐘分發。

0.6ps RMS低抖動差分振蕩器與傳統晶振的性能對比圖,適用于高速通信系統

0.6ps RMS低抖動差分振蕩器與傳統晶振的性能對比圖,適用于高速通信系統支持多種差分輸出:適配多平臺SoC

可編程差分振蕩器通常支持三類主流輸出標準:LVPECL適用于長線驅動與射頻平臺;LVDS具備低功耗、抗干擾特性,適合FPGA、ASIC接口;HCSL則為PCIe專用接口規范,對稱性強、抖動控制優良。工程師可根據主芯片支持接口進行選擇,不同輸出類型封裝一致、配置方式一致,有助于在同一PCB架構中靈活替換。部分型號還可支持單端輸出或雙輸出通道,用于多芯片同步或主備備份結構。

典型應用場景與頻點匹配建議

1)數據中心服務器主板:推薦頻率100MHz、156.25MHz,支持HCSL輸出,適配Intel Xeon、Broadcom交換芯片;

2)5G光模塊與前傳基站:推薦頻率19.44MHz、122.88MHz、161.1328MHz,使用LVPECL輸出,適配Xilinx Zynq、ADRV9026;

3)高速ADC/DAC同步系統:推薦頻率40MHz、80MHz、100MHz,使用LVDS輸出,適配TI ADC12DJ3200、ADI AD9689;

4)可重構嵌入式平臺:推薦頻率20MHz~80MHz,支持I2C可調輸出,適配FPGA、MCU模塊中的動態配置應用。

快速交付機制:加速研發與替代替換

傳統定制晶振往往需2~4周交貨周期,無法滿足樣品開發、小批快轉或臨時替代需求。可編程差分振蕩器通過數字頻率合成(PLL + M/N分頻)方式,實現頻率出廠燒錄,一鍵配置,廠家可根據客戶頻點提供1~3天快速交貨,具備柔性化、小批量、高響應的供應能力。對于需要跨平臺驗證、頻率修改、接口靈活調整的研發流程來說,這類快速交付產品可顯著縮短整體設計周期。

總結

可編程差分振蕩器不僅提供0.6ps RMS低抖動、寬頻率覆蓋、多接口輸出的多重優勢,還具備快速交付、靈活選型的市場應變能力。它已成為數據通信、5G無線、FPGA模塊、高速采樣系統等高性能平臺的核心定時選擇。面對未來多模互聯、異構平臺、高速同步的復雜挑戰,具備高可靠性與快交付能力的差分晶振將持續作為系統架構升級的關鍵推動力。

-

可編程

+關注

關注

2文章

1055瀏覽量

40588 -

差分信號

+關注

關注

4文章

394瀏覽量

28287 -

差分器件

+關注

關注

0文章

12瀏覽量

6144 -

差分晶振

+關注

關注

0文章

145瀏覽量

713

發布評論請先 登錄

愛普生的低抖動溫補可編程晶振

差分可編程晶振YSO210PR滿足電子通信行業多種應用解決方案

愛普生產品-低抖動溫補可編程晶振

愛普生(EPSON) 可編程快速交付有源晶振(SPXO)

快速交付的愛普生可編程振蕩器

可編程差分振蕩器:0.6ps低抖動,滿足高速通信與快速交付需求

可編程差分振蕩器:0.6ps低抖動,滿足高速通信與快速交付需求

評論