答案揭曉之前,請容作者聊個閑篇,講講一個叫做科學方法的東西,看下怎么運用科學方法解決問題。

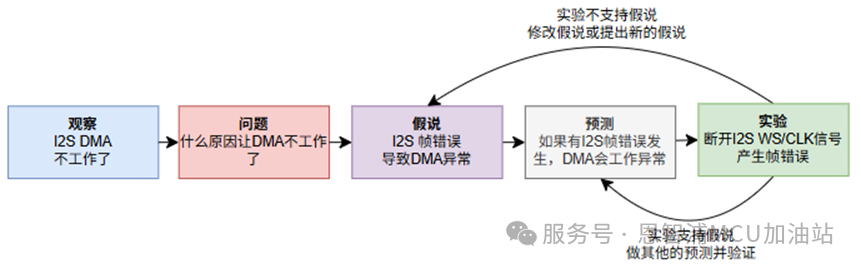

當我們發現I2S DMA不工作時,并且發現了I2S幀錯誤,會有一個假說,I2S幀錯誤導致DMA異常。假說是對一個問題作出的試探性解答,對一組觀察結果提出的解釋。作為工程師,我們不會假設超自然的力量作為DMA不工作的原因,但很多時,我們把一個很像結論的假說用腦補的方式作為問題的結論,而不進行實驗驗證。

回歸正題,上次講到我們嘗試通過I2S0 FIFO Overflow中斷重啟DMA1來解決問題,然而在重啟DMA1后,FIFO Overflow反復發生,意味著DMA1沒有能將數據從FIFO中搬移到內存。

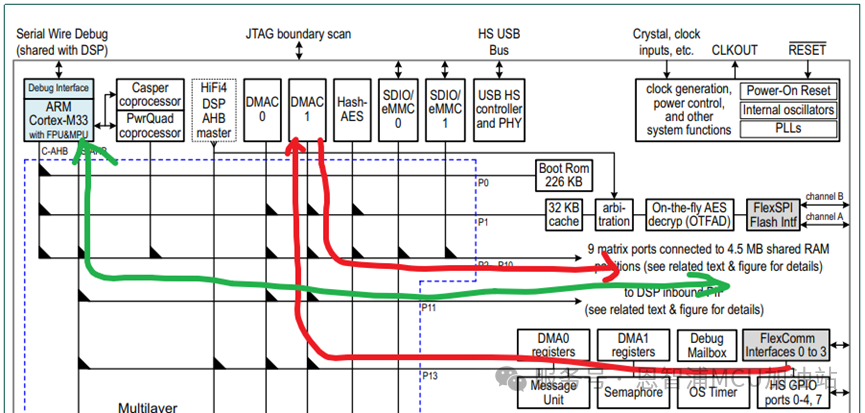

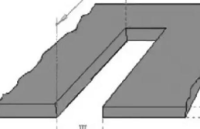

DMA1通過AHB總線從FLEXCOM FIFO讀取數據寫入SRAM的流程如下圖所示,從FIFO讀取數據用到AHB SLAVE PORT P13,寫入SRAM用到了SRAM不同地址塊的AHBSLAVE PORT。當個通路不通的時候,DMA1就無法將數據從P13讀到,或者寫入相應的SRAM區域。

在這條路徑上,有以下懷疑點,P13上,CM33在和HiFi4 DSP通信中會存在輪詢MU狀態寄存器的情況。另外,CM33和DMA1存在同時訪問某SRAM端口的可能性。當CM33頻繁對AHB SLAVE 端口進行訪問時,會影響DMA1對相同AHB SLAVE端口的訪問,從而影響DMA1路徑的延遲(Latency)。

基于以上懷疑,作者建議提高DMA1的AHB總線優先級。

AHB matrix priority (SYSCTL0_AHBMATRIXPRIOR)

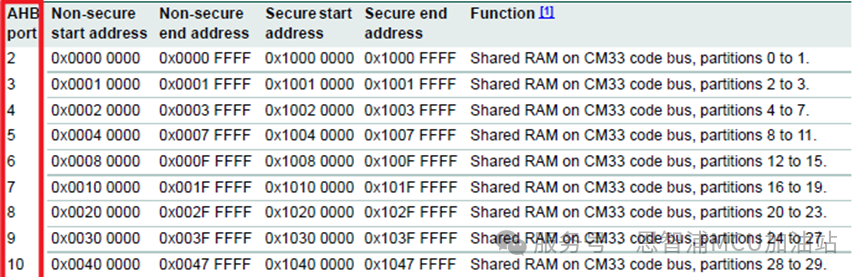

AHB矩陣仲裁各個AHB 總線主設備,當這些AHB主設備同時訪問矩陣的從端口時,仲裁器可以調度各個總線主設備訪問。每一個AHB主設備對應一個ID號和一個4bits的優先級值,默認的優先級設置各個MASTER 都是0(最高)。如果將除了DMA1以外的其他AHB 總線主設備的優先級設置為1,而DMA1的優先級保持為0,就保證了DMA1能夠優先的訪問AHB從設備端口。

經過新的優先級設置,系統穩定性問題解決。

除了調整AHB主機優先級的“大招”,如果我們能盡量避免AHB訪問沖突,既可以提高系統的運行效率又可以增強系統穩定性,下面是避免AHB總線沖突的一些經驗。

1.SRAM通常根據地址范圍不同,使用不同的AHB SLAVE PORT。除了各個AHB Master共享內存以外,每個AHB Master盡量不共享同一個AHB Port, 以避免多個AHB Master同時訪問相同的AHB Slave端口。

當多個AHB主機共享同一AHB Port內存時,避免使用循環輪詢內存變量。

2.避免長時間輪詢狀態寄存器等待狀態轉移,當狀態轉移需要較長時間,中斷是一個更有效的方式。

恩智浦致力于打造安全的連接和基礎設施解決方案,為智慧生活保駕護航。

恩智浦半導體NXP Semiconductors N.V.(納斯達克股票代碼:NXPI)是汽車、工業物聯網、移動設備和通信基礎設施市場值得信賴的合作伙伴,致力于提供創新解決方案。

-

mcu

+關注

關注

146文章

17956瀏覽量

365909 -

NXP

+關注

關注

61文章

1345瀏覽量

189143 -

dma

+關注

關注

3文章

576瀏覽量

103104 -

AHB

+關注

關注

0文章

26瀏覽量

10206 -

壓力測試

+關注

關注

0文章

28瀏覽量

13637

原文標題:工程師經驗分享 -系統壓力測試出現的問題,怎么辦?(下)

文章出處:【微信號:NXP_SMART_HARDWARE,微信公眾號:恩智浦MCU加油站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

系統壓力測試出現的問題要如何解決

系統壓力測試出現的問題要如何解決

評論