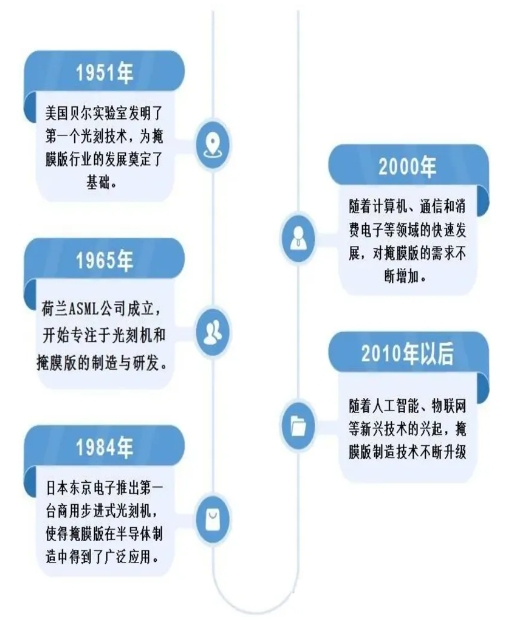

電子發燒友網報道(文/黃山明)在半導體行業邁向3nm及以下節點的今天,光刻工藝的精度與效率已成為決定芯片性能與成本的核心要素。光刻掩模作為光刻技術的“底片”,其設計質量直接決定了晶體管結構的精準度。

然而,隨著摩爾定律逼近物理極限,傳統掩模設計方法面臨巨大挑戰,以2nm制程為例,掩膜版上的每個圖形特征尺寸僅為頭發絲直徑的五萬分之一,任何微小誤差都可能導致芯片失效。對此,新思科技(Synopsys)推出制造解決方案,尤其是掩膜解決方案(Mask Solution),結合AI、GPU加速與全棧式EDA工具鏈,令人眼前一亮。

摩爾定律極限逼近,掩膜設計方案面臨巨大挑戰

隨著摩爾定律逼近物理極限,傳統掩模設計方法正面臨巨大挑戰。首先是復雜度爆炸,尤其是EUV光刻需疊加多層掩模,圖案密度與鄰近效應導致誤差累積。而掩模缺陷可能導致晶圓報廢,要知道單次流片成本高達數百萬美元,如果報廢成本巨大。此外,全芯片光刻仿真需處理PB級數據,過去的傳統CPU計算耗時長達數周。

與此同時,過去傳統掩膜設計主要依賴于工程師數十年的經驗積累,通過試錯調整圖形布局,利用光刻仿真軟件反復驗證,再通過物理掩模制造與晶圓曝光迭代優化。

然而,當制程節點推進至3nm時,這種盲人摸象式的開發模式正遭遇致命瓶頸。EUV光刻的極紫外光線波長僅13.5nm,其衍射效應導致掩模圖形誤差呈指數級放大;High-NA EUV光刻機的視場面積縮小一半,迫使掩模尺寸翻倍至6英寸×12英寸,缺陷密度控制難度陡增;更致命的是,多重圖案化疊加產生的鄰近效應,使得單個掩模層的微小偏差可能在晶圓上放大為數百納米級的電路故障。

而面對這些挑戰,長期以來行業主要依賴兩種路徑去解決。一是通過硬件升級提升光刻機分辨率,例如從0.33NA升級至0.55NA EUV系統;二是優化掩模制造工藝,如采用光學鄰近效應修正(OPC)對掩模版上的圖形做修正。但這些方案就好似在湍急河流中加固堤壩,始終處于被動防御狀態。

而新思科技推出了創新的掩膜解決方案,不再局限于局部優化,而是構建了一套覆蓋“設計-仿真-制造”的全流程智能系統,將掩模設計從經驗驅動的試錯游戲轉變為數據驅動的精準工程。

新思科技推出創新掩膜解決方案

整體來看,新思科技以全流程智能化為核心,推出三大突破性方案:智能光刻仿真、數據驅動的掩模優化、全生命周期協同。

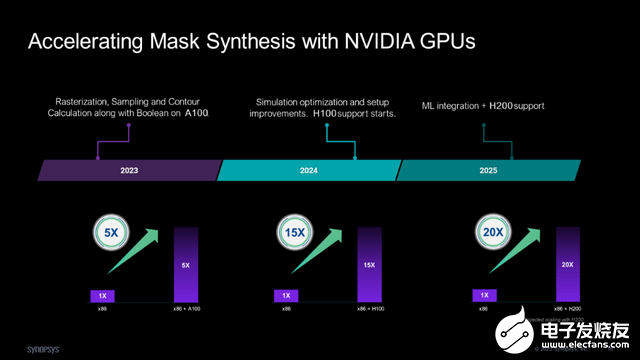

在光刻仿真領域,新思的Proteus軟件與英偉達cuLitho平臺深度融合,將計算光刻工作負載從CPU遷移到H100 GPU,顯著提升效率,例如新思與臺積電、英偉達合作,通過GPU加速計算光刻,使ILT流程總耗時從過去數天CPU計算縮短至不到1天,整體效率提升15倍以上。今年有望集成機器學習并支持H200 GPU,以x86平臺為基準,有望實現20倍的加速。

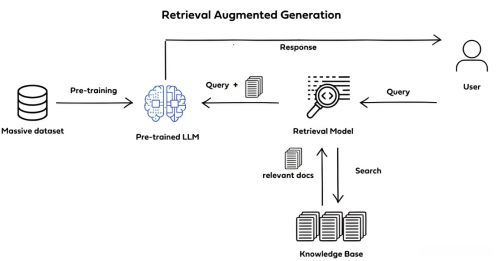

比如在3nm節點的EUV多圖案場景中,新思Proteus結合S-Litho的高精度模擬,通過GPU加速的ILT技術優化掩膜圖案,結合機器學習輔助缺陷預測,顯著提升光刻熱點檢測精度,推動“模擬驅動設計”流程,減少傳統工藝中仿真與制造的脫節。

在掩模數據準備環節,新思的CATS(計算機輔助拓撲系統)軟件憑借高可擴展架構和優化算法,能夠高效處理單層掩膜中數十億多邊形的龐大數據量,支持先進制程下復雜數據的分割、驗證與工程化處理,與Proteus等工具協同實現從設計到制造的數據無縫流轉。

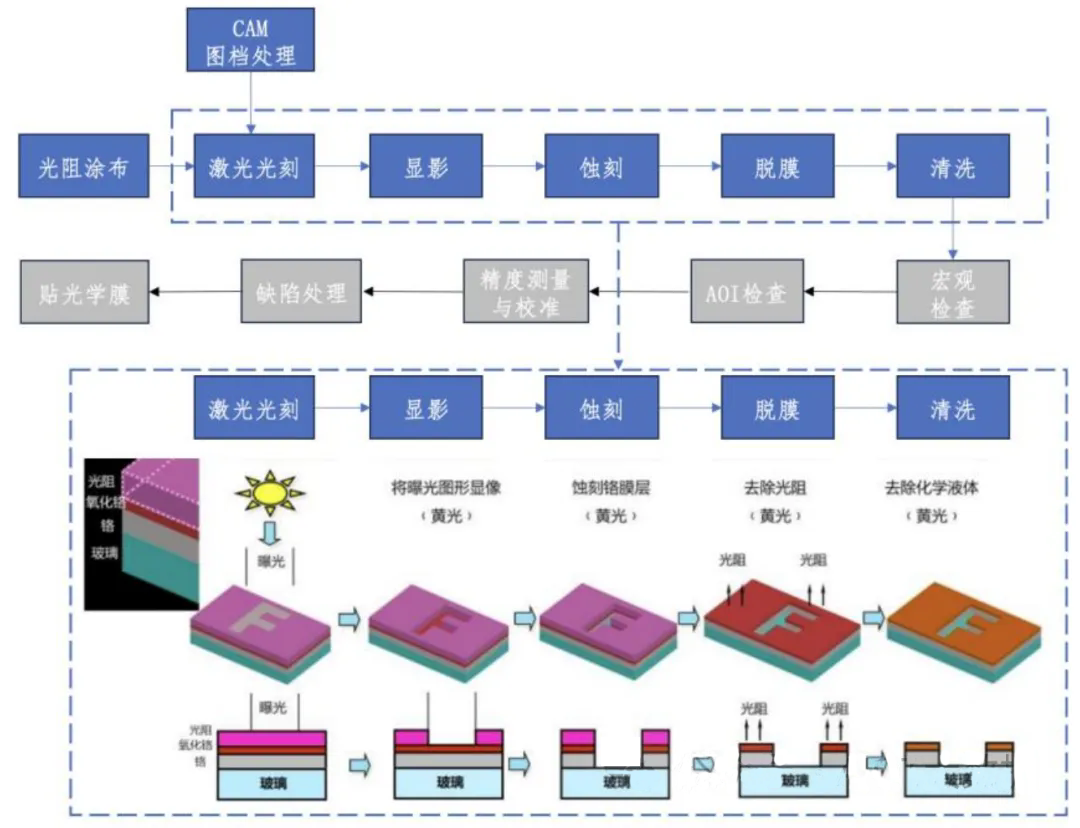

并且CATS與Proteus的深度耦合,如果再加上其他工具,例如與 TCAD(半導體工藝和器件仿真軟件)協同,將使“虛擬掩模驗證”成為可能,實現從掩模設計到工藝制造的全鏈路閉環驗證。這意味著工程師可在數字孿生環境中模擬掩模制造全過程,提前暴露光刻膠涂布不均、蝕刻速率偏差等潛在問題,有望大幅降低流片后的返工率。

用 CATS 掩膜數據準備(MDP,Mask Data Prep)軟件處理掩膜生產的數據,比如數據分割、驗證、尺寸調整等,確保數據準確, CATS和 Proteus 等工具無縫對接,適合半導體、顯示屏(TFT)、傳感器(MEMS)等多種領域。

同時,新思將Proteus和S-Litho緊密集成,為開發模型提供最高的精度和可預測性,從而加快上市時間。S-Litho可以通過GPU加速的物理模擬,實時預測 EUV 曝光、蝕刻過程中的缺陷,結合AI優化模型參數,減少昂貴的實際實驗。

全流程協同則是新思解決方案的護城河。新思的全流程協同方案通過整合掩模制造、晶圓廠工藝參數與終端測試數據(如Synopsys Fab Analytics),構建設計-制造-測試閉環。例如,在良率異常分析中,系統可結合工藝仿真模型追溯掩模版圖誤差,并通過AI推薦離子束拋光參數調整方案。這種“端到端優化”能力,將有效減少臺積電在2nm節點開發中工藝調試周期,并降低掩模相關成本。

這些技術創新正在重塑產業格局。對于芯片設計公司,新思的方案降低了3nm以下節點的開發門檻。對晶圓廠而言,掩模缺陷率的下降直接轉化為經濟效益,每減少1%的掩模缺陷,可避免價值數千萬美元的晶圓報廢。而在宏觀層面,新思的技術路線圖與全球半導體產業的碳中和目標深度契合,即通過優化光刻膠用量與掩模壽命,其方案可降低單片芯片制造碳排放量,為行業ESG實踐提供可量化的路徑。

總結

在半導體制造的精密體系中,新思的掩膜解決方案或許不直接呈現在終端產品上,卻默默支撐著每一顆先進芯片的誕生。它是算力革命與產業需求碰撞的結晶,是算法創新與工程實踐結合的典范。從2nm到更先進的制程,從硅基芯片到新型材料,這套解決方案始終扮演著賦能者的角色,讓人類對微納世界的操控能力不斷突破極限。

當我們驚嘆于智能手機的輕薄、數據中心的高效時,不妨記住,在那些看不見的技術深處,科技領先企業的隱形基礎設施正持續輸出著推動產業進步的核心力量。

-

新思科技

+關注

關注

5文章

863瀏覽量

51385

發布評論請先 登錄

電力電子中的“摩爾定律”(1)

一夜爆火的DeepSeek一體機,如何改寫AI游戲規則?

鉻板掩膜和光刻掩膜的區別

掩膜版、模具與微流控芯片及其制作方法與用途

正性光刻對掩膜版有何要求

混合鍵合中的銅連接:或成摩爾定律救星

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

評論