文章來源:半導體與物理

原文作者:jjfly686

本文主要講述芯片制造中自對準接觸技術。

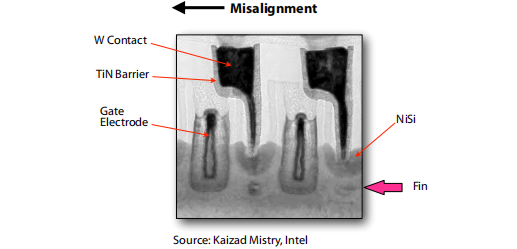

但當芯片做到22納米時,工程師遇到了大麻煩——用光刻機畫接觸孔時,稍有一點偏差就會導致芯片報廢。自對準接觸技術(SAC),完美解決了這個難題。

為什么接觸孔要對得這么準?

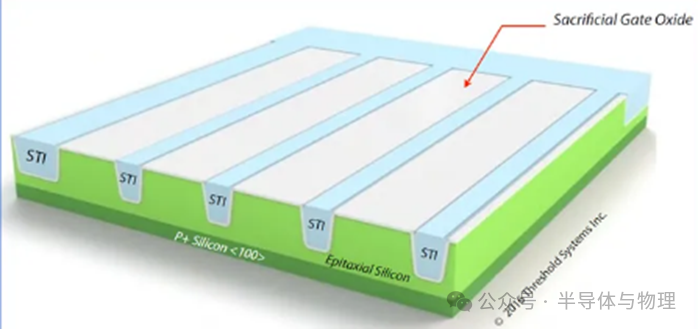

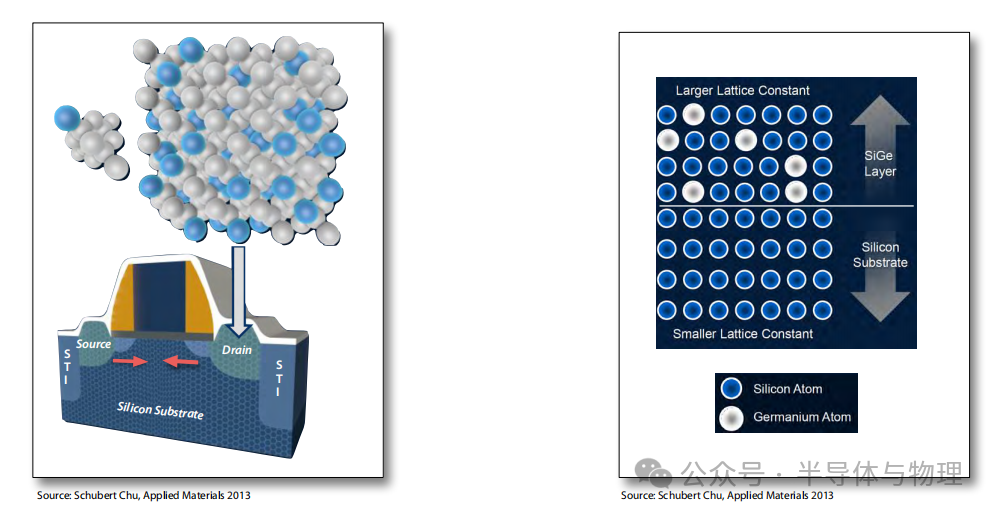

現代FinFET晶體管核心結構包括:金屬柵極:控制電流的開關間隔層:柵極兩側的絕緣保護層接觸孔:連接晶體管的金屬插頭

傳統工藝中,工程師需要先用光刻機在間隔層旁邊精確“打孔”,再把金屬填進去。但在22納米節點,接觸孔和柵極的距離只有15納米。光刻機就像手抖的畫家,最大偏差可能達到5納米——相當于要求人在10米外射箭,箭靶卻只有硬幣大小。

一旦接觸孔打偏:偏移超過5納米:可能戳穿柵極,導致芯片短路;偏移不足5納米:接觸電阻飆升,信號延遲增加

自對準接觸技術(SAC)

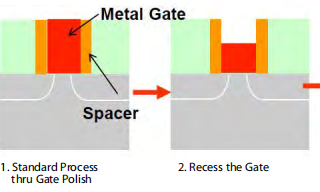

挖槽

先用刻蝕技術把柵極頂端挖出一個凹槽(深度約50納米),就像在柵極頂部刻出一道環形山。

埋入剎車層

在凹槽里填入氮化硅(一種堅硬的材料),這種材料遇到特定氣體時刻蝕會自動停止,相當于埋入隱形防護欄。

放心打孔

刻蝕接觸孔時,刻蝕劑向下腐蝕,遇到氮化硅層就自動停止。無論光刻機畫的孔位置如何偏移,接觸孔底部都會精準停在間隔層外側。

填金屬拋光

最后填入鎢金屬,拋光平整,完成接觸孔制作。

-

半導體

+關注

關注

335文章

28856瀏覽量

236843 -

晶體管

+關注

關注

77文章

10013瀏覽量

141460 -

芯片制造

+關注

關注

10文章

687瀏覽量

29686

原文標題:芯片制造中自對準接觸技術

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Techwiz LCD:基板未對準分析

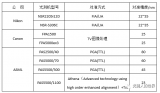

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

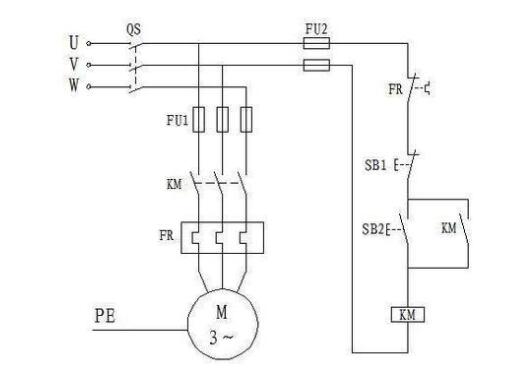

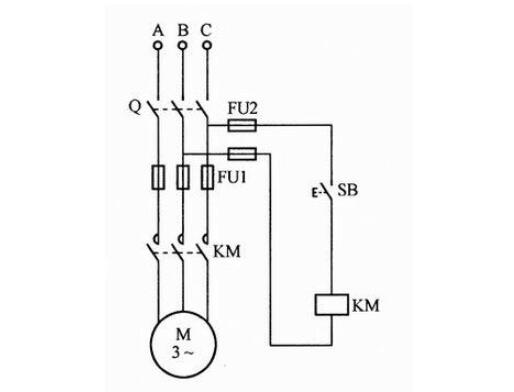

交流接觸器的自鎖和互鎖

IBC技術新突破:基于物理氣相沉積(PVD)的自對準背接觸SABC太陽能電池開發

自對準硅化物工藝詳解

芯片制造中自對準接觸技術介紹

芯片制造中自對準接觸技術介紹

評論