在嵌入式系統(tǒng)研發(fā)領(lǐng)域,隨著產(chǎn)品AI化升級(jí)進(jìn)程,原先設(shè)計(jì)常規(guī)數(shù)字系統(tǒng)的FPGA硬件工程師和系統(tǒng)軟件設(shè)計(jì)師們都不得不面臨技術(shù)轉(zhuǎn)型的問(wèn)題。那么在AI時(shí)代, FPGA廠家與傳統(tǒng)的數(shù)字系統(tǒng)軟硬件工程師們?cè)撊绾无D(zhuǎn)型,才能更好地順應(yīng)市場(chǎng)的需求?

FPGA自誕生起一直在高速?gòu)?fù)雜計(jì)算領(lǐng)域里占有極大的優(yōu)勢(shì),借助于計(jì)算機(jī)輔助設(shè)計(jì)工具通過(guò)Verilog編程,設(shè)計(jì)者可以很方便地將一個(gè)通用結(jié)構(gòu)的FPGA芯片構(gòu)造成一個(gè)規(guī)模宏大的并行的計(jì)算結(jié)構(gòu),這個(gè)結(jié)構(gòu)能以通用CPU無(wú)法比擬的高速進(jìn)行極其復(fù)雜的數(shù)據(jù)處理。在有實(shí)用價(jià)值的圖像分析、語(yǔ)音理解等模式識(shí)別的處理計(jì)算中,通常需要在幾個(gè)毫秒之內(nèi)對(duì)一幅圖像的所有像素逐點(diǎn)進(jìn)行卷積計(jì)算,分析、比較計(jì)算結(jié)果,得到可靠的結(jié)論。算法研究工作者通常用普通計(jì)算機(jī)的軟件來(lái)處理靜態(tài)數(shù)據(jù),得到理論結(jié)果,但實(shí)際應(yīng)用中如此慢的響應(yīng)速度根本無(wú)法滿足實(shí)際工程的需求。最近二十多年來(lái),圖像分析、語(yǔ)音理解等模式識(shí)別研究的算法理論研究已逐步成熟,引起了工業(yè)界的興趣,大量的研究經(jīng)費(fèi)轉(zhuǎn)向如何設(shè)計(jì)可以高速進(jìn)行復(fù)雜數(shù)據(jù)處理的并行計(jì)算機(jī)結(jié)構(gòu),并研發(fā)實(shí)用的AI系統(tǒng)。因此近二十多年來(lái),F(xiàn)PGA芯片和Verilog設(shè)計(jì)/驗(yàn)證方法得到了飛速的發(fā)展。

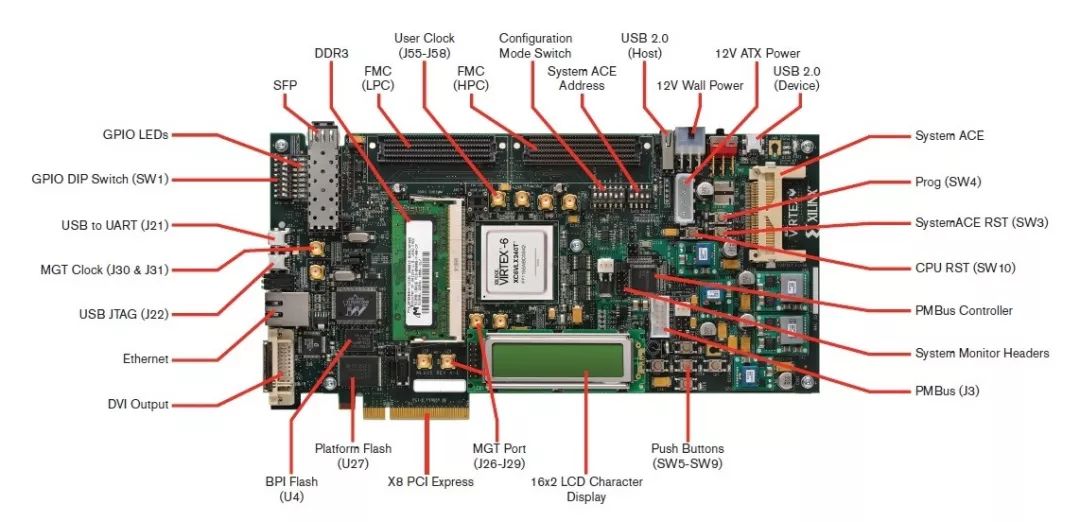

在圖像處理方面,如人臉識(shí)別、指紋識(shí)別、語(yǔ)音識(shí)別方面的機(jī)器人,其AI表現(xiàn)也十分搶眼。 在這一類機(jī)器人的計(jì)算系統(tǒng)中許多極其復(fù)雜的計(jì)算工作,絕大部分都是由FPGA結(jié)構(gòu)實(shí)現(xiàn)的。而且FPGA可以與各種不同的存儲(chǔ)器、各種不同類型的并行接口或是計(jì)算機(jī)接口,如PCIe等方便地連接,它也可以把機(jī)器人與計(jì)算機(jī)網(wǎng)絡(luò)和廣大的知識(shí)庫(kù)融為一體,構(gòu)成極其龐大、響應(yīng)迅速的AI知識(shí)系統(tǒng)。

根我所知,許多AI研究工作者習(xí)慣于用軟件進(jìn)行算法研究,他們中的大多數(shù)人用靜態(tài)的圖像或靜態(tài)的聲音(錄下來(lái)的聲音)做語(yǔ)音理解或者翻譯方面的工作。在整個(gè)過(guò)程中,雖然數(shù)據(jù)處理的計(jì)算速度比較慢,但還是可以得到可靠的分析處理結(jié)果。但是在實(shí)際工程應(yīng)用當(dāng)中,這樣慢的處理速度顯然沒(méi)有多大實(shí)用價(jià)值,因?yàn)樵谠S多場(chǎng)合,響應(yīng)根本無(wú)法用于實(shí)際場(chǎng)合。隨著研究工作向設(shè)計(jì)實(shí)際系統(tǒng)轉(zhuǎn)換,我建議軟件系統(tǒng)的工程師們應(yīng)該學(xué)會(huì)如何使用FPGA,以及如何用FPGA做復(fù)雜計(jì)算的加速。其實(shí)對(duì)計(jì)算機(jī)科學(xué)和工程專業(yè)畢業(yè)的軟件工程師而言,只要有數(shù)字電路的基礎(chǔ)知識(shí),學(xué)習(xí)Verilog HDL語(yǔ)言并不困難,學(xué)會(huì)RTL級(jí)別Verilog的編程來(lái)構(gòu)造可綜合的并行迭代計(jì)算結(jié)構(gòu)并不困難,只需要花費(fèi)一兩個(gè)月就能上手。

而對(duì)于那些在嵌入式系統(tǒng)工作多年的硬件工程師或只有一些簡(jiǎn)單接口設(shè)計(jì)經(jīng)驗(yàn)的FPGA工程師而言,雖然不是一個(gè)專職研究處理算法的軟件編程專家,但他們必須抽一些時(shí)間來(lái)理解算法,幫助算法工程師把電路結(jié)構(gòu)改變得更加合理,令計(jì)算瓶頸變成寬敞的通道。在AI時(shí)代,特別是AI進(jìn)入應(yīng)用的新時(shí)代,一個(gè)真正的硬件工程師不僅應(yīng)該熟練掌握Verilog的語(yǔ)言,學(xué)會(huì)如何用Verilog語(yǔ)言編寫可綜合的并行結(jié)構(gòu),在規(guī)定的時(shí)間間隔內(nèi)完成算法要求的計(jì)算工作量,并且學(xué)會(huì)如何設(shè)計(jì)硬件,讓硬件與算法軟件配合,更有效率地完成算法要求的多種計(jì)算任務(wù)。把原來(lái)算法研究中完全用軟件實(shí)現(xiàn)的計(jì)算過(guò)程,變成用軟件和硬件配合實(shí)現(xiàn)的過(guò)程,把整個(gè)計(jì)算結(jié)構(gòu)改造成一個(gè)可配置的高速處理的結(jié)構(gòu),專門針對(duì)某一領(lǐng)域的人工智能產(chǎn)品,讓這個(gè)硬件有更大的市場(chǎng),這是非常有意義的!

總而言之,對(duì)今天的AI嵌入式系統(tǒng)的設(shè)計(jì)師而言,必須軟硬兼?zhèn)洳拍艹蔀橐粋€(gè)優(yōu)秀的工程師。換言之,軟件人員要往硬件方向轉(zhuǎn),學(xué)習(xí)硬件知識(shí),硬件工程師也必須向軟件工程師靠攏,理解算法的執(zhí)行過(guò)程,為AI算法設(shè)計(jì)新的計(jì)算結(jié)構(gòu)和數(shù)據(jù)通路。這是因?yàn)楝F(xiàn)在AI的軟件編程并不是簡(jiǎn)單地編寫一個(gè)程序得到一個(gè)計(jì)算結(jié)果,還必須考慮計(jì)算的速度是不是足夠夠快。所以實(shí)質(zhì)上是一個(gè)如何設(shè)計(jì)合理的并行結(jié)構(gòu)計(jì)算加速核心硬件,以達(dá)到實(shí)時(shí)全面完成算法要求的問(wèn)題。

轉(zhuǎn)型勢(shì)在必行,F(xiàn)PGA工程師要理解新任務(wù)、掌握新工具

深維科技 CEO 樊平

對(duì)FPGA產(chǎn)品的需求:

1.硬件性能的提升:盡管FPGA在數(shù)據(jù)中心應(yīng)用處于一個(gè)快速增長(zhǎng)過(guò)程,但總體規(guī)模還不是很大,這里面有一些限制,也是FPGA廠商需要努力提升的地方。 首先是價(jià)格問(wèn)題,F(xiàn)PGA的大規(guī)模部署需要FPGA硬件成本盡快降下來(lái),這個(gè)要靠工藝進(jìn)步以及市場(chǎng)規(guī)模來(lái)解決;其次是存儲(chǔ)訪問(wèn)帶寬,HBM技術(shù)以及CCIX是代表性的方向。

2.軟件工具的提升:FPGA需要軟件工具來(lái)輔助工程師完成設(shè)計(jì)過(guò)程,在新的應(yīng)用領(lǐng)域?qū)υO(shè)計(jì)的內(nèi)容、流程、驗(yàn)證方法等都提出了新的需求,例如AI應(yīng)用客戶希望具備高層次的模型定制能力,但是目前還沒(méi)有廠商可以提供成熟的方案。這也為新的工具提供商提供了機(jī)會(huì)。

3.生態(tài)系統(tǒng):GPU獲得了廣泛的認(rèn)同和應(yīng)用,這與CUDA長(zhǎng)期的演進(jìn)和積累密不可分。新興應(yīng)用領(lǐng)域大都有流行的設(shè)計(jì)框架和開(kāi)源項(xiàng)目。FPGA一般作為高性能計(jì)算硬件來(lái)加速現(xiàn)有項(xiàng)目,所以需要和這類設(shè)計(jì)框架進(jìn)行融合,也需要大量基礎(chǔ)庫(kù)/IP來(lái)支持用戶快速完成設(shè)計(jì)。所以一個(gè)成熟的生態(tài)系統(tǒng)至關(guān)重要,目前這塊也還是非常薄弱。

對(duì)FPGA工程師的需求:

1.理解新任務(wù):傳統(tǒng)FPGA工程師面對(duì)的是硬件的設(shè)計(jì)問(wèn)題,但AI等應(yīng)用與應(yīng)用系統(tǒng)關(guān)系密切,不單純是FPGA片上邏輯設(shè)計(jì)的問(wèn)題。工程師往往需要了解上層軟件如何與FPGA片上系統(tǒng)的集成與優(yōu)化問(wèn)題。

2.掌握新工具:FPGA主流廠商很早就開(kāi)始布局新興市場(chǎng)的應(yīng)用,一個(gè)主要工作就是提升FPGA設(shè)計(jì)開(kāi)發(fā)抽象層次,OpenCL/HLS語(yǔ)言就是典型代表,一般情況下可以提升數(shù)倍開(kāi)發(fā)效率。所以FPGA工程師需要充分掌握這類新的工具,以保障自己能有足夠的效率面對(duì)行業(yè)需求。

3.抓住新機(jī)遇:新興應(yīng)用領(lǐng)域不僅僅是FPGA市場(chǎng)的簡(jiǎn)單擴(kuò)充,它也為FPGA應(yīng)用帶來(lái)新的商業(yè)模式,以FaaS為代表的應(yīng)用形式,為FPGA開(kāi)發(fā)人員帶來(lái)眾多新的商業(yè)機(jī)遇。

Achronix的Speedcore IP具有支持先進(jìn)人工智能技術(shù)的正確功能組合

Achronix 半導(dǎo)體公司市場(chǎng)營(yíng)銷副總裁 Steve Mensor

人工智能(AI)應(yīng)用要求高性能,并且在許多情況下,低延遲能夠成功地響應(yīng)條件和需求的實(shí)時(shí)變化。它們還要求功耗盡可能的低從而意味著無(wú)法使用,其解決方案是將機(jī)器學(xué)習(xí)放在供電和制冷能力充足的云服務(wù)器端。對(duì)這些嵌入式系統(tǒng)的進(jìn)一步要求是,即使在沒(méi)有網(wǎng)絡(luò)連接到云端的情況下也都能隨時(shí)工作并且準(zhǔn)備好做出響應(yīng)。這些因素的組合要求在硬件設(shè)計(jì)方法上做出改變。

人工智能要求謹(jǐn)慎地平衡數(shù)據(jù)通路的性能、內(nèi)存延遲和吞吐量,這就需要用一種方法來(lái)將盡可能多的功能放到專用集成電路(ASIC)或系統(tǒng)級(jí)芯片(SoC)上。過(guò)添加eFPGA技術(shù),則提供了市場(chǎng)需要的一種解決方案,來(lái)將靈活性以及客制化邏輯單元支持能力結(jié)合在一起。

作為專為嵌入到SoC和ASIC之中而設(shè)計(jì)的硅知識(shí)產(chǎn)權(quán)(IP),Achronix的Speedcore eFPGA IP是一種高度靈活的解決方案,它支持高性能機(jī)器學(xué)習(xí)應(yīng)用中需要的數(shù)據(jù)吞吐量。通過(guò)借助其可切分的架構(gòu),Speedcore IP為設(shè)計(jì)人員提供了滿足其應(yīng)用要求的能力來(lái)實(shí)現(xiàn)eFPGA功能的混合和匹配。Speedcore IP的核心功能包括基于四輸入查找表(LUT)的邏輯單元、用于寄存器文件和類似應(yīng)用并面向邏輯單元的小型存儲(chǔ)器(LRAM)、較大的單元塊存儲(chǔ)器(BRAM)和可配置的數(shù)字信號(hào)處理器(DSP)模塊。根據(jù)應(yīng)用的要求,Speedcore基于縱列的架構(gòu)可提供準(zhǔn)確混合資源的能力。

FPGA工程師要這樣擁抱AI

資深嵌入式軟件工程師 楊鑫

FPGA本身作為一種可編程的邏輯器件,其最突出的特性在于可編程的邏輯部分,這與傳統(tǒng)CPU的順序執(zhí)行方式有著本質(zhì)區(qū)別,與ASIC相比又有著較好的靈活性,在AI產(chǎn)業(yè)興起之前,就一直是ASIC設(shè)計(jì)的前期驗(yàn)證手段。但現(xiàn)在FPGA器件的發(fā)展已經(jīng)跨越了可編程這個(gè)特性,現(xiàn)在的FPGA器件往往擁有遠(yuǎn)比通用芯片更高的I/O帶寬和內(nèi)存帶寬例如高達(dá)40Gbps的serdes接口,以及HBM2等超高速內(nèi)存接口,這些接口使得FPGA在通信領(lǐng)域有著非常廣泛的應(yīng)用。

現(xiàn)如今,由于很多AI產(chǎn)品對(duì)內(nèi)存帶寬和互聯(lián)互通性有著相當(dāng)高的要求,在較輕運(yùn)算量的情況下,F(xiàn)PGA的可應(yīng)用場(chǎng)景有了非常大的突破,所以很多小批量、快迭代的產(chǎn)品,其最佳開(kāi)發(fā)方式反而變成了FPGA,而非ASIC或者GPU等等,因此FPGA開(kāi)發(fā)人員,只要多熟悉AI技術(shù)、熟悉AI應(yīng)用需求,仍然可以在AI行業(yè)游刃有余,不斷打造新的傳奇。

現(xiàn)在的圖像處理和數(shù)據(jù)的傳輸、分配這些事情在人工智能開(kāi)發(fā)方面發(fā)揮著重要作用,在AI時(shí)代需要FPGA工程師尤其是做軟件算法和做硬件設(shè)計(jì)的人要優(yōu)勢(shì)互補(bǔ)。

產(chǎn)品設(shè)計(jì)好后還要與原來(lái)的計(jì)算機(jī)與服務(wù)器連接在一塊兒,那么還需要做系統(tǒng)級(jí)設(shè)計(jì)。這對(duì)FPGA的軟件工程師、硬件工程師都是一個(gè)新的挑戰(zhàn)。希望FPGA工程師們成功轉(zhuǎn)型,為AI時(shí)代能設(shè)計(jì)出更好的產(chǎn)品助力。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21983瀏覽量

614636 -

AI

+關(guān)注

關(guān)注

88文章

34421瀏覽量

275751

原文標(biāo)題:AI時(shí)代FPGA廠商與FPGA工程師該如何轉(zhuǎn)型?

文章出處:【微信號(hào):mcuworld,微信公眾號(hào):嵌入式資訊精選】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

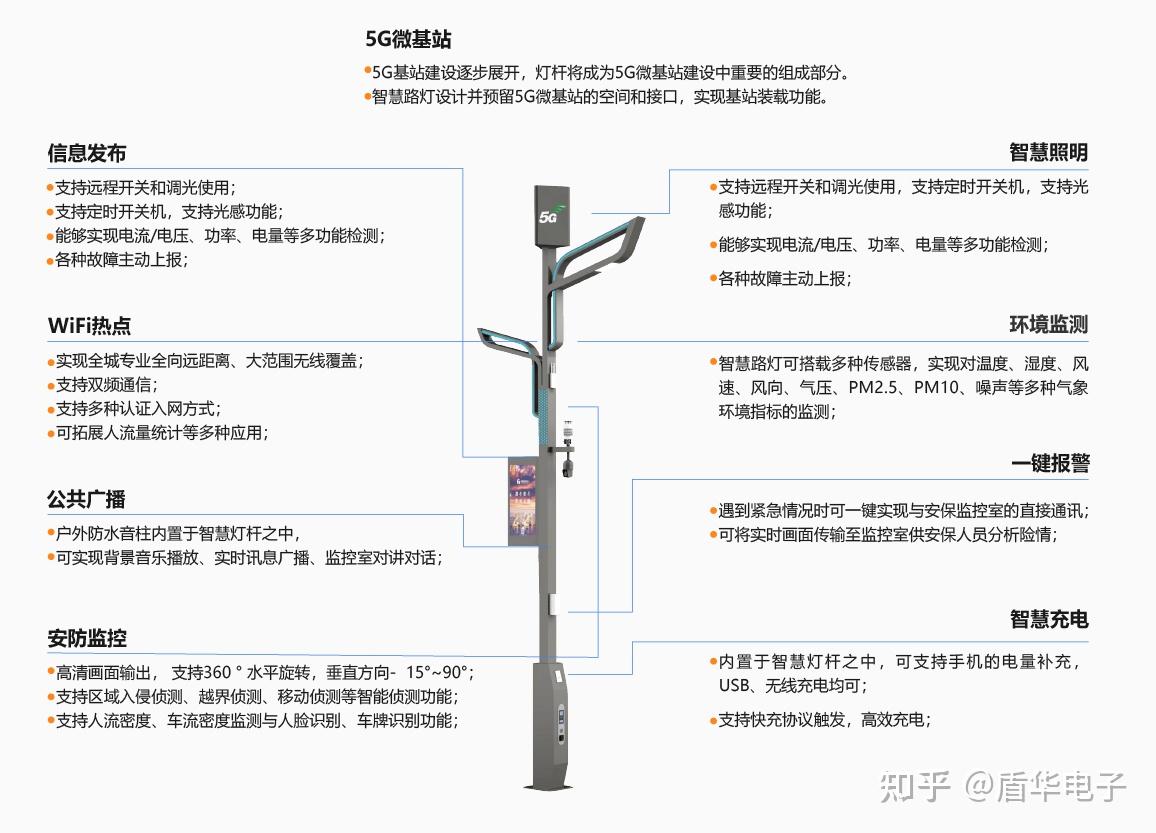

為什么智能路燈是智慧城市發(fā)展的關(guān)鍵,物聯(lián)網(wǎng)城市生命線系統(tǒng)

住建部新政落地,漫途如何織密城市生命線監(jiān)測(cè)網(wǎng)?

?住建部新政落地,如何織密城市生命線監(jiān)測(cè)網(wǎng)?

頂堅(jiān)北斗有源終端:應(yīng)急通信的‘生命線’與精準(zhǔn)定位的‘守護(hù)者

FPGA+AI王炸組合如何重塑未來(lái)世界:看看DeepSeek東方神秘力量如何預(yù)測(cè)......

當(dāng)我問(wèn)DeepSeek AI爆發(fā)時(shí)代的FPGA是否重要?答案是......

工業(yè) 4G?路由器賦能遠(yuǎn)程醫(yī)療,守護(hù)生命線

連接器:工廠中的生命線,默默無(wú)聞的紐帶

Verilog 測(cè)試平臺(tái)設(shè)計(jì)方法 Verilog FPGA開(kāi)發(fā)指南

Verilog vhdl fpga

城市生命線守護(hù)者 確保16萬(wàn)戶家庭用水安全,打造穩(wěn)定供水網(wǎng)

FPGA算法工程師、邏輯工程師、原型驗(yàn)證工程師有什么區(qū)別?

一網(wǎng)統(tǒng)管政企聯(lián)動(dòng):計(jì)訊構(gòu)建城市生命線安全智能體的應(yīng)急管理革新

【招聘】verilog vhdl FPGA

水電氣安全監(jiān)測(cè)解決方案|守護(hù)城市生命線

掌握 Verilog FPGA設(shè)計(jì)和驗(yàn)證方法是AI時(shí)代系統(tǒng)設(shè)計(jì)師的生命線

掌握 Verilog FPGA設(shè)計(jì)和驗(yàn)證方法是AI時(shí)代系統(tǒng)設(shè)計(jì)師的生命線

評(píng)論