文章來源:半導(dǎo)體與物理

原文作者:jjfly686

本文介紹了先進(jìn)集成電路制造多重曝光中的套刻精度要求。

在半導(dǎo)體工廠的潔凈室里,光刻機(jī)如同一位在納米畫布上作畫的藝術(shù)家。但當(dāng)這位“畫家”的筆觸精細(xì)到20納米以下時(shí),它的雙手開始顫抖——不是源于技藝不足,而是物理定律的桎梏。

為了突破這一限制,工程師們發(fā)明了多重曝光技術(shù),卻意外打開了潘多拉魔盒:對準(zhǔn)復(fù)雜度(Overlay Complexity)的指數(shù)級暴增。這場納米級的疊影戰(zhàn)爭,正在重塑芯片制造的底層邏輯。

一、光刻機(jī)的“視力衰退”與拆解藝術(shù)

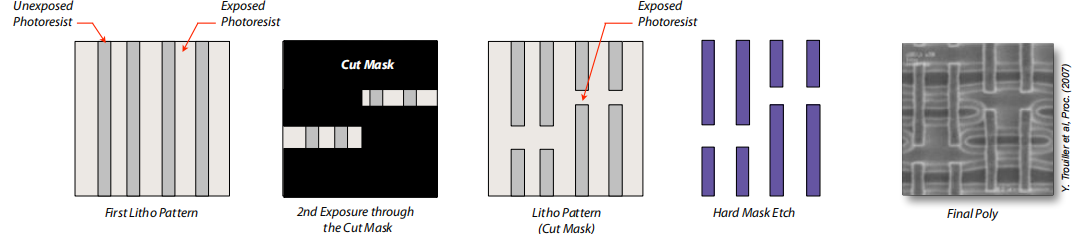

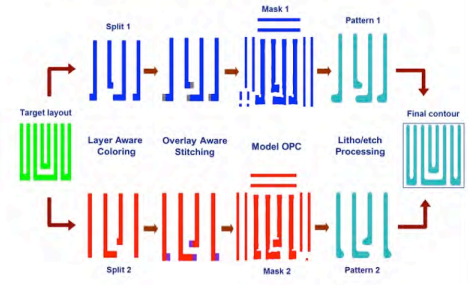

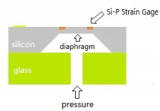

當(dāng)芯片制程進(jìn)入20納米節(jié)點(diǎn)(相當(dāng)于人類頭發(fā)直徑的1/4000),193nm浸沒式光刻機(jī)遭遇物理極限——其光學(xué)系統(tǒng)如同近視加深的雙眼,無法分辨間距小于80納米的密集電路。為此,工程師將一張電路設(shè)計(jì)圖拆解為多張“分鏡稿”:

雙重曝光:將金屬層分解為紅藍(lán)兩版,如同把樂高模型拆成兩套組件。

三重曝光:在10nm節(jié)點(diǎn),甚至需要將圖形拆分為三套獨(dú)立掩模

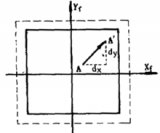

但拆解后的圖案需要完美拼接,這要求每次曝光后的硅片位置必須精準(zhǔn)對齊,誤差需控制在3納米以內(nèi)。

二、對準(zhǔn)步驟的“多米諾骨牌效應(yīng)”

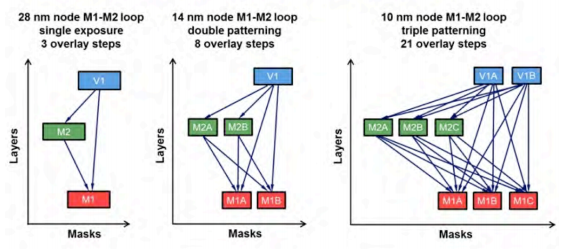

以芯片中最基礎(chǔ)的金屬-通孔(Metal-Via)連接結(jié)構(gòu)為例:

28nm節(jié)點(diǎn)(單次曝光):只需3次對準(zhǔn)操作,如同拼裝三塊標(biāo)準(zhǔn)積木。

14nm節(jié)點(diǎn)(雙重曝光):對準(zhǔn)步驟激增至8次,相當(dāng)于用八根不同顏色的線穿同一枚針眼。

10nm節(jié)點(diǎn)(三重曝光):需要21次對準(zhǔn),復(fù)雜度堪比用21把鑰匙同時(shí)開啟一把鎖

更驚人的是,若10nm節(jié)點(diǎn)采用四重曝光,對準(zhǔn)操作將達(dá)40次。

納米疊影的“蝴蝶效應(yīng)”

對準(zhǔn)誤差帶來的不僅是時(shí)間成本,更會(huì)引發(fā)更多的問題:

短路危機(jī):金屬層間5納米的錯(cuò)位,可能導(dǎo)致相鄰電路導(dǎo)通。

電阻增大:通孔偏移,接觸電阻可能飆升。

良率降低:在7nm節(jié)點(diǎn),10%的對準(zhǔn)失誤會(huì)直接導(dǎo)致整片晶圓報(bào)廢。

-

集成電路

+關(guān)注

關(guān)注

5423文章

12038瀏覽量

368264 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28865瀏覽量

237104 -

芯片制造

+關(guān)注

關(guān)注

10文章

687瀏覽量

29697

原文標(biāo)題:芯片制造多重曝光中的套刻精度要求

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

《大話芯片制造》閱讀體會(huì)分享_1

【「大話芯片制造」閱讀體驗(yàn)】+ 半導(dǎo)體工廠建設(shè)要求

有圖晶圓關(guān)鍵尺寸及套刻量測系統(tǒng)在Mini LED行業(yè)的應(yīng)用 #半導(dǎo)體元器件 #精密測量

印制電路制造者的干膜技術(shù)性能要求

數(shù)字曝光打印技術(shù)

相機(jī)成像不產(chǎn)生拖影的曝光時(shí)間計(jì)算

直接成像數(shù)字曝光技術(shù)介紹

套刻誤差的含義、產(chǎn)生原因以及和對準(zhǔn)誤差的區(qū)別

KLA公司正式推出了Archer 750套刻量測系統(tǒng)

有圖晶圓關(guān)鍵尺寸及套刻量測系統(tǒng)助力半導(dǎo)體產(chǎn)業(yè)發(fā)展

埃瑞微半導(dǎo)體前道套刻設(shè)備總部項(xiàng)目簽約

編碼器刻線數(shù)與精度數(shù)的關(guān)系

MEMS制造領(lǐng)域中光刻Overlay的概念

芯片制造多重曝光中的套刻精度要求

芯片制造多重曝光中的套刻精度要求

評論