文章來源:半導體與物理

原文作者:jjfly686

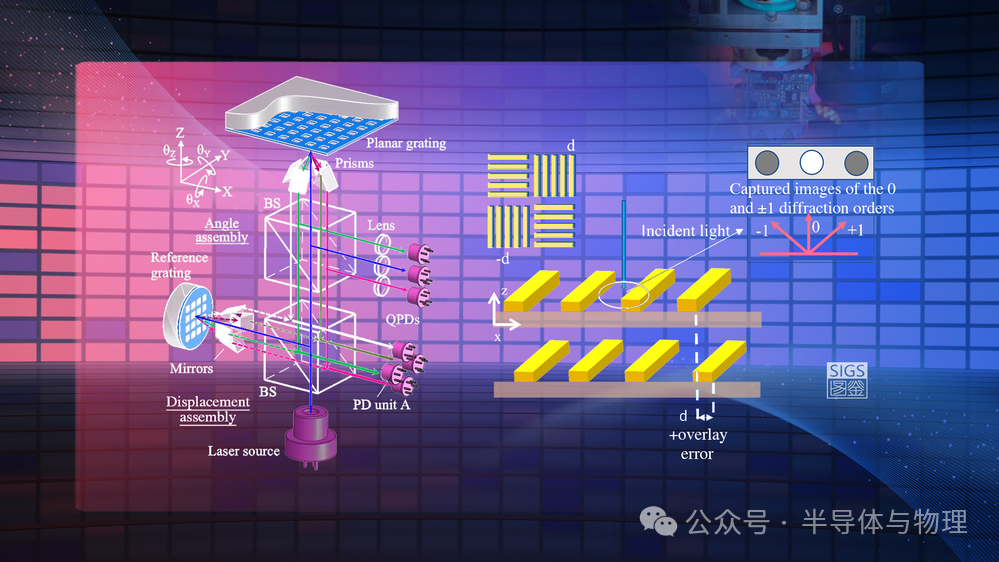

在芯片制造的復雜流程中,光刻工藝是決定晶體管圖案能否精確“印刷”到硅片上的核心環節。而光刻Overlay(套刻精度),則是衡量光刻機將不同層電路圖案對準精度的關鍵指標。簡單來說,它就像建造摩天大樓時每一層的鋼筋骨架能否完美對齊——任何微小的錯位都可能導致整棟建筑的崩塌。在芯片領域,Overlay的誤差會直接影響芯片的良率和性能,甚至決定先進制程的成敗。

什么是光刻Overlay

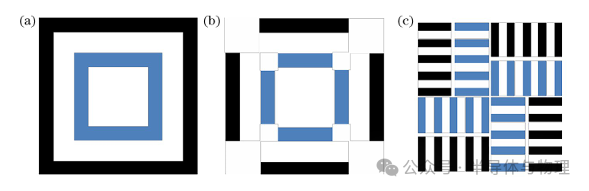

光刻Overlay指的是芯片制造過程中,前后兩次光刻工藝形成的電路圖案之間的對準精度。一顆現代芯片可能包含數十層電路結構(如晶體管層、金屬互聯層、絕緣層等),每一層都需要通過光刻機將設計圖案投射到硅片上。如果相鄰層的圖案無法精準對齊(例如金屬導線未能連接到晶體管觸點),就會導致芯片功能失效。

Overlay誤差的量化通常以納米(nm)為單位。例如,在7nm先進制程中,Overlay誤差需要控制在2nm以內。

Overlay誤差影響芯片制造

1. 良率殺手:電路短路與斷路

Overlay誤差過大會直接導致不同層電路錯位。例如,金屬連線層若未能對準晶體管觸點,可能引發斷路;而相鄰導線若重疊過多,則可能造成短路。據統計,Overlay問題可占高端芯片良率損失的30%以上。

2. 性能波動:晶體管參數失控

在FinFET或GAA(環繞柵極)晶體管中,柵極長度、溝道位置等關鍵參數對Overlay極其敏感。即使幾納米的偏差,也可能導致閾值電壓漂移、漏電流增加,進而影響芯片功耗和頻率。

3. 多層堆疊技術的瓶頸

3D NAND閃存、DRAM堆疊芯片等新型結構需要數十層材料的精確對準。Overlay誤差會引發層間應力不均、信號傳輸失真等問題,嚴重時甚至導致結構開裂。

如何提升光刻Overlay精度

1. 光刻機硬件的極致優化

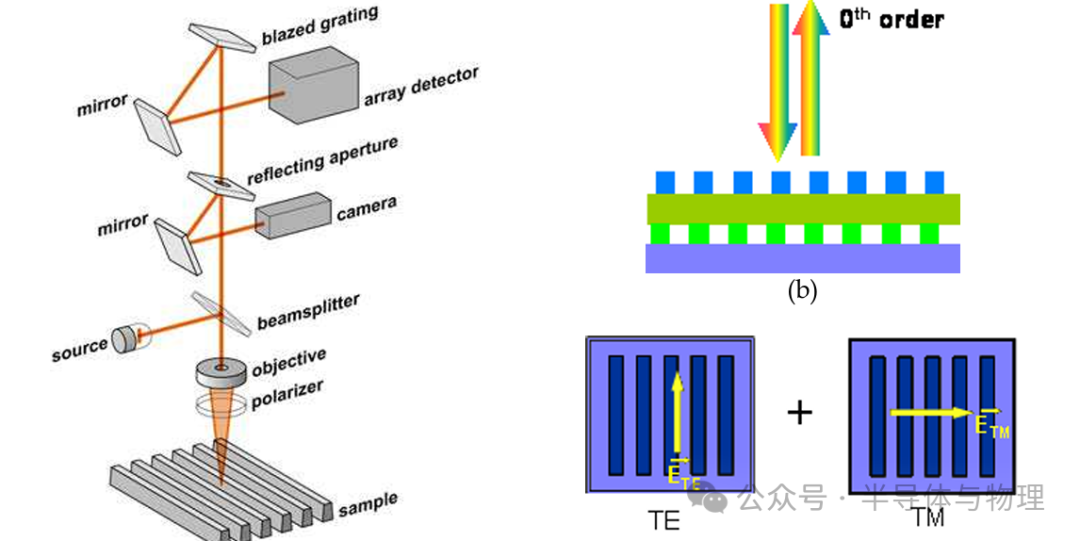

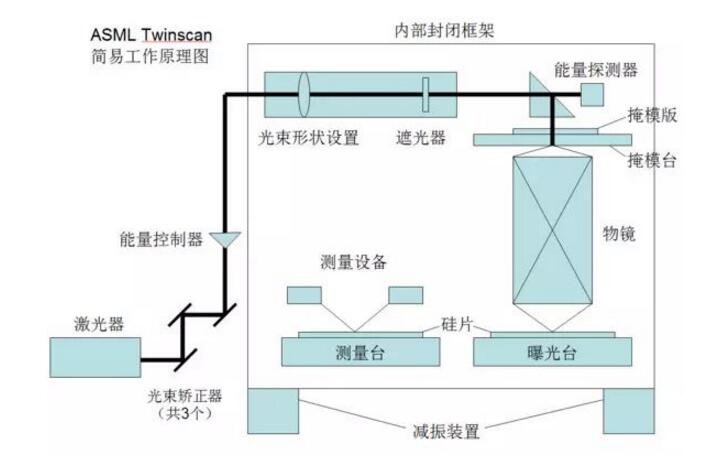

雙工件臺系統:ASML的TWINSCAN技術通過“曝光-測量”雙臺并行,將對準速度提升數倍。

高數值孔徑(NA)物鏡:EUV光刻機通過增大物鏡數值孔徑,提升分辨率和套刻精度。

激光干涉儀與形變補償:實時監測硅片形變并通過機械臂微調,抵消熱膨脹或機械應力導致的位移。

2. 材料與工藝的協同創新

智能光刻膠:開發具有自對準特性的化學放大膠(CAR),利用分子間作用力修正微小偏差。

平坦化工藝(CMP):通過化學機械拋光減少硅片表面起伏,避免高低差導致的聚焦誤差。

應力匹配材料:在多層堆疊中使用熱膨脹系數相近的材料,降低溫度變化引起的層間錯位。

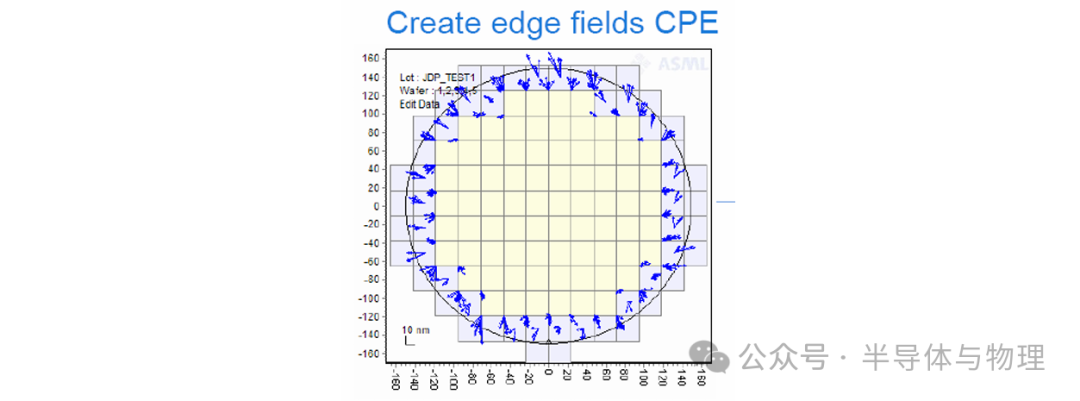

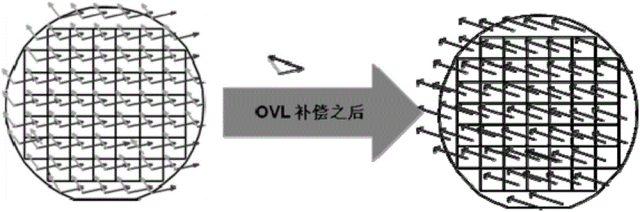

3. 算法與數據的閉環控制

實時反饋系統:每片晶圓曝光后立即測量Overlay數據并反饋調整。

機器學習預測模型:利用歷史數據訓練AI,預判設備狀態變化(如鏡頭熱漂移)并提前補償。

虛擬量測(VM):結合工藝參數模擬Overlay結果,減少物理測量時間。

4. 多重曝光與工藝協同

自對準雙重成像(SADP/SAQP):通過多次曝光和刻蝕組合,分解復雜圖形并提升對準容差。

設計-工藝協同優化(DTCO):在芯片設計階段預留Overlay補償空間,例如采用冗余觸點或彈性布線。

-

晶體管

+關注

關注

77文章

10020瀏覽量

141684 -

芯片制造

+關注

關注

10文章

688瀏覽量

29731 -

光刻工藝

+關注

關注

1文章

36瀏覽量

1979

原文標題:光刻工藝中的Overlay

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

什么是光刻機的套刻精度

什么是光刻機的套刻精度

評論