隨著配電網功能的不斷擴展和升級,傳統的單片機方案已經無法滿足FTU(饋線終端單元)對高性能、多任務處理的需求。多核異構處理器通過集成不同架構的處理核心,能夠同時處理如模擬量采集、保護邏輯運算等實時性要求高的任務,以及如多通信接口管理、加密解密等非實時性交互任務,從而顯著提升FTU的整體性能和處理能力。

1、FET3506J-S核心板在FTU中的適配性

飛凌嵌入式基于瑞芯微RK3506J處理器設計開發的FET3506J-S核心板,采用3*Cortex-A7+1*Cortex-M0的多核異構架構;滿載運行實測功耗僅0.7W,滿載運行且無需任何散熱處理即可應對+85℃的高溫環境;并且有著強大的軟件兼容性和靈活的系統架構,支持Linux 6.1、AMP架構以及Linux RT等多種軟件生態。以上特性使這款FET3506J-S核心板成為了電力FTU理想的主控選型方案,接下來我們展開說說。

01、實時方案: AP 或 MCU

飛凌嵌入式FET3506J-S核心板支持兩種實時方案,即AP+MCU模式和AP+AP模式,兩種模式各有相應的特點,適用于不同的應用領域。

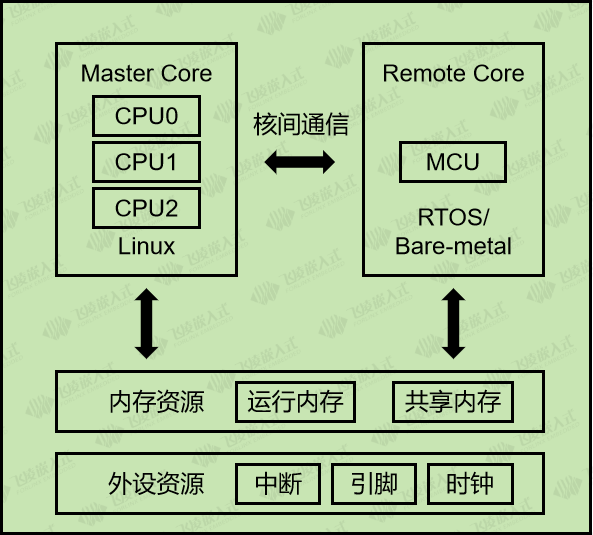

① AP+MCU系統架構

在瑞芯微的多核異構系統中,AP+MCU系統架構為Linux+MCU RTOS/Bare-metal。運行LinuxAP處理器核心作為主核(Master Core)。運行RTOS/Bare-metal的MCU處理器核心作為從核(Remote Core)。主核負責整個多核異構系統中共享資源的劃分和管理,并運行主站服務程序。

但RK3506J實時核(Cortex-M0)的主頻只有200MHz,且無法訪問硬件浮點單元(FPU),在應對復雜實時計算時,計算性能存在顯著瓶頸。適用于一些簡單控制的應用領域。FTU類似的保護測控類產品一般使用AP+AP實時方案。在此背景下,AMP(Asymmetric Multi-Processing)架構已成為主流解決方案。

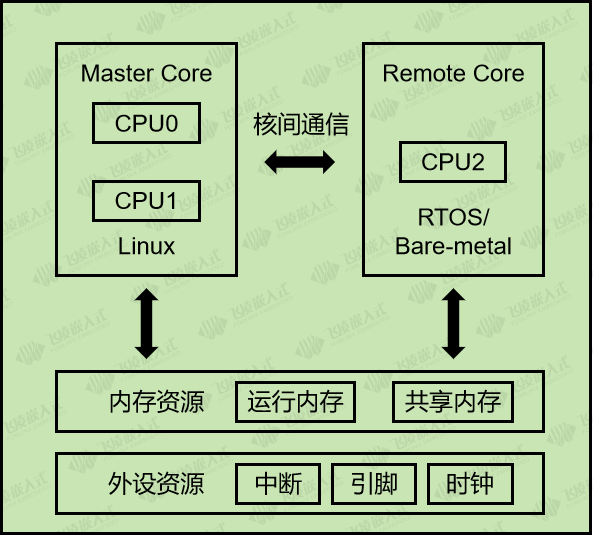

② AP+AP系統架構

在瑞芯微多核異構系統中,AP+AP系統架構為Linux+RTOS/Bare-metal兩種。在Linux+RTOS/Bare-metal系統架構中,運行Linux的處理器核心作為主核(MasterCore)。運行RTOS/Bare-metal 的處理器核心作為從核(Remote Core)。主核負責整個多核異構系統中共享資源的劃分和管理,并運行主站服務程序。

在該方案中,系統將CPU2核心配置為實時核。CPU0和CPU1依舊運行Linux系統,憑借Cortex-A7的1.5GHz高主頻,能調用硬浮點單元加速等特性,在處理諸如高精度采樣、實時計算、故障檢測等對實時性要求嚴苛的任務時,能大幅降低任務響應延遲,提升系統整體的實時處理效能 ,確保系統對關鍵事件的快速響應與穩定運行。

02、實時AP核接口資源

2、FTU方案資源框圖

01、實時A核

北斗定位、實時時鐘、多路模擬量采集、FFT運算、保護邏輯、故障處理及錄波等高實時性任務由實時A核承載。該核心可同步處理多間隔單元的實時業務:通過50MHz SPI總線實現多路AD7616高速采樣,動態配置DDR存儲空間適配不同周期錄波需求,并利用RPMsg雙核通信機制將錄波數據高效傳輸至管理核心生成標準化文件。

02、管理A核

管理A核集成多類型通信接口,可同時完成:

① 傳感器數據協議適配與接入管理;

② 按IEC101/IEC104標準對采集數據進行加密處理,并通過專用通道向調度中心轉發規范報文。雙核通過共享內存與消息隊列實現實時數據流與控制指令的高效交互。

3、應用實例

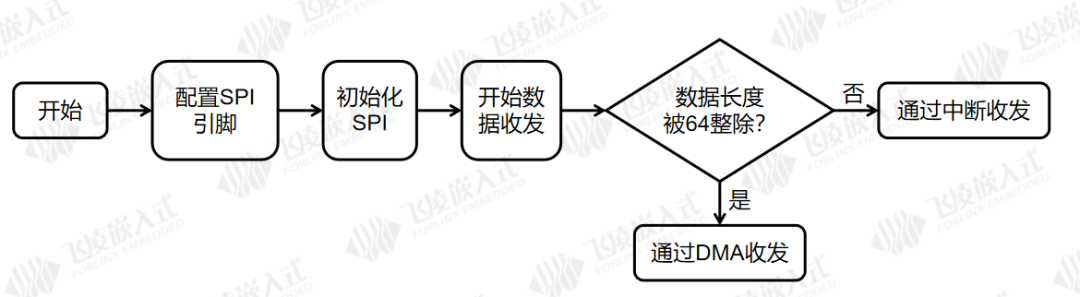

01、SPI數據收發

本案例為SPI回環測試,將SPI的MOSI和MISO兩個引腳短接進行數據收發。

① 功能介紹

② 效果展現

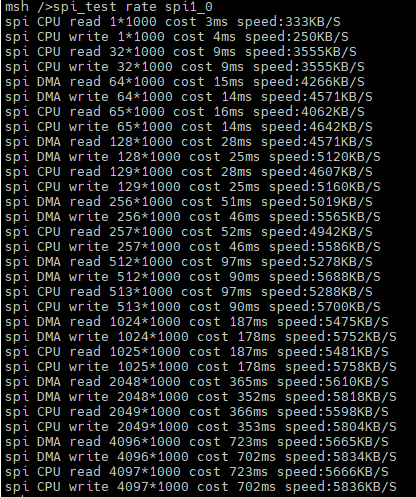

SPI的發送和接收FIFO均為64個,在底層hal庫程序中,當數據長度被64整除時,采用DMA方式,否則采用CPU中斷模式。通過此demo,展示了SPI的中端和DMA兩種使用方法,設置SPI速率為50M全雙工,案例中讀或寫平均傳輸速率為45.59Mbit/s,接近理論帶寬。

傳輸效果:

02、GOOSE

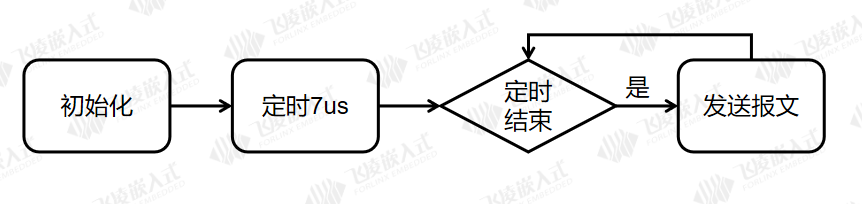

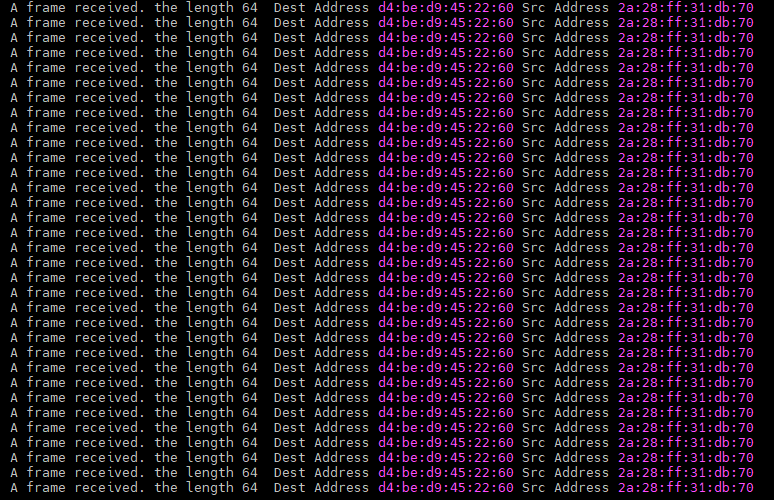

本案例采用GMAC0發送Goose數據包測試。

① 功能介紹

②效果展現

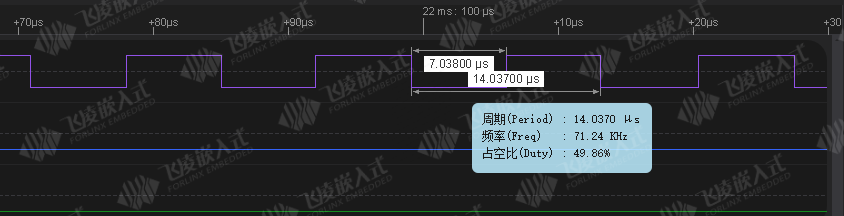

測試方法:采用單片機進行接收,接收完成后將GPIO進行反轉,使用示波器測量GPIO波形。實測64字節數據,用時7μs,接近百兆理論帶寬。

03、核間通信RPMsg

① 標準框架

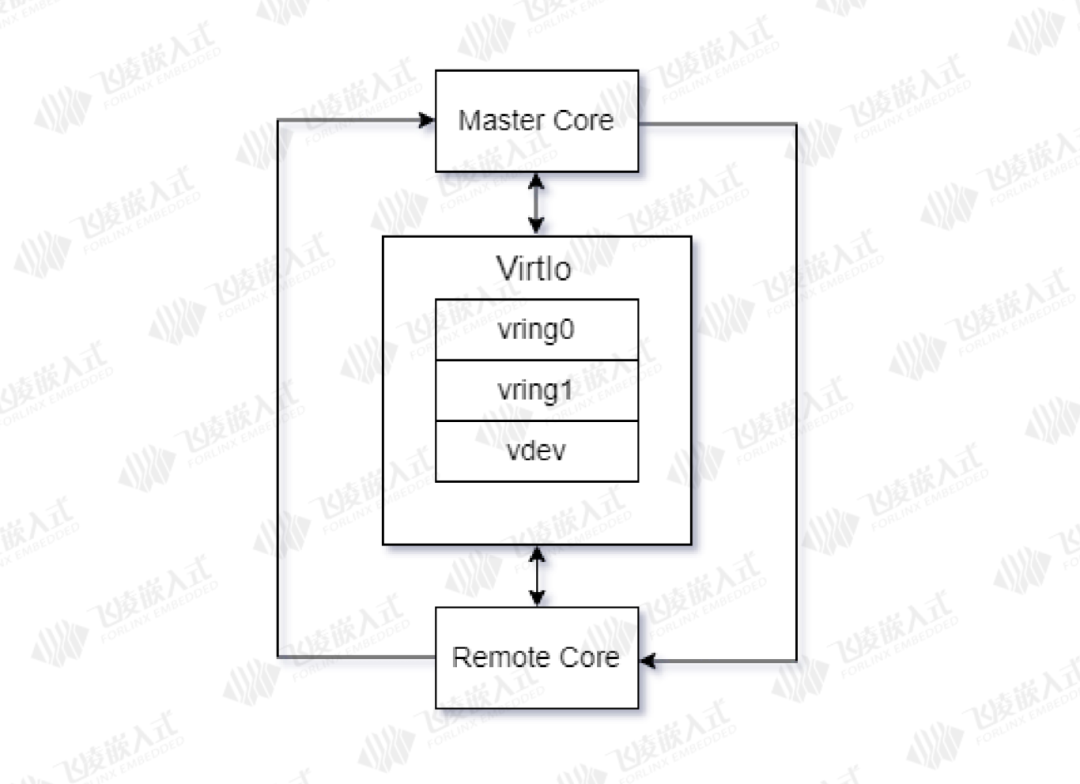

瑞芯微為多核異構系統設計了RPMsg通信框架:Linux內核采用標準RPMsg,RTOS/Bare-metal使用輕量化RPMsg-Lite,作為AMP系統核間通信的標準化二進制接口。

該協議基于VirtIo虛擬化IO架構(同虛擬網卡/虛擬磁盤等技術),通過VirtIo-Ring共享內存機制實現數據傳輸,采用單向vring設計(vring0發數據、vring1收數據)配合vdev-buffer緩沖區。

整體框架由核間中斷及vring0、vring1、vdev-buffer三段共享內存區域構成。

② 通信流程

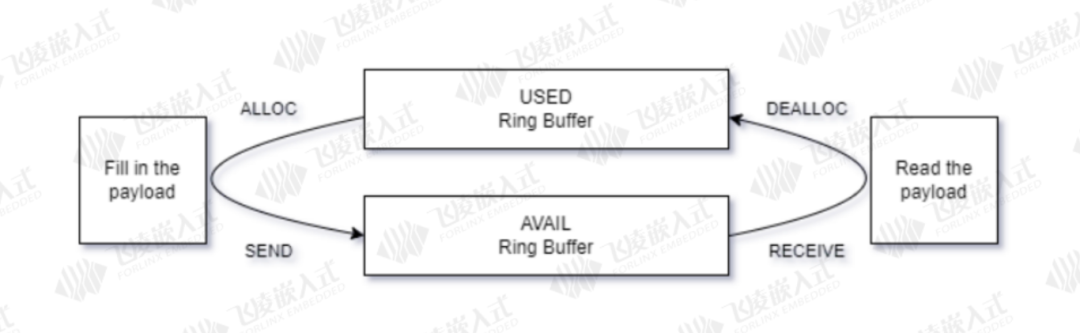

在RPMsg中,主-從核心通過中斷和共享內存的方式進行通信,內存的管理由主核負責,在每個通信方向上都有USED和AVAIL兩個緩沖區,這兩個緩沖區可以按照RPMsg的消息格式分成一塊一塊,由這些內存塊可以鏈接成一個環。

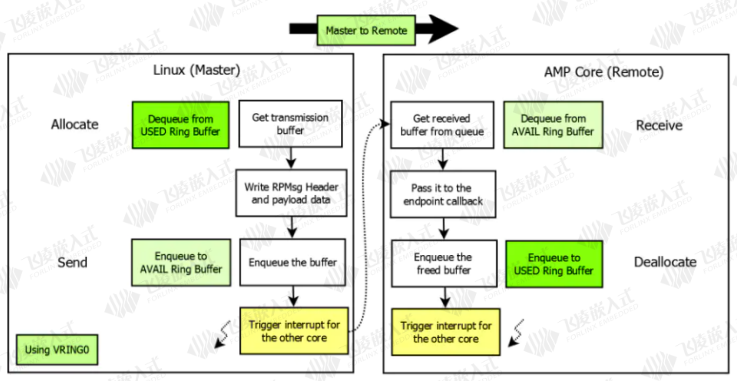

因此當主核(Master Core)和從核(Reomte Core)進行通信時:

1. Master Core發送時,從vring0(USED)中取得一塊 buffer,再將消息按照RPMsg協議填充;

2. 將處理好的內存 buffer 鏈接到 ving1(AVAIL);

3. 觸發中斷通知 Remote Core 有數據處理待處理。

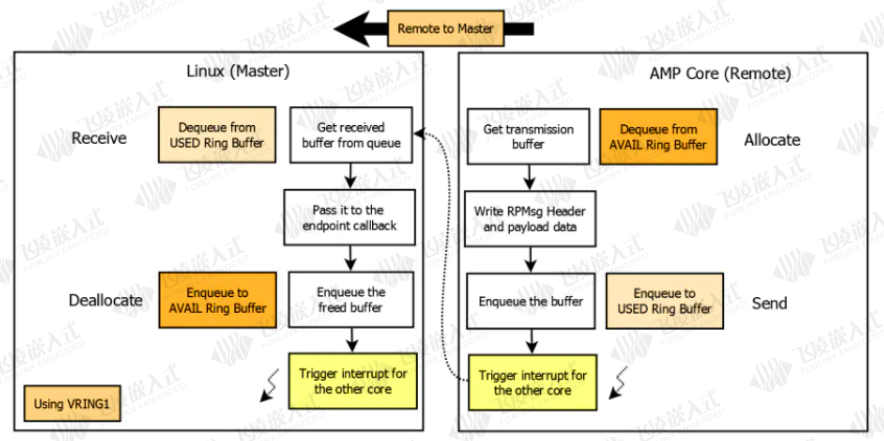

當從核需要和主核進行通信時:

1. 從核根據隊列從 vring1(AVAIL) 中取得一塊 buffer,再將消息按照 RPMsg 協議填充;

2. 將處理好的內存 buffer 鏈接到 ving0(USED);

3. 觸發中斷通知 Master Core 有數據處理待處理。

完成消息傳遞后,釋放使用的 buffer,并等待下一筆數據發送。從核發送時,與主核發送流程相反。通信過程中的共享數據放在 vdev buffer 中。

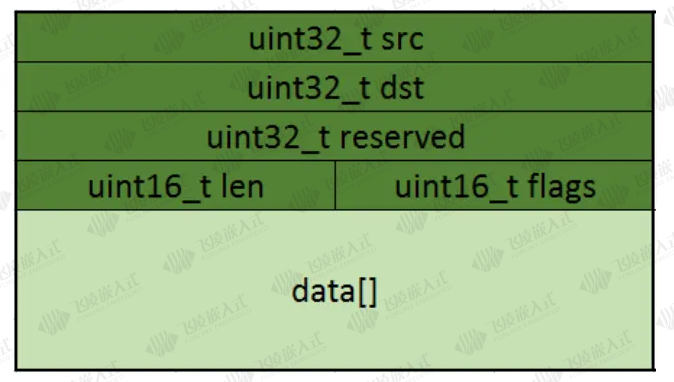

RPMsg 每次發送的最大數據長度取決于 payload 長度,這個長度在SDK中默認為 512 Bytes,由于 RPMsg還帶有16 Bytes的數據頭,因此一次性傳輸的最大數據量為 496 Bytes。

③ 效果展示

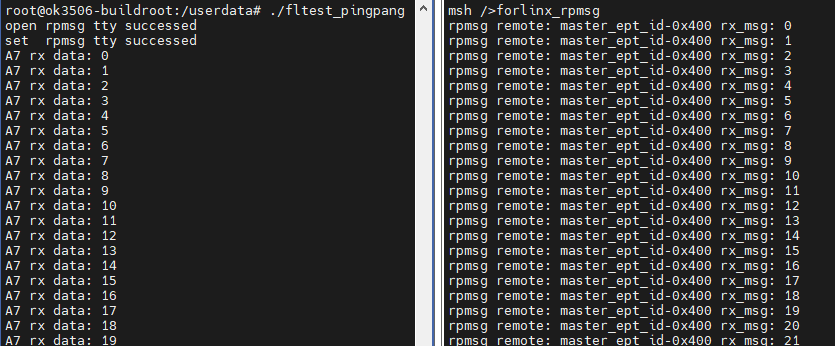

普通傳輸:乒乓示例

大數據傳輸:

在實際使用中采用原始RPMsg框架通信具有一定的局限性,默認單次發送數據最大為496字節,如果傳輸1MB數據,需要發送1024*1024/496=2114次才可傳輸完成;且每次傳輸需要觸發兩次中斷,共計需要觸發4228次中斷,耗時1.05ms,綜合上面兩個因素可知,傳輸1MB數據時間大概為2.2s,且頻繁中斷占用CPU資源較多。

而飛凌嵌入式在RPMsg基礎上優化了大數據傳輸的性能,在FET3506J-S核心板上的具體表現如下所示。傳輸6MB的數據,用時僅111ms,且僅需要觸發4次中斷,大大提高了傳輸效率,減少了對CPU資源的占用。

飛凌嵌入式FET3506J-S核心板在AMP異構多核架構下展現出卓越的通信性能,其雙系統間數據交互速率達到行業領先水平,為電力FTU(饋線終端裝置)應用提供了高效可靠的核心支撐。該板卡采用工業級設計標準,工作溫寬覆蓋-40℃至+85℃嚴苛環境,配備的豐富功能接口(包括多路串口、以太網、CAN總線等)可全面滿足配電自動化終端的多場景接入需求。憑借出色的通信效率、環境適應性和接口擴展能力,FET3506J-S核心板已成為電力FTU設備主控方案的理想選擇,特別適用于對實時性和穩定性要求極高的智能電網應用場景。

-

嵌入式

+關注

關注

5152文章

19675瀏覽量

317558 -

Amp

+關注

關注

0文章

86瀏覽量

47831 -

FTU

+關注

關注

1文章

23瀏覽量

14903 -

雙系統

+關注

關注

0文章

8瀏覽量

6192

發布評論請先 登錄

飛凌嵌入式RK3576核心板的四大優勢詳解

RK3506J行業首發!飛凌嵌入式FET3506J-S核心板亮相2024工博會

米爾瑞芯微多核異構低功耗RK3506核心板重磅發布

飛凌嵌入式FET3576-C核心板四大優勢詳解

RK3506J行業首發!飛凌嵌入式FET3506J-S核心板亮相2024工博會

飛凌嵌入式RK3576核心板已適配Android 14系統

滿載功耗僅0.7W,飛凌嵌入式國產工業級RK3506J開發板上市

米爾基于瑞芯微RK3506核心板開發板

瑞芯微RK3506開發板必備攻略之Qt應用開發手冊(下),觸覺智能工控嵌入式方案商

飛凌嵌入式RK3506核心板AMP雙系統技術應用解析

飛凌嵌入式RK3506核心板AMP雙系統技術應用解析

評論