芯片的設計理念

眾所周知,芯片擁有極為復雜的結構。以英偉達的B200芯片為例,在巴掌大的面積上,塞入了2080億個晶體管。里面的布局,堪稱一個異次元空間級的迷宮。

如此復雜的架構,無論是制造還是設計,都具有極大的難度。早期集成電路剛剛誕生的時候,晶體管的數量并不多,結構也不復雜。所以,基本上都是設計工程師直接在圖紙上繪制電路的物理版圖,然后把版圖送到制造工廠,工廠進行生產。

他們手工繪制的版圖是非常精細的,直接具體到了晶體管的物理層級,包括布局布線等。

隨著集成電路變得越來越復雜,他們仍然采用這種方式,先畫底層細節,然后進行“拼接”,最終組成一個完整的集成電路。這種設計理念,叫做自底向上(Bottom-Up)設計。

英特爾4004芯片的設計圖(1971年)

這里就要說明一下,一顆芯片從設計的角度來看,是分為不同層級的。從上到下,依次是:系統層、RTL層、門級層、晶體管層、布局布線層、掩膜層。

系統層,是最高層,是站在整個宏觀的角度對芯片進行整體設計。RTL層,是寄存器傳輸層(Register Transfer Level)。門級層的“門”,就是門電路。門電路是由晶體管搭建的。掩模,在之前晶圓制造里介紹過,就是光掩模版,是芯片設計的最終產物,是最底層的、最能夠從細節對芯片進行描述的東東。掩模層,是最底層。自底向上(Bottom-Up)設計適用于早期的集成電路和PCB傳統電路。到了上世紀70-80年代,集成電路發展為大規模和超大規模集成電路,晶體管數量超過1萬。此時,再采用自底向上(Bottom-Up)方式就不合適了。于是,自頂向下(Top-Down)的設計理念開始崛起。

簡單來說,就是不再從細節開始入手,而是“先宏觀,再微觀”——先做系統級設計,然后再做RTL級設計(邏輯功能設計)。等上層設計完成后,再進行下層設計(門級層、晶體管層、布局布線層和掩膜層),完善每一個細節。自頂向下(Top-Down)設計理念一直到現在都是主流。對于日益復雜的芯片架構來說,這種方式具有更高的效率、更短的設計周期,以及更低的設計成本。

逐級的設計,伴隨著逐級的仿真驗證,所以,這種設計方式的成功率也很高。

芯片的設計工具

工欲善其事,必先利其器。想要高效進行芯片的設計,當然不能一直依賴于手工作業。上世紀70年代,隨著計算機技術的不斷成熟,芯片設計逐漸從手工設計走向了計算機輔助設計階段,出現了ICCAD(ICComputer Aided Drafting)。

到了80年代,又出現了CAE(Computer Aided Engineering,計算機輔助工程)。CAD專注于產品設計建模與繪圖,而CAE側重于工程仿真與性能優化?。再后來,大名鼎鼎的EDA(Electronic Design Automation,電子設計自動化)誕生了。

EDA技術的演進階段

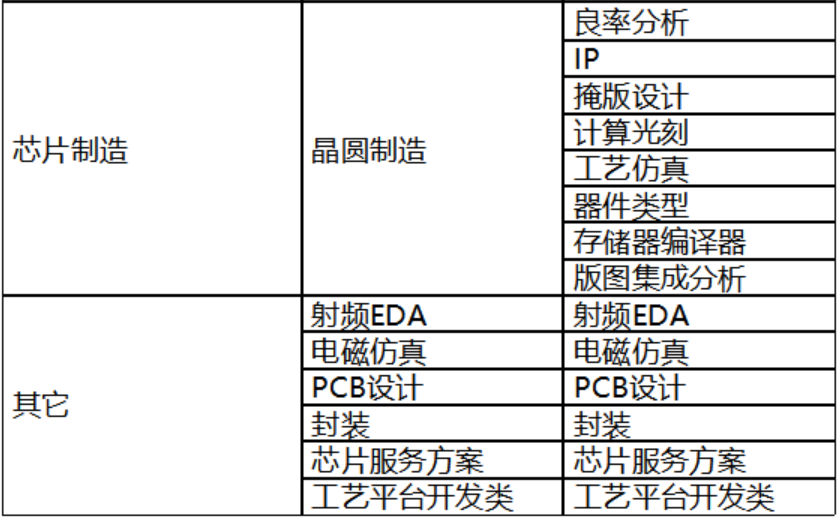

大家需要注意,EDA并不是一個具體的軟件,而是一類軟件的統稱。它不僅僅用于芯片的設計、驗證和仿真,也用于芯片的制造流程。

換言之,EDA貫穿于芯片的整個研發和生產周期,能夠幫助工程師完成大量的細分任務,可以顯著提高設計效率、精度以及成功率。

很多人都知道光刻機,也知道光刻機是我們被“卡脖子”的一個關鍵點。事實上,在EDA方面,我們也是被“卡脖子”的,問題同樣很嚴重。

很多人都知道光刻機,也知道光刻機是我們被“卡脖子”的一個關鍵點。事實上,在EDA方面,我們也是被“卡脖子”的,問題同樣很嚴重。

從全球范圍內來看,處于EDA行業第一梯隊的,就是三家公司——Synopsys(新思科技)、Cadence(鏗騰電子)、Siemens EDA(原Mentor)。

他們都于上世紀80年代創立于美國,目前擁有完整的、全流程的EDA產品體系,市場占有率超過70%,競爭優勢非常明顯。

國內雖然也有華大九天等一些EDA企業,但市場份額較小,和第一梯隊的差距較大。

前幾天傳出新聞,漂亮國那邊又在EDA上搞事,對我們進行封禁。這也是一件麻煩事。

芯片設計的投入成本

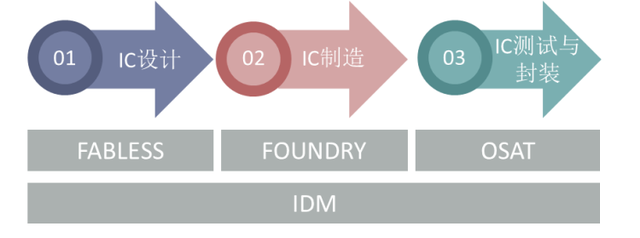

在之前的文章中,小棗君介紹過,芯片的研發和制造有非常明確的分工。

除了極少數公司(IDM,整合元件制造商)設計、制造、封測全都做之外,大部分公司都只做其中一塊(Fabless、Foundry、OSAT),或者是某個更加細分的領域。

國內的很多知名芯片公司,例如華為海思、中興微電子、寒武紀等,都是Fabless(無晶圓芯片設計企業)。小米前兩天發布了自己的手機SoC芯片——玄戒O1。他們也是Fabless,只負責設計,芯片制造還是交給了臺積電(3nm工藝)。芯片設計的難度,由芯片的種類、功能和性能所決定。數字芯片處理數字信號,通常都可以做很大規模,尤其是現在很多CPU、GPU、NPU計算芯片,還有手機SoC芯片,結構都極為復雜,晶體管數量極多,設計難度極大,成本也極為高昂。設計這種高端芯片,往往需要幾百甚至幾千人的專業技術團隊,耗費一年甚至幾年的時間,投入上億甚至上百億美元的資金。芯片工藝制程越先進,成本就越高。

芯片的設計成本估算(單位:美元),僅供參考

成本中,包括了專業人才的薪資(芯片設計人才的薪資很高)、EDA工具的授權費、IP核(待會會提到)的采購費、設備購買費以及運營費用等。

模擬/射頻芯片,處理模擬信號,往往是針對一些具體的功能,規模遠不如剛才說的高端數字芯片。另外還有一些數模混合信號芯片,例如ADC(模數轉換)、DAC(數模轉換),也是針對一些具體應用。這些芯片,大部分相對數字芯片來說簡單一些。

對于較為簡單的芯片,一些中小型團隊,借助目前比較齊全的芯片設計軟件工具平臺(例如EDA)和硬件設備,也能夠進行自主設計。當然,哪怕是簡單的芯片,設計周期大概是1-1.5年,耗費資金在百萬至千萬級。特別值得一提的是,芯片設計具有極高的風險性。如果流片(芯片設計最后要進行流片,相當于做一個測試版)失敗,損失會非常大(28nm單次流片需要1000萬元,7nm需要超過1億美元)。直接經濟損失還只是一方面。流片失敗還會拉長芯片的研發周期,導致錯失市場機遇。嚴重情況下,流片失敗可以直接導致一家公司破產倒閉。

IP核

芯片設計,也是有一些“捷徑”的。例如采用IP核。

IP核,即知識產權核,代表著一種預先定義、經過驗證且可重復使用的模塊化功能單元。它是構建大規模集成電路的基礎元素。

簡單來說,你在設計一個復雜芯片的時候,不必每個部分都從零開始,一些成熟的或通用的功能單元,你就可以直接購買IP核,大幅減少芯片設計的工作量。

手機SoC芯片的設計理念,其實就來自于IP核的復用。

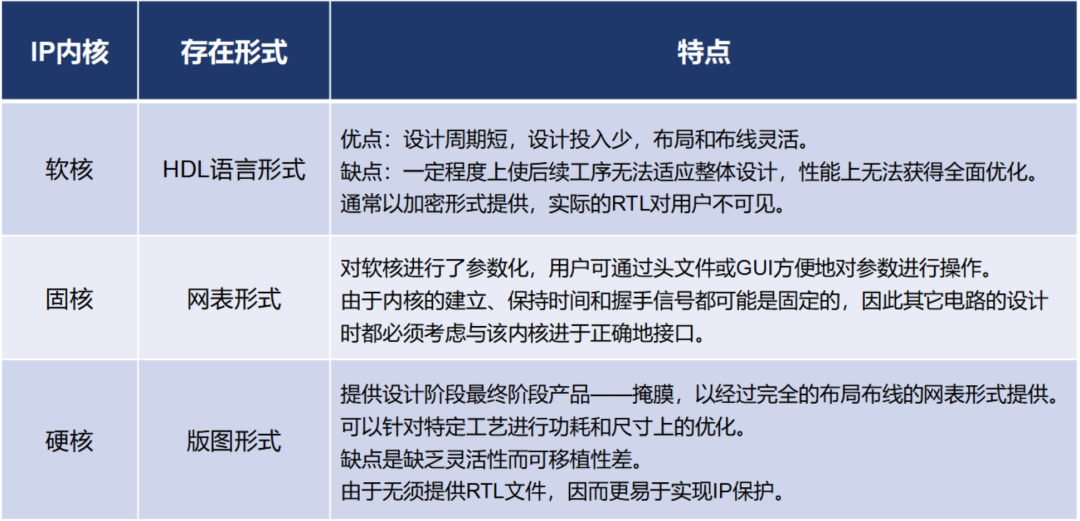

根據特性,IP核可以分為硬核、固核和軟核。具體區別可以參考下面的表格:

目前,芯片IP核的主要市場份額也被歐美企業所占據,其中Arm、Synopsys和Cadence位列市場前三。

大家發現了,Synopsys和Cadence不就是剛才EDA三強的第一和第二嗎?

沒錯,搭配捆綁銷售,軟件授權和IP核授權一起賣,效果更好,利潤更高。

在芯片設計的產業鏈中,上游的EDA工具和IP核授權環節毛利率高達90%以上。然而,這些利潤基本上都被剛才說的那幾家公司所占據。

目前,EDA工具的國產化率尚不足5%,高端IP核仍嚴重依賴進口,形勢真的是不容樂觀。

根據有關機構的數據顯示,2020至2024年間,全球芯片設計市場的復合增長率是9.8%,2024年市場規模突破4800億美元。中國市場的增長更為驚人,占比從19%迅速提升至28%。

隨著整個社會數字化轉型的不斷推進,還有AI浪潮的蓬勃發展,相信包括芯片設計在內的整個芯片產業還會繼續高歌猛進。這其中,蘊藏著巨大的商業機會和挑戰。

文章來源于鮮棗課堂,作者小棗君

-

集成電路

+關注

關注

5420文章

11987瀏覽量

367542 -

芯片設計

+關注

關注

15文章

1074瀏覽量

55510 -

晶體管

+關注

關注

77文章

9994瀏覽量

140936

發布評論請先 登錄

關于芯片設計的一些基本知識

關于芯片設計的一些基本知識

評論