隨著通信速率進入100G、200G乃至400G時代,系統對時鐘源的抖動容限和溫漂性能提出更高要求。FCom富士晶振推出的FCO-L系列差分晶體振蕩器具備50fs級別的超低相位抖動、寬溫高穩等特點,成為光模塊、PCIe Gen6平臺和新一代數據中心的關鍵定時解決方案。

一、在光模塊中的設計應用

應用背景

光模塊(如SFP+/QSFP+/OSFP等)是實現光電轉換的核心器件,通常內建CDR(時鐘數據恢復)和高速SerDes電路,對輸入時鐘的抖動與穩定性極為敏感。

設計要點

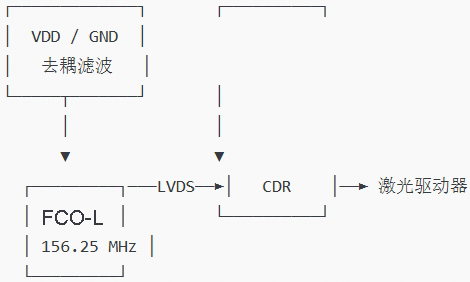

- 推薦輸出:LVPECL或LVDS,兼容CDR輸入;

- 推薦頻率:156.25?MHz(25G NRZ)、625?MHz(25G PAM4)、312.5?MHz(100G)等;

- 關鍵指標:抖動< 100fs RMS(12kHz–20MHz);

- 布線建議:時鐘走線需采用差分對布線,保持長度匹配(<5mil),并嚴格控制阻抗(100Ω±10%);

- 電源管理:建議配置 LDO + π型濾波(0.1μF + 1μF + 4.7μF),降低電源噪聲;

- 共模抑制:接收端建議加共模吸收磁珠,改善EMI表現;

- 晶振位置:靠近 SerDes/Clock Input,減少時鐘路徑長度,避免過孔引起反射;

FCom-光模塊拓撲圖示意

FCom-光模塊拓撲圖示意典型器件搭配

光模塊類型 | 推薦主控/CDR芯片 | 推薦FCO-L頻率 | 應用速率 | |

SFP+ / SFP28 | 156.25 MHz | LVDS | 10G / 25G NRZ | |

QSFP+ / QSFP28 | 312.5 MHz | LVDS / LVPECL | 40G / 100G | |

OSFP / CFP2 / QSFP-DD | Inphi IN3256TA | 625 MHz | LVPECL | 100G / 400G PAM4 |

DWDM Tunable | Semtech GN2217 | 161.1328125 MHz | LVDS | Tunable 10/25G |

光模塊帶 FPGA平臺 | Intel Stratix 10 TX | 156.25/312.5/ 625 MHz | LVDS | 多通道 SerDes同步 |

設計注意事項與調試建議

- 使用差分探頭測試時鐘輸出,確保波形無反射/畸變;

- 在PCB layout中,優先將晶振靠近接收端放置,避免長線回授;

- 若模塊內存在高速DC-DC轉換器,注意振蕩器電源路徑需隔離;

- 多模塊同步建議使用具備±25ppm頻穩的FCO-L,并考慮冗余備份路徑。

二、在PCIe Gen6平臺中的設計要點與器件搭配

應用背景

PCIe Gen6(Peripheral Component Interconnect Express Generation 6)協議支持64 GT/s(Gigatransfers per second)傳輸速率,使用PAM4 編碼,對參考時鐘(Refclk)的抖動要求極為嚴格。相比Gen4/Gen5時代,對時鐘源的噪聲容限、頻率精度、熱穩定性提出了更高要求。

設計要點

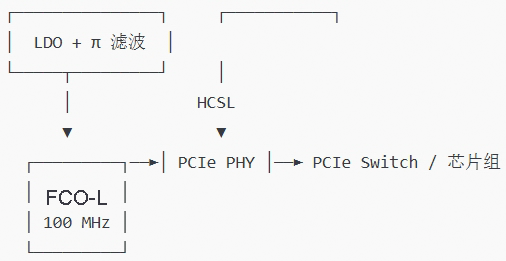

- 推薦頻率:100 MHz(主流PCIe Refclk頻率),200 MHz(部分CXL 2.0平臺使用);

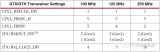

- 輸出接口:HCSL(用于標準PCIe)、LVDS(低功耗替代)、LVPECL(長線驅動);

- 輸出容差要求:抖動需≤ 80 fs RMS(符合PCIe Gen6 jitter budget);

- 供電電壓:支持1.8V、2.5V、3.3V平臺共用,適配多電壓主板設計;

- 布線建議:使用 100Ω 差分對走線,走線長度差<5mil,HCSL需50Ω終端到GND;

- 電源去耦:推薦配置:0.1μF + 1μF 去耦電容;必要時加入π型濾波(磁珠+電容);

- 散熱與穩定性:封裝金屬殼接地,有助于EMI控制;可靠近時鐘Buffer布置,減短路徑;

FCom-PCIe Gen 6 拓撲圖示意

FCom-PCIe Gen 6 拓撲圖示意典型器件搭配

應用平臺 | 核心芯片 / 控制器 | 推薦輸出 | 推薦頻率 | 說明 |

服務器主板 | HCSL | 100 MHz | 主板中心時鐘, 連接至多PCIe槽 | |

加速板卡 | NVIDIA H100/A100、AMD MI300 | HCSL / LVDS | 100 MHz | 通常集成PCIe Switch或橋接器 |

PCIe拓展卡 | Broadcom PEX9700/PEX88000 Switch | LVPECL / LVDS | 100 MHz | 適配多個下游設備,需低抖動 |

CXL 內存模塊 | Micron CXL-DDR5 Expansion Module | LVDS | 200 MHz | CXL標準中定義的 高精度同步頻點 |

高速互連 芯片 | Marvell Alaska、Astera Labs Aries | HCSL / LVDS | 100 MHz | 支持PCIe Gen6和CXL混合鏈路 |

時鐘Buffer/分配器 | Renesas 9ZXL, TI CDCLVC1310 | HCSL / LVPECL | 100 MHz | 布局中心位置, 作為扇出中繼 |

設計注意事項與調試建議

- 在HCSL接口下,輸出端需 50Ω 電阻下拉至 GND;

- 時鐘線應遠離高電流/開關電源軌,避免交叉干擾;

- 使用相鄰地層作為參考面,保持走線阻抗;

- 走線長度盡量短直,減少via(過孔)數量,防止反射;

- 若需熱備份方案,可并聯雙晶振+MUX控制切換,提升可靠性。

三、數據中心中的時鐘挑戰

應用背景

現代數據中心正從傳統架構向高帶寬、低延遲、多協議互連平臺(如PCIe/CXL/以太網)演進。服務器主板、交換芯片、光互連設備之間的協同要求在不同子系統之間實現極高精度的

時鐘同步與相位一致性。

在此類系統中,差分晶體振蕩器承擔著以下關鍵任務:

- 提供高穩定性低抖動主時鐘;

- 驅動 SerDes、PHY、FPGA、網絡芯片的參考時鐘輸入;

- 與時鐘緩沖器(Clock Fan-out)組合,分發至多路下游設備;

- 滿足系統級 散熱、抗干擾、封裝緊湊要求;

設計要點

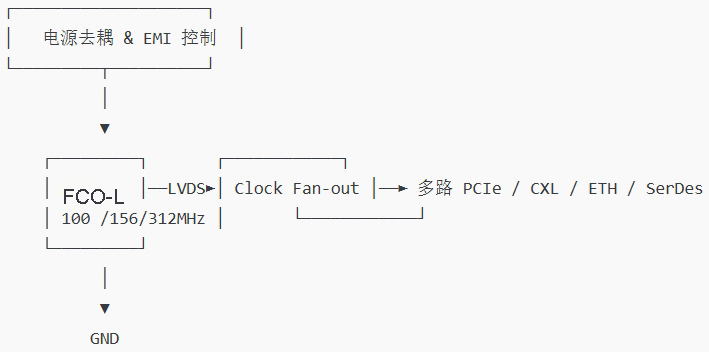

- 推薦頻率:100 MHz(PCIe/CXL平臺的通用標準頻率),156.25MHz(以太網、光模塊、交換芯片),312.5?MHz / 625?MHz(高速CDR、PAM4信號處理、SerDes鏈路);122.88/245.76 MHz(5G與同步通信鏈路)

- 輸出接口:LVDS(交換芯片、CDR、FPGA),HCSL(PCIe/CXL),LVPECL(高速SerDes和后級驅動鏈路)

- 極低抖動性能:< 50 fs RMS(12 kHz–20 MHz),滿足SerDes/CDR抖動容限;

- 差分布線:采用100Ω差分對布線,布線長度誤差<5mil,避免途經大電流區域;

- 電源去耦設計:在VDD端布設0.1μF+1μF并聯去耦,必要時引入π型磁珠濾波;

- 靠近負載布置:建議將振蕩器放置于FPGA、SerDes或CDR芯片附近,避免過長走線;

- EMI控制:保證地層完整、避免走線跨區域;輸出對加終端匹配或共模電感;

- 熱管理:貼近銅泊區布置,利于熱量釋放,推薦使用金屬殼接地處理設計;

FCom-數據中心拓撲圖示意

FCom-數據中心拓撲圖示意典型器件搭配

應用場景 | 核心芯片 / 組件 | 推薦頻率 | 輸出接口 | 應用說明 |

交換芯片 主板 | Broadcom Tomahawk5 | 156.25 MHz | LVDS / HCSL | 為核心交換芯片提供高精度Refclk |

AI加速平臺 / GPU主板 | NVIDIA H100/A100 | 100 / 156.25 MHz | HCSL / LVPECL | 驅動PCIe時鐘、CXL接口與高速SerDes |

服務器主板時鐘系統 | Intel Tofino2/3 | 100 MHz | HCSL | 與時鐘分配器搭配驅動全板PCIe/CXL |

高速光接口模塊 | Semtech GN2110 / Inphi CDR芯片 | 312.5 / 625 MHz | LVDS | 為QSFP-DD等光互聯系統提供CDR參考時鐘 |

高速存儲 主控 | Marvell Bravera、Microchip Switchtec | 100 MHz | HCSL | 驅動NVMe-SAN或互聯Switch |

設計注意事項與調試建議

- 使用100Ω差分對(LVDS/LVPECL)或50Ω單端對地(HCSL);

- 線寬與線距需嚴格控制,推薦使用專用差分線規則;

- 差分走線需長度匹配,差值< 5 mil(0.127mm),避免產生共模噪聲;

- 時鐘線遠離高頻切換電源、DRAM/SoC高速信號區域,避免串擾;

- 差分線優先避免過多via(過孔),可在必要處使用 GSSG 結構保證阻抗連續性;

- 電源波動可能引起周期抖動,建議在VDD端布設0.1μF + 1μF并聯去耦電容,并使用 LDO 或 π型濾波抑制干擾;

- 用示波器查看差分波形幅度、對稱性;確認 Rise/Fall 時間是否符合要求(典型 <1ns);

總結

FCO-L系列作為跨速率、跨協議、跨平臺的微型差分時鐘解決方案,其靈活性、低抖動、高集成度使其在以上三大關鍵模塊中均可深度集成。

-

數據中心

+關注

關注

16文章

5170瀏覽量

73276 -

PCIe

+關注

關注

16文章

1329瀏覽量

84821 -

光模塊

+關注

關注

80文章

1397瀏覽量

60123 -

差分晶振

+關注

關注

0文章

136瀏覽量

594

發布評論請先 登錄

瑞薩電子推出符合PCIe Gen6標準的時鐘緩沖器和多路復用器

FCO-L差分振蕩器搭建時鐘架構,全面剖析光模塊與PCIe Gen6的時鐘設計思路

FCO-L差分振蕩器搭建時鐘架構,全面剖析光模塊與PCIe Gen6的時鐘設計思路

評論