聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

asic

+關注

關注

34文章

1244瀏覽量

122117 -

賽靈思

+關注

關注

33文章

1797瀏覽量

132170 -

時鐘

+關注

關注

11文章

1887瀏覽量

132939

發布評論請先 登錄

相關推薦

熱點推薦

FCO-L差分振蕩器搭建時鐘架構,全面剖析光模塊與PCIe Gen6的時鐘設計思路

隨著通信速率進入100G、200G乃至400G時代,系統對時鐘源的抖動容限和溫漂性能提出更高要求。FCom富士晶振推出的FCO-L系列差分晶體振蕩器具備50fs級別的超低相位抖動、寬溫高穩等特點,成為光模塊、PCIe Gen6平臺和新一代數據中心的關鍵定時解決方案。

Xilinx Ultrascale系列FPGA的時鐘資源與架構解析

。Ultrascale+采用16ns,有3個系列:Artix,Kintex,Virtex。不僅是工藝制程方面,在其他方面也存在較大改進,如時鐘資源與架構,本文將重點介紹Ultrascale

AD9253對時鐘抖動的要求怎么樣,應該選擇怎樣的時鐘架構?

1:這款芯片支持連續采樣、沿觸發和外觸發工作方式

2:時鐘必須使用時鐘芯片配置才行?使用有源晶振是否可以?

3:這款芯片對時鐘抖動的要求怎么樣,應該選擇怎樣的時鐘架構?

發表于 04-15 06:43

CPLD 與 ASIC 的比較

在數字電子領域,CPLD和ASIC是兩種廣泛使用的集成電路技術。它們各自有著獨特的優勢和局限性,適用于不同的應用場景。 1. 定義與基本原理 1.1 CPLD(復雜可編程邏輯器件) CPLD是一種

微服務容器化部署好處多嗎?

微服務容器化部署好處有很多,包括環境一致性、資源高效利用、快速部署與啟動、隔離性與安全性、版本控制與回滾以及持續集成與持續部署。這些優勢助力應用可靠穩定運行,提升開發運維效率,是現代軟件架構的優質選擇。UU云小編認為微服務容器化部署好處

ASIC和GPU的原理和優勢

? 本文介紹了ASIC和GPU兩種能夠用于AI計算的半導體芯片各自的原理和優勢。 ASIC和GPU是什么 ASIC和GPU,都是用于計算功能的半導體芯片。因為都可以用于AI計算,所以也被稱為“AI

Verilog 與 ASIC 設計的關系 Verilog 代碼優化技巧

Verilog與ASIC設計的關系 Verilog作為一種硬件描述語言(HDL),在ASIC設計中扮演著至關重要的角色。ASIC(Application Specific Integrated

時序約束一主時鐘與生成時鐘

的輸出,對于Ultrascale和Ultrascale+系列的器件,定時器會自動地接入到GT的輸出。 1.2 約束設置格式 主時鐘約束使用命令create_clock進行創建,進入Timing

ASIC集成電路在人工智能中的應用

ASIC(Application-Specific Integrated Circuit)集成電路在人工智能領域的應用日益廣泛,其專為特定應用而設計的特點使得它在處理人工智能任務時能夠展現出卓越

ASIC集成電路如何提高系統效率

在現代電子系統中,效率和性能是衡量一個系統優劣的關鍵指標。隨著技術的發展,ASIC集成電路因其高度定制化和優化的特性,在提高系統效率方面發揮著越來越重要的作用。 ASIC的定義和特點 ASIC是一種

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件

架構的 Mali-400 MP2 圖形處理單元。該套件的 ZCU102 板支持所有主要外設和接口,支持許多應用的開發。 特征 針對使用 Zynq Ultrascale+ MPSoC 的快速應用原型設計進行了優化 DDR4 SODIMM – 4GB 64 位,帶 ECC 連

自動駕駛三大主流芯片架構分析

當前主流的AI芯片主要分為三類,GPU、FPGA、ASIC。GPU、FPGA均是前期較為成熟的芯片架構,屬于通用型芯片。ASIC屬于為AI特定場景定制的芯片。行業內已經確認CPU不適用于AI計算

恩智浦MCU解讀 MCX A系列微處理器之時鐘架構

全新的MCX A系列融合了恩智浦通用MCU的特點,適用更為廣泛的通用應用,實現了低成本,低功耗,高安全性和高可靠性。 今天,大家一起來了解一下MCX A最新產品的時鐘架構: MCXA153是MCX

發表于 06-20 09:21

?920次閱讀

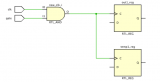

新UltraScale ASIC時鐘架構的使用及好處

新UltraScale ASIC時鐘架構的使用及好處

評論