在長期服務(wù)于用戶AI訓(xùn)練/推理生產(chǎn)網(wǎng)絡(luò)的實(shí)踐中,我們深刻觀察到傳統(tǒng)靜態(tài)或簡單度量(如跳數(shù))的選路策略難以滿足高性能AI集群網(wǎng)絡(luò)的嚴(yán)苛要求。AI工作負(fù)載,特別是涉及大規(guī)模參數(shù)同步(如All-Reduce操作)和RDMA(如RoCEv2)流量時(shí),對網(wǎng)絡(luò)的帶寬可用性、低延遲和極低抖動有著近乎極致的需求。

網(wǎng)絡(luò)路徑上的微小波動,如短暫擁塞導(dǎo)致的隊(duì)列積壓或轉(zhuǎn)發(fā)延遲增加,都可能顯著拖慢整個(gè)訓(xùn)練作業(yè)的完成時(shí)間,造成昂貴的算力資源浪費(fèi)。

智能選路的路徑質(zhì)量如何判定?

為了從根本上優(yōu)化AI流量的傳輸效率并最大化集群利用率,我們設(shè)計(jì)并實(shí)踐了基于多維度網(wǎng)絡(luò)狀態(tài)感知的動態(tài)智能選路技術(shù)。該技術(shù)的核心創(chuàng)新在于,聚焦關(guān)鍵影響因子,摒棄單一指標(biāo),精準(zhǔn)識別并引入在AI集群網(wǎng)絡(luò)環(huán)境中對性能影響最為顯著的動態(tài)參數(shù)作為核心計(jì)算因子:

- 實(shí)時(shí)帶寬利用率:精確測量路徑上關(guān)鍵鏈路的當(dāng)前可用帶寬。避免將高吞吐量的AI流量(如梯度同步)引導(dǎo)至已接近飽和的鏈路,防止擁塞崩潰和PFC反壓風(fēng)暴。

- 隊(duì)列深度/使用情況: 直接監(jiān)控網(wǎng)絡(luò)設(shè)備(交換機(jī))出口隊(duì)列的瞬時(shí)和平均深度。隊(duì)列深度是擁塞的先行指標(biāo),深度過大意味著數(shù)據(jù)包排隊(duì)等待時(shí)間(Bufferbloat)增加,直接導(dǎo)致傳輸延遲上升和抖動加劇,這對依賴確定性的RDMA和集合通信操作是致命的。

- 轉(zhuǎn)發(fā)時(shí)延/延遲變化: 不僅測量路徑的基礎(chǔ)傳播延遲,更關(guān)鍵的是持續(xù)監(jiān)測數(shù)據(jù)包轉(zhuǎn)發(fā)處理延遲及其變化(抖動)。這反映了設(shè)備本身的處理能力和當(dāng)前負(fù)載狀態(tài),高或波動的處理時(shí)延會破壞AI流量的同步性。

智能選路中的統(tǒng)計(jì)計(jì)數(shù):ASIC賦能的高精度數(shù)據(jù)采集

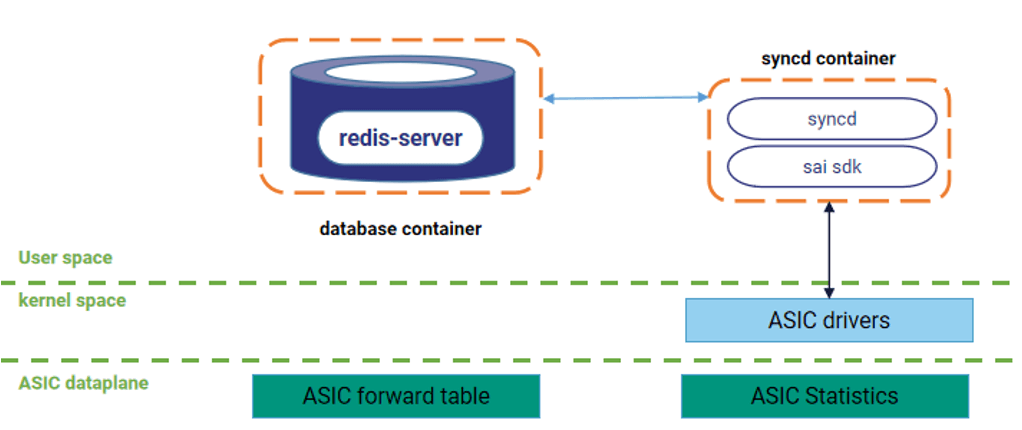

在動態(tài)智能選路系統(tǒng)的實(shí)現(xiàn)中,帶寬利用率與隊(duì)列深度這兩大關(guān)鍵指標(biāo)的采集直接依賴于網(wǎng)絡(luò)設(shè)備的ASIC硬件級能力。具體而言:

硬件級實(shí)時(shí)監(jiān)測(百毫秒級精度)

ASIC芯片內(nèi)置的硬件寄存器持續(xù)執(zhí)行線速統(tǒng)計(jì),對每個(gè)端口的字節(jié)轉(zhuǎn)發(fā)計(jì)數(shù)(Byte Counter) 和各優(yōu)先級隊(duì)列的緩存占用計(jì)數(shù)(Queue Depth Counter) 進(jìn)行原子級累加。這種基于硅片級電路的計(jì)數(shù)機(jī)制擺脫了軟件輪詢的延遲與性能開銷,可實(shí)現(xiàn)百毫秒級精度的數(shù)據(jù)捕獲,精準(zhǔn)反映瞬時(shí)網(wǎng)絡(luò)擁塞狀態(tài)。

控制面高效采集(亞秒級同步)

運(yùn)行于設(shè)備控制面的SONiC網(wǎng)絡(luò)操作系統(tǒng),通過標(biāo)準(zhǔn)化的SAI(Switch Abstraction Interface)接口以亞秒級周期(通常為500ms) 主動讀取ASIC寄存器的統(tǒng)計(jì)快照。此設(shè)計(jì)確保控制面能夠近乎實(shí)時(shí)地感知轉(zhuǎn)發(fā)芯片的狀態(tài)變化,為動態(tài)選路提供高時(shí)效性數(shù)據(jù)輸入。

流水線式數(shù)據(jù)處理與存儲

采集的原始計(jì)數(shù)器數(shù)據(jù)通過以下高效流水線處理:

- ① 增量計(jì)算:SAI層將本次讀數(shù)與上次讀數(shù)做差,計(jì)算出時(shí)間窗口內(nèi)的實(shí)際流量增量(ΔBytes)與隊(duì)列深度變化值(ΔQueue-Occupancy)。

- ② Redis高速緩存:處理后的增量數(shù)據(jù)被寫入內(nèi)存數(shù)據(jù)庫Redis的時(shí)序結(jié)構(gòu)(TSDB)中,形成帶時(shí)間戳的指標(biāo)序列。此架構(gòu)滿足高吞吐、低延遲的數(shù)據(jù)存取需求,為后續(xù)分析提供支撐。

BGP宣告的優(yōu)化設(shè)計(jì)(秒級間隔)?

若按ASIC的亞秒級精度(如每100ms)通過BGP宣告路徑質(zhì)量,會導(dǎo)致控制面壓力劇增,頻繁生成和傳輸BGP Update消息,占用CPU和帶寬資源。微秒級變化也可能觸發(fā)不必要的路由更新,影響網(wǎng)絡(luò)穩(wěn)定性。所以,采用秒級間隔?(例如每秒1次)向鄰居發(fā)送BGP Update消息,攜帶加權(quán)平均后的路徑質(zhì)量值。路徑質(zhì)量通過BGP擴(kuò)展社區(qū)屬性?(如Path Bandwidth Extended Community)傳遞,格式為浮點(diǎn)數(shù)(單位Gb/s)

納秒級時(shí)延測量:INT與HDC技術(shù)負(fù)載均衡中的深度應(yīng)用

轉(zhuǎn)發(fā)時(shí)延計(jì)算因子基于INT(In-band Network Telemetry)技術(shù),精度可達(dá)納秒級。HDC(High Delay Capture)是一種能捕獲ASIC中經(jīng)歷高延遲的數(shù)據(jù)包信息的INT技術(shù)。

INT硬件流水線實(shí)現(xiàn)原理

數(shù)據(jù)包進(jìn)入交換機(jī)ASIC時(shí),入口流水線在包頭插入INT Shim頭部,并記錄精確入端口時(shí)間戳(基于芯片級高精度時(shí)鐘,分辨率達(dá)納秒級)。轉(zhuǎn)發(fā)過程中,每個(gè)流水線階段(如Ingress/Egress隊(duì)列)實(shí)時(shí)追加時(shí)延元數(shù)據(jù)。包離開出口隊(duì)列時(shí),ASIC計(jì)算,此設(shè)計(jì)消除了交換機(jī)基礎(chǔ)轉(zhuǎn)發(fā)延遲的影響,僅保留隊(duì)列排隊(duì)時(shí)延這一關(guān)鍵變量。

HDC(高延遲捕獲)技術(shù)深度解析

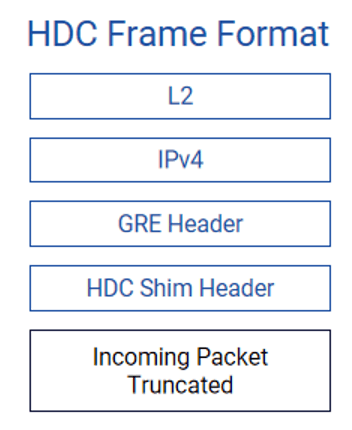

HDC是INT的功能擴(kuò)展,專為捕捉網(wǎng)絡(luò)中的尾延遲(Tail Latency) 事件設(shè)計(jì)。只捕獲超過用戶預(yù)設(shè)閾值(如10μs)的異常延遲報(bào)文,實(shí)現(xiàn)靶向抓包而非全量監(jiān)控。ASIC硬件實(shí)時(shí)比對報(bào)文時(shí)延與閾值——當(dāng)報(bào)文在隊(duì)列/緩存中的滯留時(shí)間超過閾值,立即觸發(fā)抓取動作。并將原始數(shù)據(jù)包的前150字節(jié)連同INT元數(shù)據(jù)(包含出入端口、時(shí)延等關(guān)鍵信息)作為HDC數(shù)據(jù)包發(fā)送到收集器。

動態(tài)閾值觸發(fā)機(jī)制

- 用戶可基于業(yè)務(wù)需求設(shè)置多級延遲閾值(如:關(guān)鍵RDMA流:>5μs、普通TCP流:>50μs)

- ASIC硬件實(shí)時(shí)比對每個(gè)包的實(shí)際隊(duì)列時(shí)延與閾值,觸發(fā)零拷貝抓包。

元數(shù)據(jù)結(jié)構(gòu)化封裝

HDC告警包包含兩類關(guān)鍵信息:

- 原始包摘要:截取L2-L4層頭部(150字節(jié)),保留五元組、TCP標(biāo)志位等特征

- INT元數(shù)據(jù):

{ "ingress_port": "Ethernet1/1", "egress_port": "Ethernet1/2", "queue_id": 3, // 擁塞隊(duì)列ID "queue_depth": 16384, // 觸發(fā)時(shí)隊(duì)列深度(Bytes) "latency": 8.7, // 實(shí)測時(shí)延(μs) "timestamp": 1717501234567890 // 納秒級時(shí)間戳 }

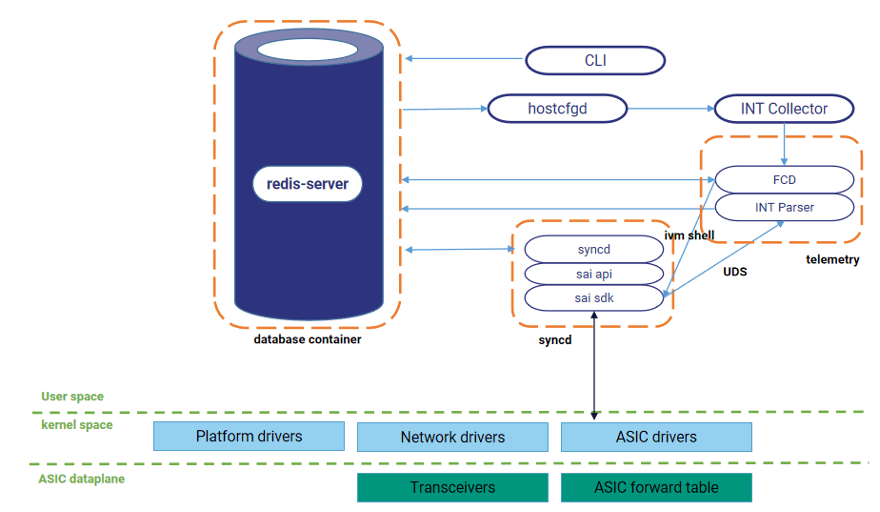

落地實(shí)踐:AI RoCE交換機(jī)上的智能選路

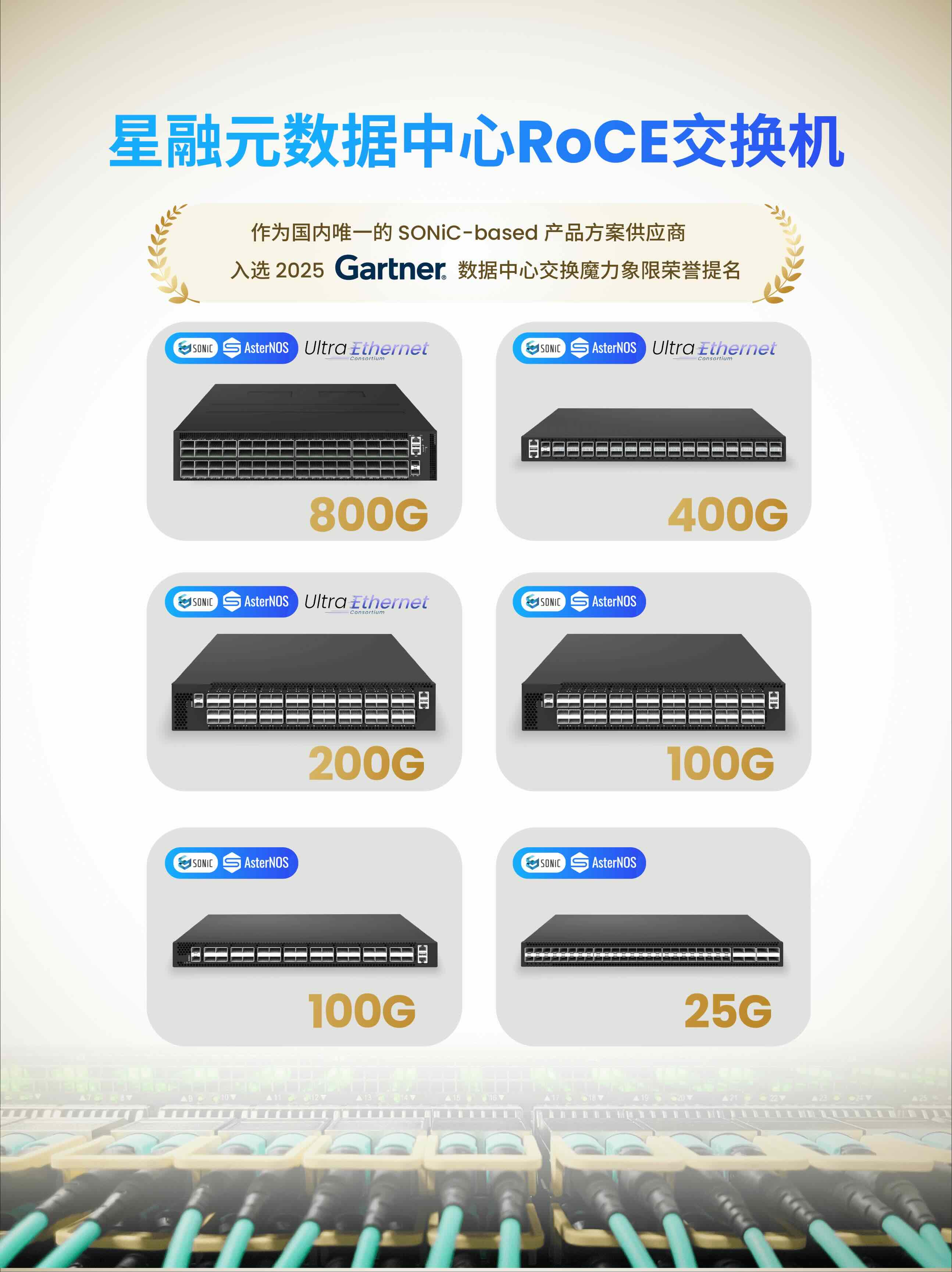

動態(tài)智能選路技術(shù)在星融元交換機(jī)上開啟HDC功能,并將CPU作為HDC的收集分析器,通過分析HDC報(bào)文實(shí)現(xiàn)高精度測量交換機(jī)轉(zhuǎn)發(fā)時(shí)延,并將時(shí)延信息作為路徑質(zhì)量評價(jià)因子,提高路徑質(zhì)量評價(jià)精度。

命令行配置HDC功能控制INT進(jìn)程運(yùn)行,之后通過socket連接進(jìn)行收包循環(huán),將收取到的報(bào)文進(jìn)行解析并將關(guān)鍵信息(出入端口、轉(zhuǎn)發(fā)時(shí)延等)寫入數(shù)據(jù)庫。

【參考文檔】

動態(tài)感知+智能決策,一文解讀 AI 場景組網(wǎng)下的動態(tài)智能選路技術(shù)

BGP在數(shù)據(jù)中心的應(yīng)用2——BGP如何適應(yīng)數(shù)據(jù)中心網(wǎng)絡(luò)_bgp bestpath as-path multipath-relax-CSDN博客

-

網(wǎng)絡(luò)

+關(guān)注

關(guān)注

14文章

7815瀏覽量

90989 -

AI

+關(guān)注

關(guān)注

88文章

35168瀏覽量

280185 -

負(fù)載均衡

+關(guān)注

關(guān)注

0文章

122瀏覽量

12612

發(fā)布評論請先 登錄

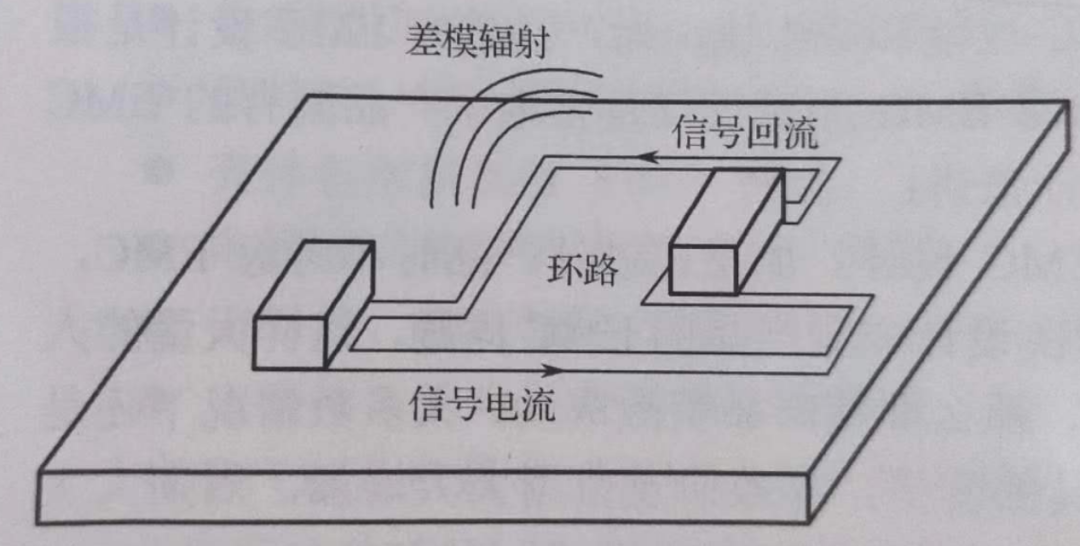

EMC三要素中的耦合路徑

智算網(wǎng)絡(luò)路徑質(zhì)量三要素:帶寬/隊(duì)列/時(shí)延在智能選路中的協(xié)同優(yōu)化

智算網(wǎng)絡(luò)路徑質(zhì)量三要素:帶寬/隊(duì)列/時(shí)延在智能選路中的協(xié)同優(yōu)化

評論