現有的晶體管都是基于 PN 結或肖特基勢壘結而構建的。在未來的幾年里,隨著CMOS制造技術的進步,器件的溝道長度將小于 10nm。在這么短的距離內,為使器件能夠工作,將采用非常高的摻雜濃度梯度。進入納米領域,常規 CMOS 器件所面臨的許多問題都與PN結相關。傳統的按比例縮小將不再繼續通過制造更小的晶體管而達到器件性能的提高。半導體工業界正努力從器件幾何形狀、結構以及材料方面尋求新的解決方案。無結場效應器件有可能成為適用于 10nm及以下技術節點乃至按比例縮小的終極器件。無結場效應晶體管與傳統反型模式 MOS晶體管或其他結型晶體管相比有以下優點:①它們與常規CMOS工藝兼容、易于制作;②它們沒有源漏PN 結;③短溝道效應大為減弱;④由于避開了半導體/柵絕緣層粗糙界面對載流子的散射,載流子受到界面散射影響有限,遷移率不會降低;⑤由于避開了粗糙表面對載流子的散射,器件具備優異的抗噪聲能力;⑥放寬了對降低柵極介電層厚度的嚴格要求;⑦無結場效應晶體管屬于多數載流子導電器件,靠近漏極的電場強度比常規反型溝道的MOS 晶體管要低,因此,器件的性能及可靠性得以提高。一些取代硅作為候選溝道材料(包括鍺硅、鍺、III-V 族化合物半導體、碳納米管、石墨烯以及 MoS2等二維材料)在積極的探索與研究當中,甚至真空溝道也在考慮之列。這一新領域有望突破摩爾定律的藩禽,改變微電子學的面貌。新的后 CMOS 器件需要集成這些異質半導體或其他高遷移率溝道材料在硅襯底上。集成電路器件工藝與材料學家和工程師們要緊密合作,共同迎接未來新的挑戰。

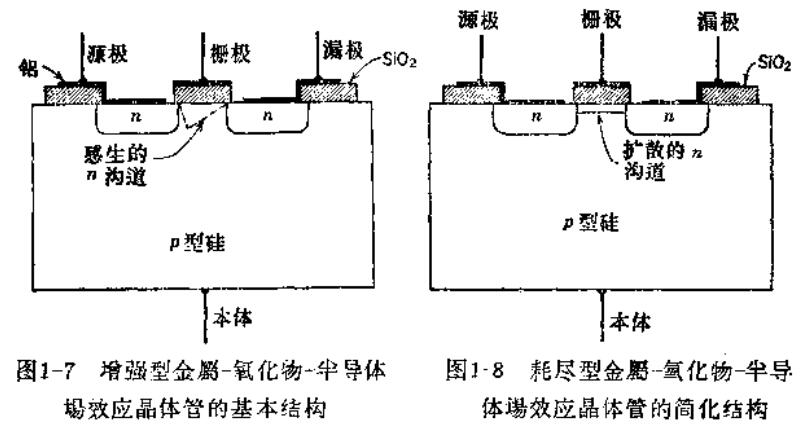

常規的 CMOS 晶體管,從源區至溝道和漏區由兩個背靠背的PN 結組成,溝道的摻雜類型與其漏極與源極相反。當足夠大的電位差施于柵極與源極之間時,電場會在柵氧化層下方的半導體表面感應少子電荷,形成反型溝道;這時溝道的導電類型與其漏極與源極相同。溝道形成后,MOSFET 即可讓電流通過,器件工作于反型模式(IM)。由于柵氧化層與半導體溝道界面的不完整性,載流子受到散射,導致遷移率下降及可靠性降低。進一步地,伴隨 MOS 器件特征尺寸持續不斷地按比例縮小,基于PN結的 MOS 場效應晶體管結構弊端也越來越明顯。通常需要將一個摻雜濃度為1×1019cm-3的N 型半導體在幾納米范圍內轉變為濃度為1X1018cm-3的P型半導體,采用這樣超陡峭摻雜濃度梯度是為了避免源漏穿通造成漏電。而這樣設計的器件將嚴重限制器件工藝的熱預算。由于摻雜原子的統計分布以及在一定溫度下摻雜原子擴散的自然屬性,在納米尺度范圍內制作這樣超陡峭的 PN結變得極困難,造成晶體管閾值電壓下降,漏電嚴重,甚至無法關閉。這是未來半導體制造業難以逾越的障礙。

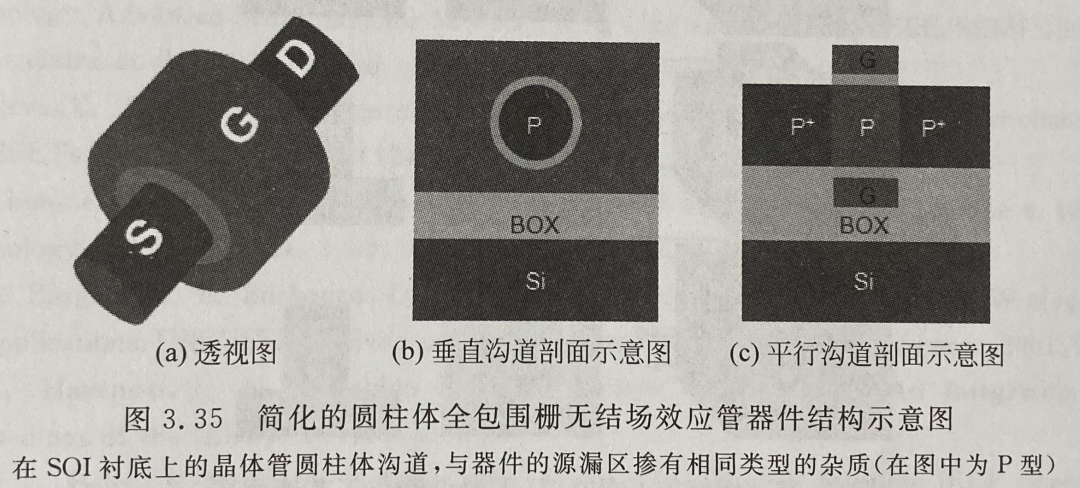

為克服由PN結所構成器件在納米尺度所面臨的障礙,2005年,中芯國際的肖德元等人首次提出一種圓柱體全包圍柵無結場效應晶體管(Gate-All-Around-Cylindrical Junctionless Field Effect Transistor, GAACJLT)及其制作方法,它屬于多數載流子導電器件。與傳統的MOSFET 不同,無結場效應晶體管(JLT)由源區、溝道、漏區,柵氧化層及柵極組成,從源區至溝道和漏區,其雜質摻雜類型相同,沒有 PN 結,屬于多數載流子導電的器件。圖3.35描繪了這種簡化了的圓柱體全包圍柵無結場效應晶體管器件的結構透視圖和沿溝道及垂直于溝道方向的器件剖面示意圖。在SOI 襯底上晶體管有一個圓柱體的單晶硅溝道,它與器件的源漏區摻雜類型相同(在圖中為P型)。絕緣體柵介質將整個圓柱體溝道包裹起來,在其上面又包裹金屬柵。導電溝道與金屬柵之間被絕緣體介質隔離,溝道內的多數載流子(空穴)在圓柱體溝道體內而非表面由源極達到漏極。通過柵極偏置電壓使器件溝道內的多數載流子累積或耗盡,可以調制溝道電導進而控制溝道電流。當柵極偏置電壓大到將圓柱體溝道靠近漏極某一截面處的空穴完全耗盡掉,在這種情況下,器件溝道電阻變成準無限大,器件處于關閉狀態。由于柵極偏置電壓可以從360°方向將圓柱體溝道空穴由表及里將其耗盡,這樣大大增強了柵極對圓柱體溝道的控制能力,有效地降低了器件的閾值電壓。由于避開了不完整的柵氧化層與半導體溝道界面,載流子受到界面散射影響有限,提高了載流子遷移率。此外,無結場效應晶體管屬于多數載流子導電器件,沿溝道方向,靠近漏極的電場強度比常規反型溝道的MOS 晶體管要來得低,器件的性能及可靠性得以大大提高。

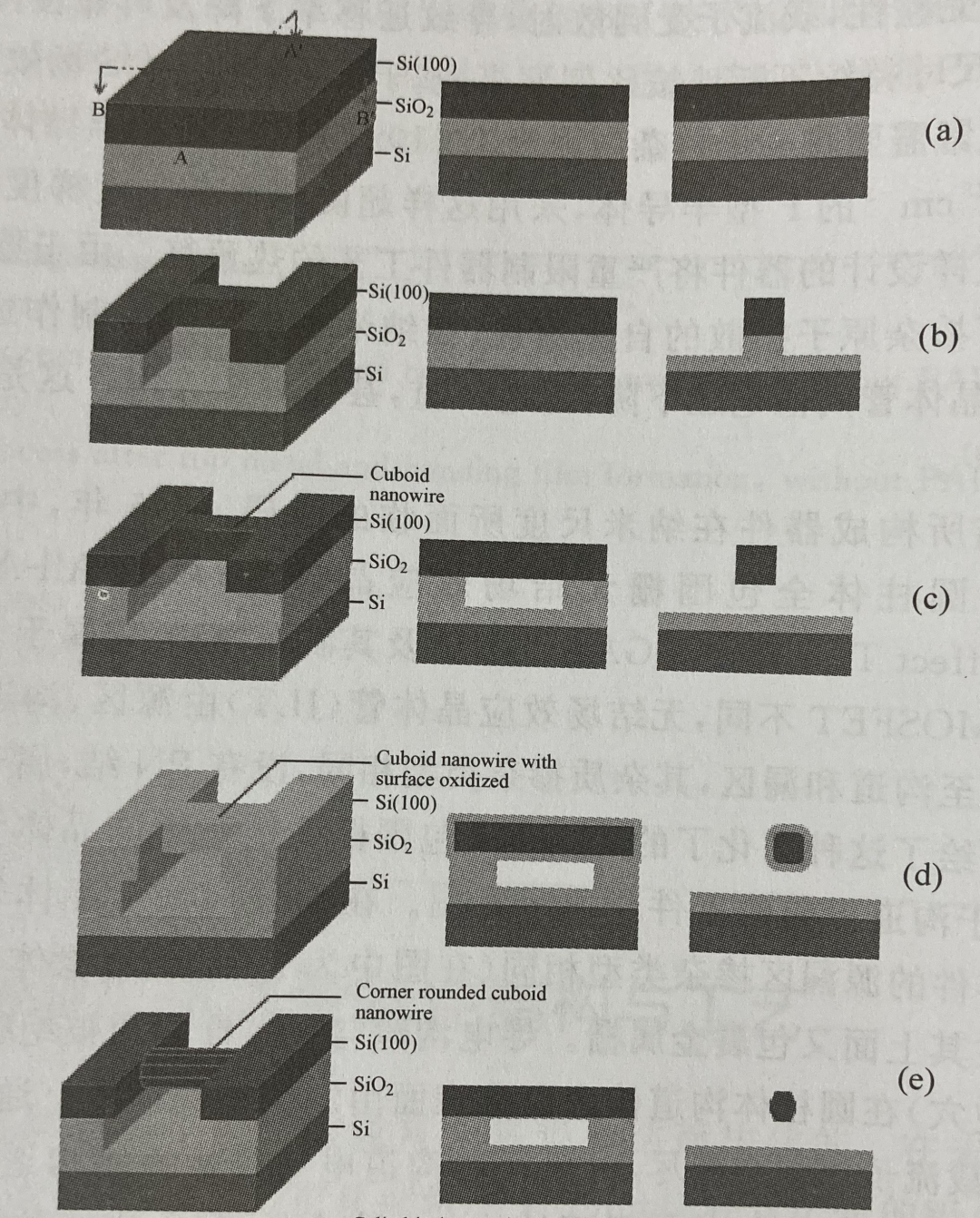

我們發展了一種柵極將圓柱體溝道全部包圍的GAAC JLT 全新制作工藝,如圖3.36所示。首先,在SOI襯底上對N型與P型溝道分別進行溝道離子注入摻雜,經光刻圖形化,刻蝕半導體硅材料層和部分埋入電介質層(BOX),形成半導體材料柱和電介質支撐柱;接下來,使用緩沖氧化物蝕刻劑(BOE)進行埋入電介質層橫向蝕刻工藝以選擇性地去除顯露的底切部分氧化物使電介質支撐柱的中段形成鏤空,形成接近立方體形狀的硅納米橋;經多次氧化與氧化物去除將其圓角化處理,最后在氫氣氛圍下進行高溫退火,形成圓柱體硅納米線橋;接下來,在襯底上沉積柵介質層及金屬層將中段鏤空處圓柱體硅納米線全部包裹;經光刻,刻蝕金屬層形成金屬柵極;形成絕緣體介質側墻結構,對圓柱體硅納米線兩端的暴露部分進行與器件溝道摻雜類型相同的離子注入重摻雜,形成源區和漏區,最后源漏區形成鎳硅化物以降低接觸電阻。

無結全包圍圓柱形溝道柵晶體管,載流子由源極流經整個圓柱體半導體溝道體內流向漏極,避開了柵氧化層與半導體溝道界面的不完整性,載流子不易受到界面散射的影響,通常其低頻噪音比傳統 MOSFET低五個數量級。在施加熱載流子應力后,器件表現出很低的ION退化,具有更高的使用壽命,這歸功于載流子流經納米線的中心以及鄰近漏極一側位置的電場峰值下降。器件具備更高的性能和可靠性以及更強的按比例縮小能力。此外,無結圓柱體全包圍柵場效應晶體管與傳統的CMOS 工藝兼容性較好且極大地簡化了器件制造工藝,適合于10nm 及以下技術節點CMOS大規模集成電路的生產制造。

-

CMOS

+關注

關注

58文章

6035瀏覽量

239148 -

MOSFET

+關注

關注

150文章

8685瀏覽量

221076 -

晶體管

+關注

關注

77文章

10029瀏覽量

142118

原文標題:無結場效應晶體管器件結構與工藝----納米集成電路制造工藝 張汝京等 編著

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

場效應晶體管

一文讓你秒懂場效應晶體管的所有參數

MOS管與場效應晶體管背后的聯系,看完后就全明白了

場效應晶體管的選用經驗分享

MOSFET和鰭式場效應晶體管的不同器件配置及其演變

什么是鰭式場效應晶體管?鰭式場效應晶體管有哪些優缺點?

什么是場效應晶體管

如何進行場效應晶體管的分類和使用

無結場效應晶體管器件結構與工藝

無結場效應晶體管器件結構與工藝

評論