結(jié)合目前應(yīng)用需求,以及前面基礎(chǔ)分析,確定IP應(yīng)具有如下特色:

(1) 通用性

前端數(shù)據(jù)采集系統(tǒng)基于 FPGA 開發(fā)。 一方面, 設(shè)備類型多, 使用的 FPGA型號各不相同, 需要實(shí)現(xiàn)的設(shè)計(jì)能夠在多種類型 FPGA 上的工作; 另一方面, 為了降部署低成本, 需要實(shí)現(xiàn)脫離 CPU 的存儲控制。 綜合考慮以上兩方面因素,設(shè)計(jì)應(yīng)采用純邏輯電路的方式實(shí)現(xiàn)。

(2) 高性能

前端采集的數(shù)據(jù)存在連續(xù)數(shù)據(jù)、 零散數(shù)據(jù)等多種數(shù)據(jù)量形式。 面臨大量零散數(shù)據(jù)存儲請求時(shí), 需要增加 NVMe I/O 隊(duì)列的數(shù)量和深度來保證數(shù)據(jù)傳輸性能; 而面臨大量連續(xù)數(shù)據(jù)存儲請求時(shí), 單隊(duì)列足以發(fā)揮性能。 在這種情況下, 需要盡可能降低功耗,減少運(yùn)行中的 I/O 隊(duì)列數(shù)量。 因此, 需要實(shí)現(xiàn)動態(tài)的隊(duì)列管理功能, 在滿足高性能的同時(shí)適應(yīng)不同的應(yīng)用環(huán)境。 具體要求為使用 PCIe3.0 以上接口的高性能固態(tài)硬盤的順序讀寫數(shù)據(jù)吞吐量不低于2GB/s, 隨機(jī)寫IOPS不低于500000, 隨機(jī)寫延遲不高于1ms。

(3) 易集成、 易操作

實(shí)現(xiàn)的 NVMe 主機(jī)控制邏輯和 NVMe 固態(tài)硬盤作為存儲子系統(tǒng), 應(yīng)能夠方便的集成到應(yīng)用環(huán)境中, 并提供簡易的操作方式實(shí)現(xiàn)數(shù)據(jù)的傳輸與存儲。 因此, 設(shè)計(jì)需要采用標(biāo)準(zhǔn)化接口, 實(shí)現(xiàn)盡可能低的資源占用率, 并具備 DMA 數(shù)據(jù)傳輸功能。

基于以上需求, 本IP擬基于 FPGA 的 NVMe over PCIe(NoP) 邏輯進(jìn)行設(shè)計(jì),它具有以下特點(diǎn):

(1) 支持 NVMe 1.3d 協(xié)議、 支持 PCIe 3.0 協(xié)議。

(2) 基于 Xilinx PCIe Integration Block 硬核開發(fā)。 一方面, 該 PCIE 集成塊具有多種版本, 并且適用平臺多, 因此 NoP 邏輯加速引擎能夠部署在支持 PCIE 集成塊的FPGA 開發(fā)板上。 另一方面, 直接對接 PCIE 集成塊的結(jié)構(gòu)設(shè)計(jì)具有更高的數(shù)據(jù)傳輸性能。

(3) 純邏輯電路開發(fā)。 設(shè)計(jì)基于純邏輯電路, 不需要 CPU 的介入, 獨(dú)立運(yùn)行,可以節(jié)省 CPU 資源, 兼容 SoC 與純邏輯環(huán)境。

(4) 使用 AXI 總線接口。 設(shè)計(jì)使用標(biāo)準(zhǔn)化的 AXI 總線接口提供系統(tǒng)控制和數(shù)據(jù)傳輸功能, 在保證了傳輸性能的同時(shí), 更容易集成到應(yīng)用環(huán)境中。

(5) 多隊(duì)列并行管理與動態(tài)配置。 支持的最大 I/O 提交隊(duì)列數(shù)量為 16, 支持的最大單 I/O 提交隊(duì)列深度為 1024, 最大 I/O 提交隊(duì)列總深度為 1024, 支持運(yùn)行過程中動態(tài)的創(chuàng)建或刪除隊(duì)列。

(6) DMA 功能。 通過配置 DMA 寄存器直接請求數(shù)據(jù)傳輸, 數(shù)據(jù)傳輸通過 AXI4總線接口對接用戶邏輯, 使用突發(fā)傳輸提高數(shù)據(jù)傳輸性能。

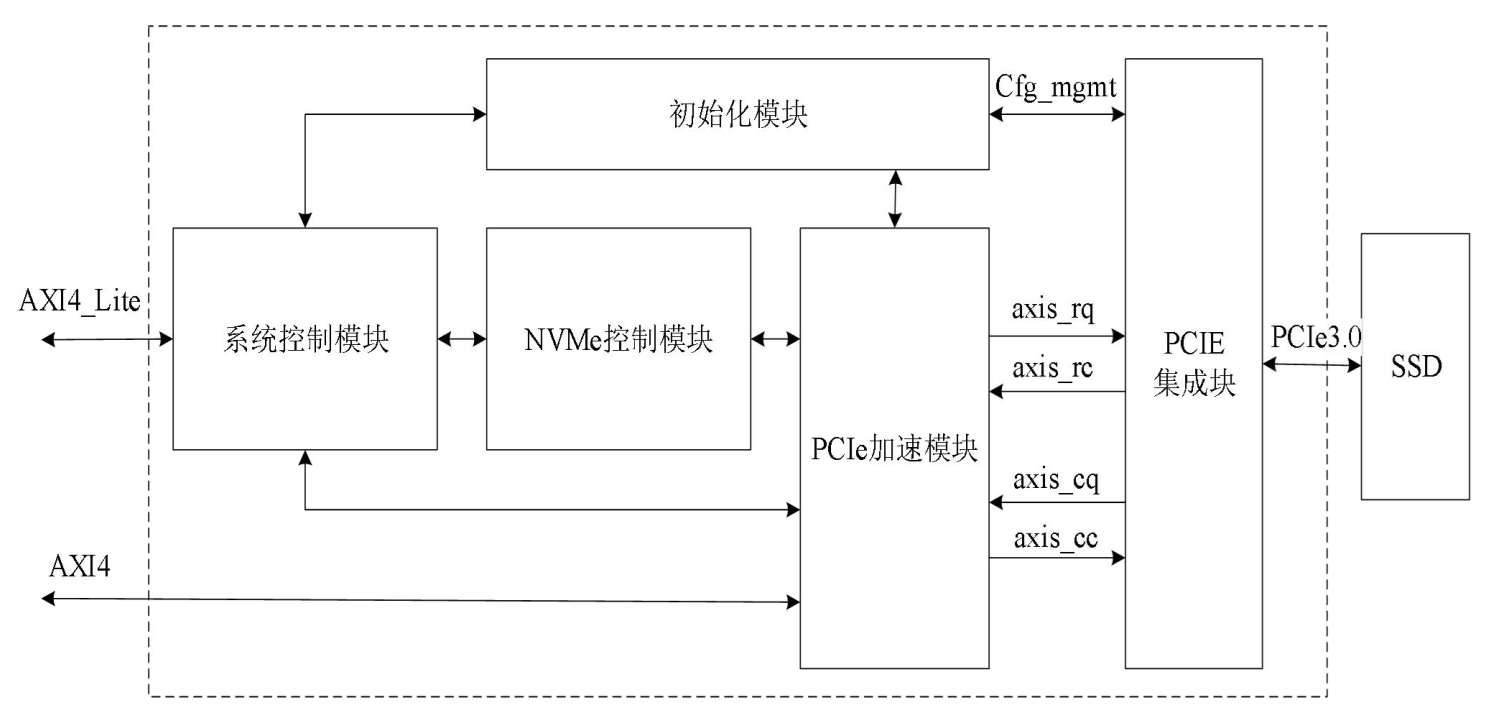

圖1 Nvme邏 輯加速IP系統(tǒng)架構(gòu)圖

新系統(tǒng)中,Nvme邏輯加速IP通過 PCIe 3.0x4 接口連接 NVMe

固態(tài)硬盤, 并提供 AXI4-Lite 接口用于系統(tǒng)控制, 以及 AXI4 接口用于數(shù)據(jù)傳輸。 在該IP內(nèi)部, 根據(jù)功能劃分為系統(tǒng)控制模塊、 初始化模塊、 NVMe 控制模塊、 PCIe 加速模塊、 PCIE 集成塊。 以下為各功能模塊的定義:

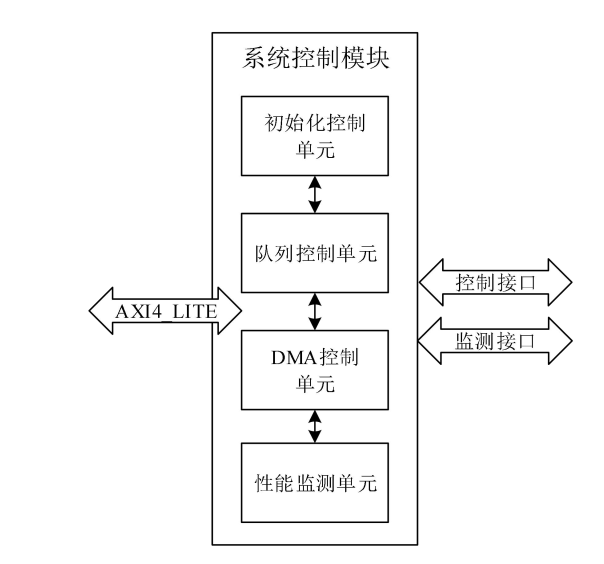

系統(tǒng)控制模塊是實(shí)現(xiàn)NVMe over PCIe關(guān)鍵組件。 NoP 邏輯加速引擎內(nèi)部集成了各種功能, 包括初始化、 NVMe 隊(duì)列管理以及 DMA 等多種功能, 統(tǒng)由系統(tǒng)控制模塊進(jìn)行管理。 為了有效管理這些功能, 系統(tǒng)控制模塊設(shè)計(jì)了對應(yīng)的功能控制單元, 并提供了 AXI4-Lite 從機(jī)接口, 使得 NoP 邏輯加速引擎能夠輕松地與用戶環(huán)境集成。 通過 AXI4-Lite 接口, 用戶可以方便地訪問各個(gè)功能控制單元, 實(shí)現(xiàn)對系統(tǒng)功能的控制。 這種設(shè)計(jì)使得用戶能夠直接與 NoP 邏輯加速引擎進(jìn)行交互, 靈活地配置和管理系統(tǒng)的各項(xiàng)功能, 從而更好地滿足特定的應(yīng)用需求。

初始化模塊負(fù)責(zé)控制系統(tǒng)的初始化流程, 其中包括 PCIe 初始化和 NVMe 初始化兩個(gè)主要步驟。 在系統(tǒng)上電復(fù)位后, 首先由 PCIE 集成塊執(zhí)行物理層的鏈路訓(xùn)練和速度協(xié)商, 建立有效的 PCIe 通信鏈路。 隨后, 由初始化模塊進(jìn)行 PCIe 設(shè)備的枚舉與配置, 并執(zhí)行 NVMe 的初始化流程。 初始化過程是確保系統(tǒng)能夠在正確狀態(tài)下運(yùn)行的前提條件, 也為后續(xù)操作提供了必要的支持。

NVMe 控制模塊是實(shí)現(xiàn) NVMe 的命令提交和完成機(jī)制的核心模塊。 首先, 該模塊負(fù)責(zé)將來自系統(tǒng)控制模塊的功能請求轉(zhuǎn)換為 NVMe 命令請求, 并執(zhí)行 NVMe 指令提交與完成機(jī)制。 其次, 該模塊實(shí)現(xiàn) NVMe 隊(duì)列管理功能, 除了基本的隊(duì)列存儲、門鈴控制、 請求仲裁、 條目解析等, 還包括了動態(tài)創(chuàng)建和刪除隊(duì)列功能。 最后, 該模塊還負(fù)責(zé)實(shí)現(xiàn) PRP 尋址機(jī)制, 根據(jù)指令管理和計(jì)算 PRP 偏移, 實(shí)現(xiàn)數(shù)據(jù)的尋址并降低 PRP 讀取延遲。

PCIe 加速模塊負(fù)責(zé)處理 PCIe TLP, 將 PCIe 事務(wù)與 NVMe 緊密結(jié)合。 一方面,該模塊將來自初始化模塊或 NVMe 控制模塊的事務(wù)請求轉(zhuǎn)換為 PCIe TLP 請求, 然后發(fā)送到 PCIE 集成塊, 同時(shí)接收 PCIE 集成塊的 TLP 響應(yīng)包, 將其轉(zhuǎn)換為內(nèi)部事務(wù)響應(yīng)發(fā)送到對應(yīng)內(nèi)部模塊。 另一方面, 該模塊負(fù)責(zé)處理來自 NVMe 存儲設(shè)備的 TLP 請求, 根據(jù)請求內(nèi)容將請求轉(zhuǎn)發(fā)到 NVMe 控制模塊或轉(zhuǎn)換為 AXI4 總線事務(wù), 同時(shí)將來自 NVMe 控制模塊和 AXI4 總的響應(yīng)組裝為 CplD, 經(jīng)由 PCIE 集成塊發(fā)送給 NVMe存儲設(shè)備。

PCIE 集成塊實(shí)現(xiàn) PCIe 的數(shù)據(jù)鏈路層和物理層。 PCIE 集成塊是 Xilinx 提供的用于 PCIe 的高帶寬、 可擴(kuò)展和靈活的通用 I/O 核, 在 NoP 邏輯加速引擎中使用 PCIE集成塊的 RC 模式實(shí)現(xiàn) Root Complex 的數(shù)據(jù)鏈路層與物理層。 PCIE 集成塊提供了四組 AXI stream 接口用于傳遞 PCIe TLP, 通過這些接口實(shí)現(xiàn) TLP 與 PCIe 鏈路信號的相互轉(zhuǎn)換, 此外還包含一組配置接口用于訪問 PCIE 集成塊的配置空間。

想進(jìn)一步了解相關(guān)視頻,請搜索B站用戶:專注與守望

鏈接:https://space.bilibili.com/585132944/dynamic?spm_id_from=333.1365.list.card_title.click

更多博文見:https://blog.csdn.net/tiantianuser/article/details/148994728

-

FPGA

+關(guān)注

關(guān)注

1645文章

22012瀏覽量

616668 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

525瀏覽量

44665 -

高速存儲

+關(guān)注

關(guān)注

0文章

8瀏覽量

5996 -

nvme

+關(guān)注

關(guān)注

0文章

246瀏覽量

23180

發(fā)布評論請先 登錄

NVMe IP高速傳輸卻不依賴便利的XDMA設(shè)計(jì)之三:系統(tǒng)架構(gòu)

NVMe IP高速傳輸擺脫XDMA設(shè)計(jì)之四:系統(tǒng)控制模塊設(shè)計(jì)

PCIE高速傳輸解決方案FPGA技術(shù)XILINX官方XDMA驅(qū)動

據(jù)調(diào)查64%的人表示:日常生活中不依賴物聯(lián)網(wǎng)設(shè)備

PHP簡單實(shí)現(xiàn)不依賴于Unix系統(tǒng)Cron的定時(shí)任務(wù)程序資料說明

以色列成立新研究中心,開發(fā)不依賴GPS的導(dǎo)航系統(tǒng)

智行者發(fā)布國內(nèi)首款不依賴高精地圖的高級別自動駕駛解決方案

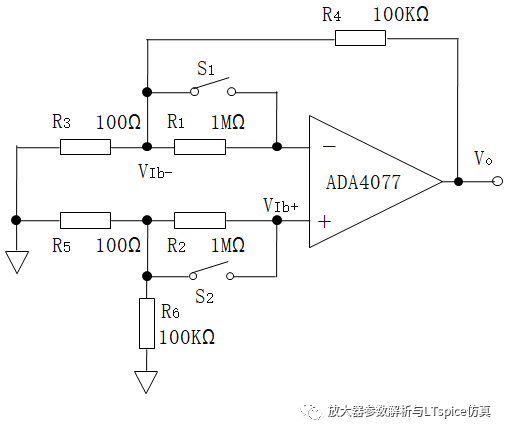

一個(gè)種不依賴昂貴檢測設(shè)備的偏置電流測試方法

原生鴻蒙系統(tǒng)正式發(fā)布,余承東宣布不依賴國外核心技術(shù)

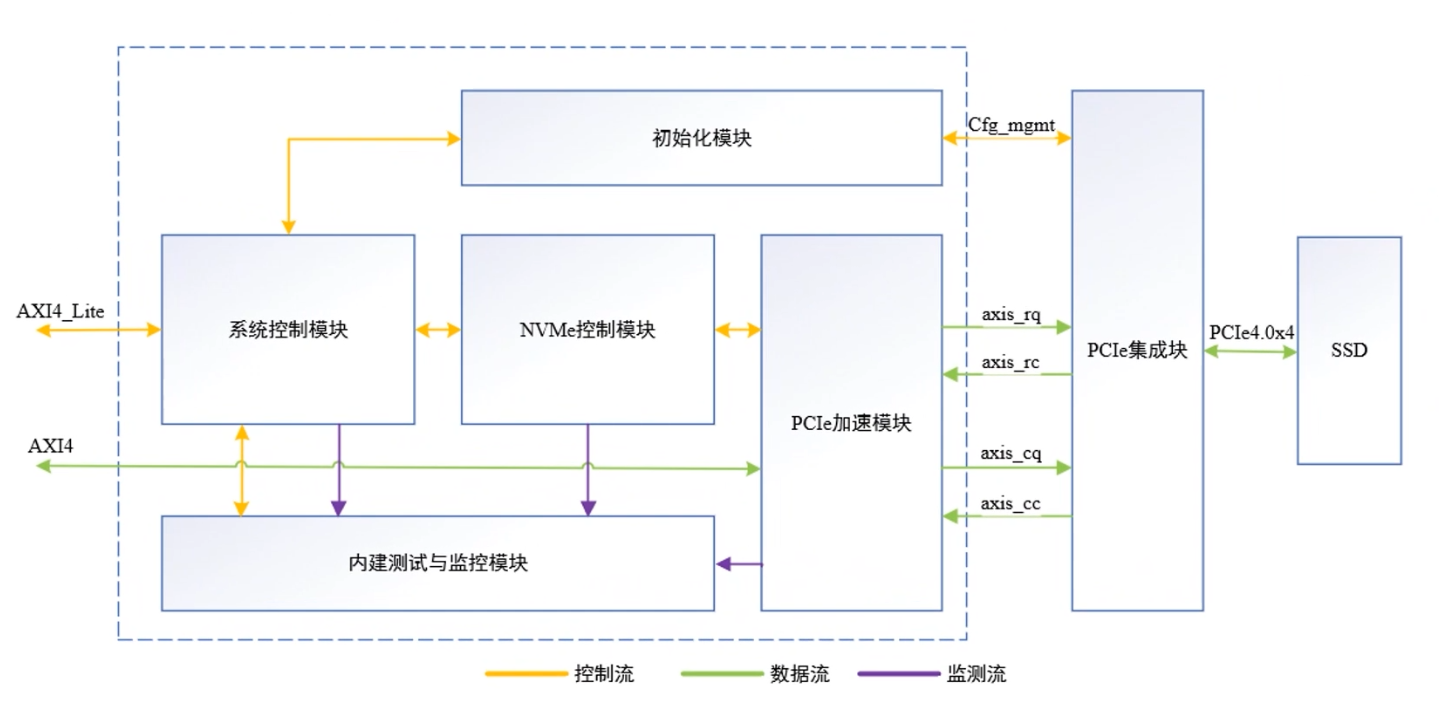

NVMe IP over PCIe 4.0:擺脫XDMA,實(shí)現(xiàn)超高速!

NVMe IP高速傳輸卻不依賴XDMA設(shè)計(jì)之二:PCIe讀寫邏輯

NVMe IP高速傳輸卻不依賴XDMA設(shè)計(jì)之四:系統(tǒng)控制模塊

NVMe IP高速傳輸卻不依賴XDMA設(shè)計(jì)之三:系統(tǒng)架構(gòu)

NVMe IP高速傳輸卻不依賴XDMA設(shè)計(jì)之三:系統(tǒng)架構(gòu)

評論