單芯片解決方案,開啟全新體驗(yàn)——W55MH32高性能以太網(wǎng)單片機(jī)

W55MH32是WIZnet重磅推出的高性能以太網(wǎng)單片機(jī),它為用戶帶來前所未有的集成化體驗(yàn)。這顆芯片將強(qiáng)大的組件集于一身,具體來說,一顆W55MH32內(nèi)置高性能Arm? Cortex-M3核心,其主頻最高可達(dá)216MHz;配備1024KB FLASH與96KB SRAM,滿足存儲與數(shù)據(jù)處理需求;集成TOE引擎,包含WIZnet全硬件TCP/IP協(xié)議棧、內(nèi)置MAC以及PHY,擁有獨(dú)立的32KB以太網(wǎng)收發(fā)緩存,可供8個(gè)獨(dú)立硬件socket使用。如此配置,真正實(shí)現(xiàn)了All-in-One解決方案,為開發(fā)者提供極大便利。

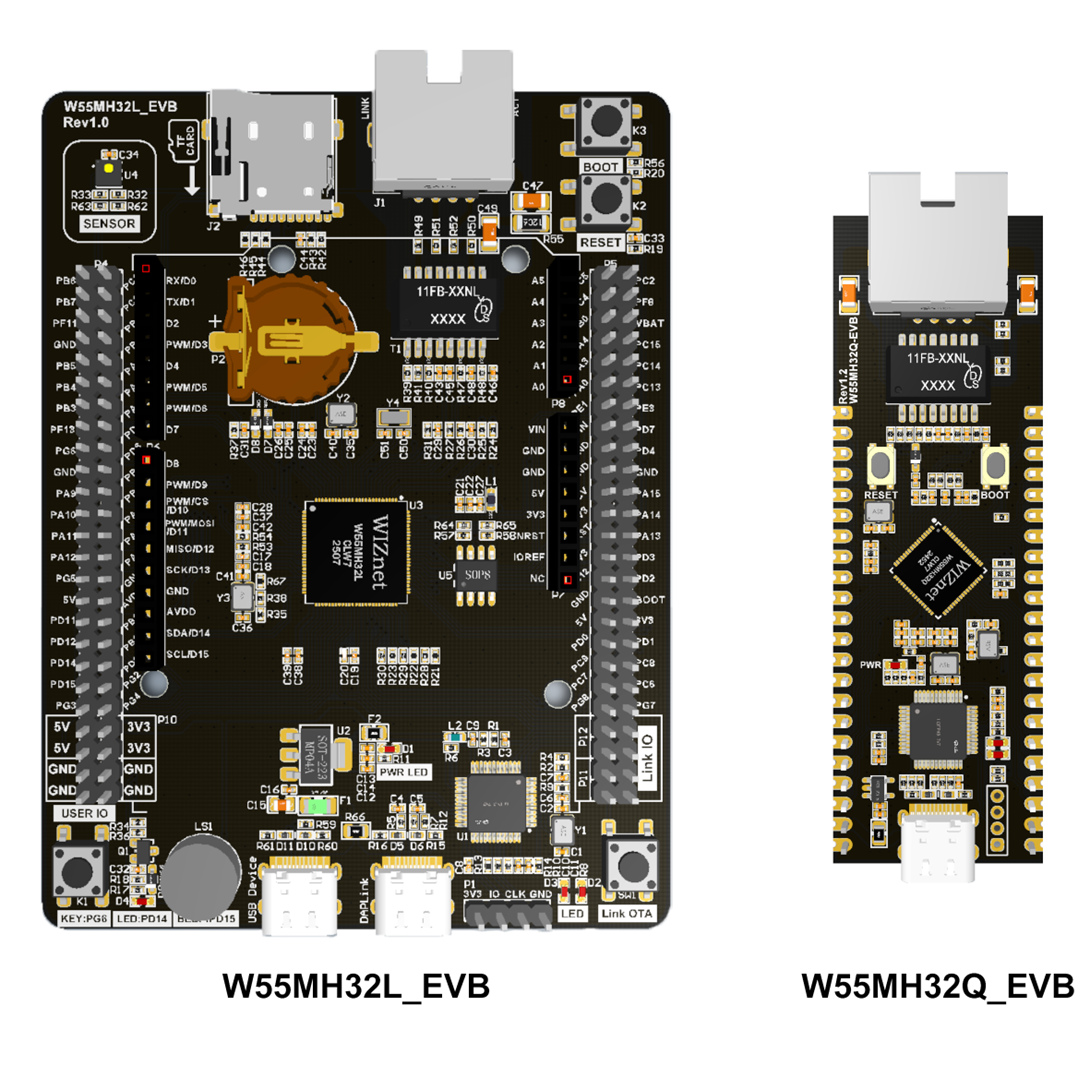

在封裝規(guī)格上,W55MH32提供了兩種選擇:QFN100和QFN68。

W55MH32L采用QFN100封裝版本,尺寸為12x12mm,其資源豐富,專為各種復(fù)雜工控場景設(shè)計(jì)。它擁有66個(gè)GPIO、3個(gè)ADC、12通道DMA、17個(gè)定時(shí)器、2個(gè)I2C、5個(gè)串口、2個(gè)SPI接口(其中1個(gè)帶I2S接口復(fù)用)、1個(gè)CAN、1個(gè)USB2.0以及1個(gè)SDIO接口。如此豐富的外設(shè)資源,能夠輕松應(yīng)對工業(yè)控制中多樣化的連接需求,無論是與各類傳感器、執(zhí)行器的通信,還是對復(fù)雜工業(yè)協(xié)議的支持,都能游刃有余,成為復(fù)雜工控領(lǐng)域的理想選擇。同系列還有QFN68封裝的W55MH32Q版本,該版本體積更小,僅為8x8mm,成本低,適合集成度高的網(wǎng)關(guān)模組等場景,軟件使用方法一致。更多信息和資料請進(jìn)入http://www.w5500.com/網(wǎng)站或者私信獲取。

此外,本W(wǎng)55MH32支持硬件加密算法單元,WIZnet還推出TOE+SSL應(yīng)用,涵蓋TCP SSL、HTTP SSL以及 MQTT SSL等,為網(wǎng)絡(luò)通信安全再添保障。

為助力開發(fā)者快速上手與深入開發(fā),基于W55MH32L這顆芯片,WIZnet精心打造了配套開發(fā)板。開發(fā)板集成WIZ-Link芯片,借助一根USB C口數(shù)據(jù)線,就能輕松實(shí)現(xiàn)調(diào)試、下載以及串口打印日志等功能。開發(fā)板將所有外設(shè)全部引出,拓展功能也大幅提升,便于開發(fā)者全面評估芯片性能。

若您想獲取芯片和開發(fā)板的更多詳細(xì)信息,包括產(chǎn)品特性、技術(shù)參數(shù)以及價(jià)格等,歡迎訪問官方網(wǎng)頁:http://www.w5500.com/,我們期待與您共同探索W55MH32的無限可能。

第三十二章 MPU——內(nèi)存保護(hù)單元

MPU(Memory Protection Unit,內(nèi)存保護(hù)單元)是W55MH32中用于管理內(nèi)存區(qū)域訪問權(quán)限與屬性的關(guān)鍵模塊。它通過劃分內(nèi)存區(qū)域并設(shè)置訪問規(guī)則(如讀/寫/執(zhí)行權(quán)限、緩存策略),增強(qiáng)系統(tǒng)的安全性和穩(wěn)定性,尤其適用于多任務(wù)系統(tǒng)(如RTOS)或需要隔離關(guān)鍵資源的場景。

1MPU功能概述

1.1基本概念

MPU是W55MH32內(nèi)置的硬件模塊,不支持虛擬內(nèi)存(與MMU不同),但能通過物理內(nèi)存區(qū)域劃分實(shí)現(xiàn)以下功能:

限制任務(wù)/程序?qū)μ囟▋?nèi)存區(qū)域的訪問(如禁止寫、禁止執(zhí)行)。

定義內(nèi)存區(qū)域的屬性(如緩存策略、共享性),優(yōu)化系統(tǒng)性能。

檢測非法內(nèi)存訪問(如越界、權(quán)限違規(guī)),觸發(fā)異常(如 MemManage Fault),避免系統(tǒng)崩潰。

1.2關(guān)鍵術(shù)語

內(nèi)存區(qū)域(Region):MPU將內(nèi)存劃分為多個(gè)獨(dú)立區(qū)域,每個(gè)區(qū)域需配置基地址、大小、權(quán)限等參數(shù)。

訪問權(quán)限(Access Permission):定義區(qū)域的讀(R)、寫(W)、執(zhí)行(X)權(quán)限(如僅讀、可讀可寫、不可執(zhí)行)。

內(nèi)存屬性(Memory Attribute):包括緩存策略(如無緩存、寫通、寫回)、共享性(是否被多處理器共享)等,影響數(shù)據(jù)訪問效率。

2MPU核心功能

2.1內(nèi)存區(qū)域劃分

MPU通過配置區(qū)域基地址(Base Address)和區(qū)域大小(Size),將物理內(nèi)存劃分為多個(gè)獨(dú)立區(qū)域。

大小限制:區(qū)域大小必須是2的冪次(如32B、64B、1KB、64KB等),且基地址需對齊到區(qū)域大小(例如 64KB區(qū)域的基地址必須是 64KB的整數(shù)倍)。

區(qū)域重疊:若多個(gè)區(qū)域重疊,編號大的區(qū)域優(yōu)先級更高(覆蓋小編號區(qū)域的配置)。

2.2訪問權(quán)限控制

每個(gè)區(qū)域可獨(dú)立設(shè)置特權(quán)級(Privileged)和用戶級(Unprivileged)的訪問權(quán)限(如 RTOS中內(nèi)核運(yùn)行在特權(quán)級,任務(wù)運(yùn)行在用戶級)。常見權(quán)限組合如下:

| 權(quán)限類型 | 說明 |

| PRIV_RW | 特權(quán)級可讀可寫,用戶級無權(quán)限 |

| PRIV_RW_USER_RO | 特權(quán)級可讀可寫,用戶級僅可讀 |

| PRIV_RO | 特權(quán)級僅可讀,用戶級無權(quán)限 |

| NO_ACCESS | 任何級別均不可訪問(用于標(biāo)記非法區(qū)域) |

2.3內(nèi)存屬性配置

通過設(shè)置內(nèi)存類型(Memory Type)和緩存策略(Cache Policy),優(yōu)化數(shù)據(jù)訪問效率:

內(nèi)存類型:如普通內(nèi)存(Normal)、設(shè)備內(nèi)存(Device)。

普通內(nèi)存:支持緩存(如SRAM中的變量)。

設(shè)備內(nèi)存:通常為外設(shè)寄存器(如 GPIO、UART),需禁用緩存(避免緩存導(dǎo)致的讀寫延遲)。

緩存策略:

無緩存(Non-Cacheable):直接訪問物理內(nèi)存(如設(shè)備寄存器)。

寫通(Write-Through):寫數(shù)據(jù)時(shí)同時(shí)更新緩存和內(nèi)存(適合需要實(shí)時(shí)性的場景)。

寫回(Write-Back):寫數(shù)據(jù)時(shí)僅更新緩存,后續(xù)統(tǒng)一寫入內(nèi)存(適合高頻讀寫場景,提升效率)。

3應(yīng)用場景

MPU的核心價(jià)值在于內(nèi)存安全防護(hù)和資源隔離,以下是其典型應(yīng)用場景,結(jié)合核心功能說明其實(shí)際意義:

RTOS任務(wù)隔離(多任務(wù)系統(tǒng)核心需求):在RTOS(實(shí)時(shí)操作系統(tǒng))中,多個(gè)任務(wù)共享同一內(nèi)存空間,若未隔離可能因任務(wù)異常(如棧溢出、野指針)導(dǎo)致系統(tǒng)崩潰。MPU通過區(qū)域劃分與權(quán)限控制實(shí)現(xiàn)任務(wù)隔離。

關(guān)鍵數(shù)據(jù)/代碼保護(hù)(防篡改與誤操作):系統(tǒng)中某些數(shù)據(jù)或代碼(如固件、校準(zhǔn)參數(shù)、加密密鑰)一旦被修改,可能導(dǎo)致功能失效或安全漏洞。MPU通過只讀或禁止訪問權(quán)限保護(hù)這些資源。

外設(shè)寄存器訪問控制(防止誤操作外設(shè)):外設(shè)寄存器(如GPIO、UART的控制寄存器)的錯誤修改可能導(dǎo)致外設(shè)異常。MPU限制僅特權(quán)級代碼(如內(nèi)核)可修改關(guān)鍵寄存器。

內(nèi)存越界檢測(開發(fā)調(diào)試輔助):開發(fā)階段,程序可能因數(shù)組越界、野指針等錯誤訪問未分配內(nèi)存。MPU將未使用的內(nèi)存區(qū)域配置為NO_ACCESS(無訪問權(quán)限),觸發(fā)異常以快速定位問題。

安全啟動與固件保護(hù)(系統(tǒng)級安全需求):在需要安全啟動的系統(tǒng)中(如醫(yī)療設(shè)備、工業(yè)控制),MPU保護(hù)啟動代碼和安全配置區(qū)域,確保系統(tǒng)從可信代碼啟動。

4注意事項(xiàng)

引腳驅(qū)動能力:MCO輸出頻率不宜過高(需低于GPIO的最大可靠頻率,通常建議不超過50MHz),高頻時(shí)需考慮信號完整性(如阻抗匹配)。

時(shí)鐘源使能順序:配置MCO前需確保時(shí)鐘源已穩(wěn)定(如HSE起振完成),避免輸出無效信號。

5程序設(shè)計(jì)

MPU的核心配置通過RASR(Region Attribute and Size Register,區(qū)域?qū)傩耘c大小寄存器)實(shí)現(xiàn),具體配置步驟如下:

5.1內(nèi)存區(qū)域大小宏(SIZE字段)

#define MPU_DEFS_RASR_SIZE_1KB (0x09

作用:設(shè)置內(nèi)存區(qū)域的大小。

原理:RASR的SIZE字段(位 [5:0])用于定義區(qū)域大小,實(shí)際大小為2(SIZE+1)字節(jié)。

0x09對應(yīng)SIZE=9,計(jì)算得210=1024字節(jié)(1KB);

0x0D對應(yīng)SIZE=13,計(jì)算得214=16384字節(jié)(16KB);

0x0F對應(yīng)SIZE=15,計(jì)算得216=65536字節(jié)(64KB)。

5.2內(nèi)存類型與緩存策略宏(C和S字段)

#define MPU_DEFS_NORMAL_MEMORY_WT (MPU_RASR_C_Msk| MPU_RASR_S_Msk)

作用:定義普通內(nèi)存的直寫(Write-Through, WT)緩存策略。

原理:

C_Msk(位 [16]):使能緩存(Cacheable);

S_Msk(位 [18]):標(biāo)記為共享內(nèi)存(Sharable),用于多主設(shè)備(如 CPU與 DMA)訪問時(shí)的一致性;

組合后表示“可緩存、共享的直寫內(nèi)存”(寫操作直接更新內(nèi)存,不經(jīng)過緩存)。

5.3訪問權(quán)限宏(AP字段)

#define MPU_DEFS_RASE_AP_FULL_ACCESS (0x3

作用:設(shè)置內(nèi)存區(qū)域的完全訪問權(quán)限(無限制)。

原理:RASR的AP字段(位 [23:21])定義訪問權(quán)限,0x3表示:

特權(quán)模式(Privileged)允許讀/寫;

用戶模式(User)允許讀/寫(無限制訪問)。

5.4設(shè)置內(nèi)存保護(hù)規(guī)則

內(nèi)存保護(hù)規(guī)則由MPU_Set()函數(shù)實(shí)現(xiàn),函數(shù)內(nèi)容如下:

{ SCB->SHCSR|= SCB_SHCSR_MEMFAULTENA_Msk; mpu_disable(); mpu_region_config(0,0x8000000, MPU_DEFS_RASR_SIZE_64KB, MPU_DEFS_NORMAL_MEMORY_WT | MPU_DEFS_RASE_AP_FULL_ACCESS| MPU_RASR_ENABLE_Msk); mpu_region_config(1,0x20000000, MPU_DEFS_RASR_SIZE_16KB, MPU_DEFS_NORMAL_MEMORY_WT | MPU_DEFS_RASE_AP_FULL_ACCESS| MPU_RASR_ENABLE_Msk); mpu_region_config(2, USART1_BASE, MPU_DEFS_RASR_SIZE_1KB, MPU_DEFS_NORMAL_MEMORY_WT | MPU_DEFS_RASE_AP_FULL_ACCESS| MPU_RASR_ENABLE_Msk); mpu_region_disable(3); mpu_region_disable(4); mpu_region_disable(5); mpu_region_disable(6); mpu_region_disable(7); mpu_enable(); }

該函數(shù)首先使能了內(nèi)存錯誤(MemFault)異常,以便檢測非法內(nèi)存訪問;隨后禁用MPU(配置前需禁用以避免沖突),依次配置3個(gè)內(nèi)存區(qū)域:

區(qū)域0(起始地址0x8000000,64KB,對應(yīng)Flash)

區(qū)域1(起始地址0x20000000,16KB,對應(yīng)RAM)

區(qū)域2(起始地址USART1_BASE,1KB,對應(yīng)串口1外設(shè)寄存器)

這3個(gè)區(qū)域均設(shè)置為“直寫緩存+完全訪問權(quán)限”并啟用;接著禁用未使用的區(qū)域3~7(MPU通常支持8個(gè)區(qū)域,未使用的需禁用以防意外訪問);最后啟用MPU,使所有配置的內(nèi)存保護(hù)規(guī)則生效,確保Flash、RAM及串口外設(shè)的訪問受限于預(yù)設(shè)的大小、權(quán)限和緩存策略,提升系統(tǒng)內(nèi)存訪問的安全性與穩(wěn)定性。

5.5主函數(shù)main()

主函數(shù)main()的內(nèi)容如下:

int main(void) { RCC_ClocksTypeDef clocks; delay_init(); UART_Configuration(115200); RCC_GetClocksFreq(&clocks); printf("n"); printf("SYSCLK: %3.1fMhz, HCLK: %3.1fMhz, PCLK1: %3.1fMhz, PCLK2: %3.1fMhz, ADCCLK: %3.1fMhzn", (float)clocks.SYSCLK_Frequency /1000000,(float)clocks.HCLK_Frequency/1000000, (float)clocks.PCLK1_Frequency /1000000,(float)clocks.PCLK2_Frequency/1000000,(float)clocks.ADCCLK_Frequency/1000000); printf("MPU Test.n"); printf("MPU->TYPE, Value: 0x%xn", MPU->TYPE); printf("MPU->CTRL, Value: 0x%xn", MPU->CTRL); printf("MPU->RNR, Value: 0x%xn", MPU->RNR); printf("MPU->RBAR, Value: 0x%xn", MPU->RBAR); printf("MPU->RASR, Value: 0x%xn", MPU->RASR); printf("MPU->RBAR_A1;, Value: 0x%xn", MPU->RBAR_A1); printf("MPU->RASR_A1, Value: 0x%xn", MPU->RASR_A1); printf("MPU->RBAR_A2, Value: 0x%xn", MPU->RBAR_A2); printf("MPU->RASR_A2, Value: 0x%xn", MPU->RASR_A2); printf("MPU->RBAR_A3, Value: 0x%xn", MPU->RBAR_A3); printf("MPU->RASR_A3, Value: 0x%xnn", MPU->RASR_A3); printf("LimiteToPrivilege Accessn"); SHOW_PrintFlash(0x08000000,64); MPU_Set(); printf("LimiteToUser Accessn"); SHOW_PrintFlash(0x08000000,64); while(1); }

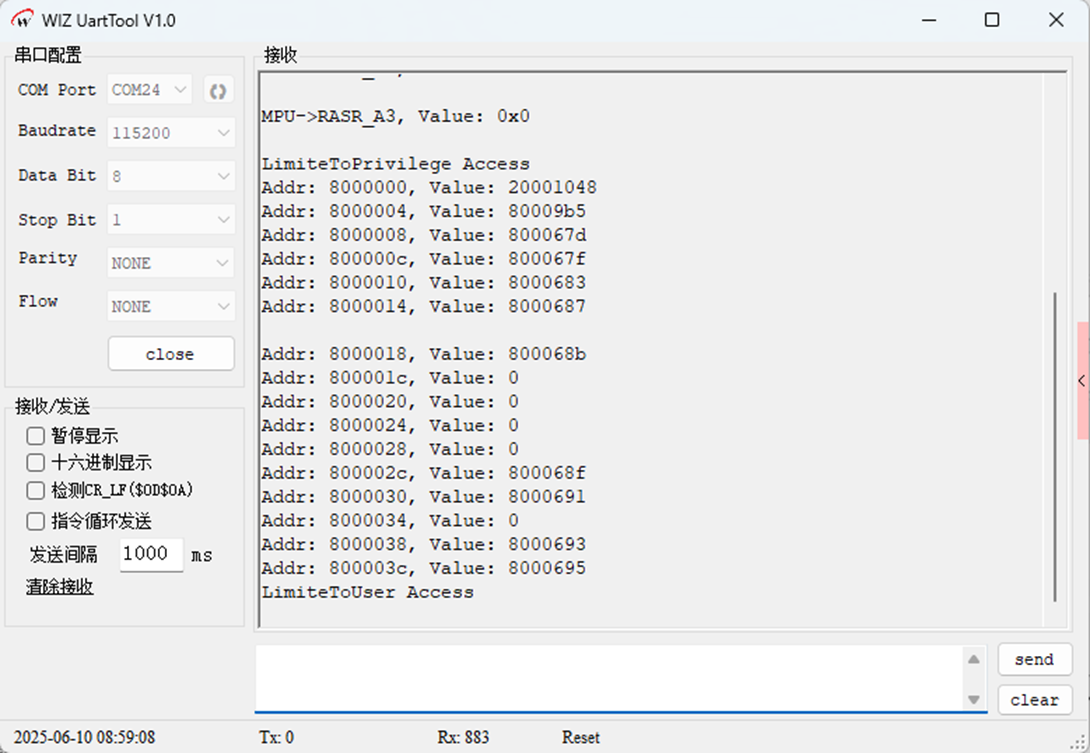

main()函數(shù)是MPU功能測試的主程序:首先初始化延時(shí)函數(shù)和串口(波特率115200),調(diào)用標(biāo)準(zhǔn)庫獲取系統(tǒng)各時(shí)鐘域頻率(SYSCLK、HCLK等)并打印;接著打印MPU核心寄存器(TYPE、CTRL等)的初始狀態(tài)用于調(diào)試;

隨后調(diào)用MPU_Set配置內(nèi)存保護(hù)規(guī)則,對比配置前后對Flash起始地址(0x08000000)前64字節(jié)的訪問結(jié)果(特權(quán)模式與用戶模式),驗(yàn)證MPU對內(nèi)存訪問權(quán)限的限制效果;最后進(jìn)入無限循環(huán)保持運(yùn)行。

6下載驗(yàn)證

程序下載運(yùn)行之后,首先打印了時(shí)鐘信息,接著是MPU的相關(guān)寄存器初始狀態(tài)信息,然后用特權(quán)限制訪問內(nèi)存成功,之后設(shè)置為用戶訪問,再次訪問則無法讀取內(nèi)容:

7總結(jié)

MCO功能通過靈活配置時(shí)鐘源和分頻系數(shù),為W55MH32提供了對外輸出時(shí)鐘的能力,簡化了系統(tǒng)設(shè)計(jì)中的時(shí)鐘同步問題。先理解其應(yīng)用場景(如多芯片同步、調(diào)試測量),再掌握配置步驟(時(shí)鐘源選擇、GPIO設(shè)置、分頻配置),可更高效地應(yīng)用于實(shí)際項(xiàng)目中。

WIZnet是一家無晶圓廠半導(dǎo)體公司,成立于1998年。產(chǎn)品包括互聯(lián)網(wǎng)處理器iMCU?,它采用TOE(TCP/IP卸載引擎)技術(shù),基于獨(dú)特的專利全硬連線TCP/IP。iMCU?面向各種應(yīng)用中的嵌入式互聯(lián)網(wǎng)設(shè)備。

WIZnet在全球擁有70多家分銷商,在香港、韓國、美國設(shè)有辦事處,提供技術(shù)支持和產(chǎn)品營銷。

香港辦事處管理的區(qū)域包括:澳大利亞、印度、土耳其、亞洲(韓國和日本除外)。

審核編輯 黃宇

-

單片機(jī)

+關(guān)注

關(guān)注

6067文章

44967瀏覽量

649085 -

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5615瀏覽量

175425 -

封裝

+關(guān)注

關(guān)注

128文章

8625瀏覽量

145179 -

WIZnet

+關(guān)注

關(guān)注

3文章

20瀏覽量

42422 -

MPU

+關(guān)注

關(guān)注

0文章

412瀏覽量

49804

發(fā)布評論請先 登錄

第二十二章 TIM——高級定時(shí)器

RK3568驅(qū)動指南|第十二篇 GPIO子系統(tǒng)-第130章 GPIO的調(diào)試方法

RK3568驅(qū)動指南|第十二篇 GPIO子系統(tǒng)-第135章 GPIO子系統(tǒng)與pinctrl子系統(tǒng)相結(jié)合實(shí)驗(yàn)

第十二章 SysTick——系統(tǒng)定時(shí)器

如何優(yōu)化MPU的能耗

MPU的性能評估方法

MPU與數(shù)字信號處理的關(guān)系

MPU與MCU的區(qū)別

MPU微處理器的工作原理

首頁-2025年第三十二屆上海國際電力設(shè)備及技術(shù)展覽會 EP Shanghai

第三十二章 MPU——內(nèi)存保護(hù)單元

第三十二章 MPU——內(nèi)存保護(hù)單元

評論